The Effect of CNR Capacitor and CFF Capacitor in TPL910

# The Effect of CNR Capacitor and CFF Capacitor in TPL910

The TPL910 series of products are 1-A highcurrent, 4.5- $\mu$ V<sub>RMS</sub> low-noise, high-PSRR, highaccuracy linear regulators with only maximum 500-mV ultra-low dropout voltage at 1-A load current. The TPL910 series supports both fixed output voltage ranging from 1.2 V to 5 V and adjustable output voltage ranging from 0.8 V to 6 V with an external resistor divider.

Ultra-low noise, high PSRR, and high output current capabilities make the TPL910 series an ideal power supply for noise-sensitive applications, such high-speed as communication facilities and high-definition imaging equipment. Accurate output voltage tolerance, excellent transient response, and adjustable soft-start control ensure the TPL910 series optimal power supply for the large-scale processors or digital loads, such as ASIC, FPGA, CPLD and DSP.

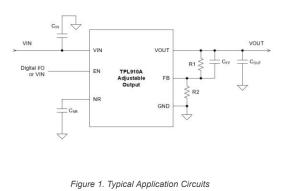

# 1. The TPL910 Typical Application Circuits:

## 2. CNR Effect on the TPL910.

The NR/SS pin is a noise reduction and soft-start pin. A 10-nF or larger capacitor from NR/SS to GND (as close as possible to the NR/SS pin) is recommended to maximize the ac performance. The TPL910 series integrates a programmable soft-start function to control output voltage ramp-up slew rate and start-up time. The output start-up time can be calculated with below equation:

$$T_{\text{Start-up}} = 1.25 \times \frac{V_{\text{NR/SS}} \times C_{\text{NR/SS}}}{I_{\text{NR/SS}}}$$

Where:

- The typical value of V<sub>NR/SS</sub> is 0.8 V

- The typical value of I<sub>NR/SS</sub> is 6.2 µA

- C<sub>NR/SS</sub> is the external capacitor at the NR/SS pin.

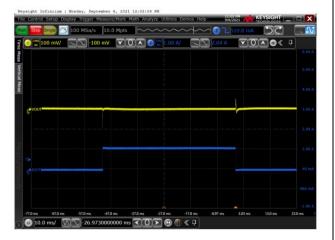

Figure 2 and Figure 3 show TPL910 soft-start waveforms with the different  $C_{NR}$  capacitors.

Test conditions:  $V_{IN} = 2.2 \text{ V}$ ,  $V_{OUT} = 0.8 \text{ V}$ ,  $C_{IN} = 10 \text{ }\mu\text{F}$ ,  $C_{OUT} = 10 \text{ }\mu\text{F}$ ,  $C_{FF} = 10 \text{ }n\text{F}$ ,  $R2 = 10 \text{ }k\Omega$ ,  $R1 = 0 \text{ }k\Omega$ ,  $C_{NR} = 10 \text{ }n\text{F}/470 \text{ }n\text{F}.$

Figure 2. Start-up Waveform (CNR = 10 nF, IOUT = 100 mA)

Figure 3. Start-up Waveform (CNR = 100 nF, IOUT = 100 mA)

The internal reference is the most dominant source of noise in an LDO.  $C_{NR}$  in conjunction with the noise-reduction resistor, forms a low-pass filter (LPF) that filters out the noise from the reference before being gained up with the error amplifier, thereby reducing the device noise floor.

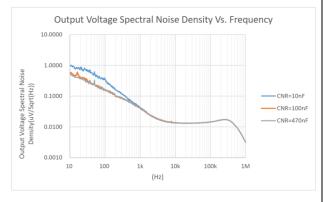

Figure 4 shows different spectral noise density curves with different CNR capacitors. Test conditions :  $V_{IN} = 3.8 \text{ V}, V_{OUT} = 3.3 \text{ V},$  $C_{IN} = 10 \ \mu\text{F}, C_{OUT} = 10 \ \mu\text{F}, C_{FF} = 10 \ n\text{F}, R2 = 10 \ \text{k}\Omega, R1 = 30.9 \ \text{k}\Omega, C_{NR} = 10 \ \text{nF}/100 \ \text{nF}/470 \ \text{nF}.$

Figure 4. Output Voltage Spectra Noise Density  $(C_{\rm NR}=10~{\rm nF}/100~{\rm nF}/470~{\rm nF})$

The Effect of CNR Capacitor and CFF Capacitor in TPL910

### 3. C<sub>FF</sub> Effect on the TPL910

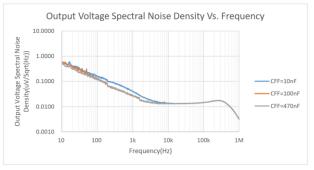

There are several advantages when using the TPL910 with  $C_{FF}$ .  $C_{FF}$  can reduce the output noise and improve the PSRR and the load transient. If the  $C_{FF}$  capacitance is large enough, the TPL910 soft-start time can also be controlled by  $C_{FF}$ .

The reference noise can be gained by external resistors (1+R1/R2), then passed up to the output. At higher frequencies,  $V_{FB}$  and  $V_{OUT}$  are effectively shorted by  $C_{FF}$ , which prevents the reference noise from being increased by the gain of the error amplifier.

Figure 5 shows different spectral noise density curves with different  $C_{FF}$  capacitors.

Test conditions:  $V_{IN} = 3.8V$ ,  $V_{OUT} = 3.3$  V,  $C_{IN} = 10 \ \mu\text{F}$ ,  $C_{OUT} = 10 \ \mu\text{F}$ ,  $C_{NR} = 100 \ n\text{F}$ ,  $R2 = 10 \ k\Omega$ ,  $R1 = 30.9 \ k\Omega$ ,  $C_{FF} = 10 \ n\text{F}/100 \ n\text{F}/470 \ n\text{F}$

The TPL910 uses  $C_{FF}$  to improve the stability of the LDO by adding a zero ( $Z_{FF}$ ) and a pole ( $P_{FF}$ ) to the LDO feedback loop.

$$Z_{FF} = \frac{1}{2 \times \pi \times R1 \times C1}$$

$$P_{FF} = \frac{1}{2 \times \pi \times R1 / / R2 \times C1}$$

The Effect of CNR Capacitor and CFF Capacitor in TPL910

The frequency of  $P_{FF}$  is higher than the frequency of the  $Z_{FF}$ .  $Z_{FF}$  is generated by  $C_{FF}$  improving the phase margin of the TPL910 if  $Z_{FF}$  is close to the open-loop, unity-gain frequency. In addition, the zero increases the bandwidth of the TPL910 feedback loop and improves the load transient response of the TPL910.

Figure 6 and Figure 7 show different load transient waveforms with different  $C_{FF}$  capacitors.

Test conditions :  $V_{IN} = 3.8 \text{ V}$ ,  $V_{OUT} = 3.3 \text{ V}$ ,  $C_{IN} = 10 \ \mu\text{F}$ ,  $C_{OUT} = 10 \ \mu\text{F}$ ,  $C_{NR} = 10 \ n\text{F}$ ,  $R2 = 10 \ k\Omega$ ,  $R1 = 30.9 \ k\Omega$ ,  $C_{FF} = 10 \ n\text{F}$ / no CFF The TPL910 load transient waveform (no CFF)

Figure 7. Iour = 1 mA-1 A TPL910 with CFF = 10 nF during a load transient

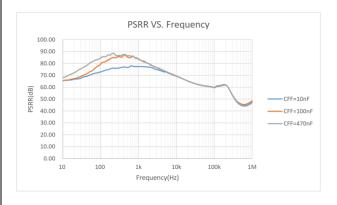

The  $C_{FF}$  capacitor increases the open-loop gain of the circuit, so it can improve the PSRR of the TPL910. Figure 8 shows the different PSRR curves with different  $C_{FF}$  capacitors.

Figure 8. PSRR for Various CFF Capacitor (CFF = 10 nF/100 nF/470 nF)

#### 4. Summary

The noise reduction capacitor  $C_{NR}$  is mainly used to reduce the noise of the internal reference noise, and it can also affect the softstart time of the TPL910. Usually, A 10-nFor larger capacitor is recommended to maximize the ac performance. If lower noise is desired, a 470-nF capacitor is recommended. The feedforward capacitor  $C_{FF}$  can also reduce the output noise and improve load transient performance and PSRR. Usually a 10-nF capacitor is recommended.