# **TPS32 Bootloader User Guide**

Version: A2

| Chapter 1 Introduction         | 2  |

|--------------------------------|----|

| 1.1 Introduction               |    |

| 1.2 Related Documents          |    |

| 1.3 Documentation Conventions  |    |

| Chapter 2 Description          | 5  |

| 2.1 Boot Mode                  |    |

| 2.2 Serial Peripherals         |    |

| 2.3 Memory Management          |    |

| 2.4 Programming Constraints    |    |

| Chapter 3 Bootloader           |    |

| 3.1 Configuration              |    |

| 3.2 Flow Chart                 |    |

| 3.3 Command Set                |    |

| 3.4 Communication Security     |    |

| 3.5 USART Bootloader           |    |

| 3.5.1 USART Bootloader Process |    |

| 3.5.2 USART Baud Rate          |    |

| 3.5.3 Command Implementation   |    |

| 3.6 IIC Bootloader             |    |

| 3.6.1 IIC Bootloader Process   |    |

| 3.6.2 Command Implementation   |    |

| Revision History               |    |

| •                              | 31 |

# **Chapter 1 Introduction**

## **1.1 Introduction**

The bootloader is stored in the TPS325Mx device's internal system memory and is programmed by 3PEAK during the production process. Its main task is to download the application program to the internal main flash memory using available serial peripherals, such as USART and IIC.

Communication protocols are defined for each serial interface to ensure compatibility with command sets and sequences. This document applies to the products listed in Table 1-1 and describes the supported peripherals and hardware requirements when using the TPS32 device's bootloader.

| Product S | eries     | Part Number       |

|-----------|-----------|-------------------|

|           |           | TPS325M0177Q-QP7T |

|           |           | TPS325M0166Q-QP7T |

|           |           | TPS325M0156Q-QP7T |

|           |           | TPS325M0177Q-QP5T |

|           | TPS325M01 | TPS325M0166Q-QP5T |

|           |           | TPS325M0155Q-QP5T |

|           |           | TPS325M0177Q-QP6T |

|           |           | TPS325M0166Q-QP6T |

|           |           | TPS325M0155Q-QP6T |

|           |           | TPS325M5177Q-QP7T |

|           |           | TPS325M5165Q-QP7T |

|           | TPS325M51 | TPS325M5166Q-QP7T |

| TROOOFIA  |           | TPS325M5167Q-QP7T |

| TPS325Mx  |           | TPS325M5155Q-QP7T |

|           |           | TPS325M5156Q-QP7T |

|           |           | TPS325M5177Q-QP5T |

|           |           | TPS325M5166Q-QP5T |

|           |           | TPS325M5155Q-QP5T |

|           |           | TPS325M5177Q-QP6T |

|           |           | TPS325M5166Q-QP6T |

|           |           | TPS325M5177Q-FSDR |

|           |           | TPS325M5177I-FSDR |

|           |           | TPS325M5166I-FSDR |

|           |           | TPS325M5156I-FSDR |

|           | TPS325M0A | TPS325M0A57Q-QP5T |

|           | TPS325M5A | TPS325M5A57Q-QP5T |

| Table 1-1 | Applicable Devices |

|-----------|--------------------|

|-----------|--------------------|

### **1.2 Related Documents**

For device listed in Table 1-1, refer to the following documents and tools from www.3peak.com:

- TPS325M Datasheet

- TPS325M Technical Reference Manual

- TPS32 Programmer User Guide

- TPS32 Programmer Tool

# **1.3 Documentation Conventions**

| Convention  | Usage                                                                                                                                                        |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold        | Displays commands, menu paths, and icon names in<br>procedures.<br>For example:<br>Click the <b>File</b> icon and then click <b>Open</b> .                   |

| File > New  | Represents menu path.<br>For instance:<br><b>File &gt; New &gt;</b> New Project                                                                              |

| Courier New | Displays file locations, user entered text, and source<br>code.<br>For example:<br><your_sdk_path>/example/tpsensor/<br/>tpsensor_exp/source</your_sdk_path> |

# **Chapter 2 Description**

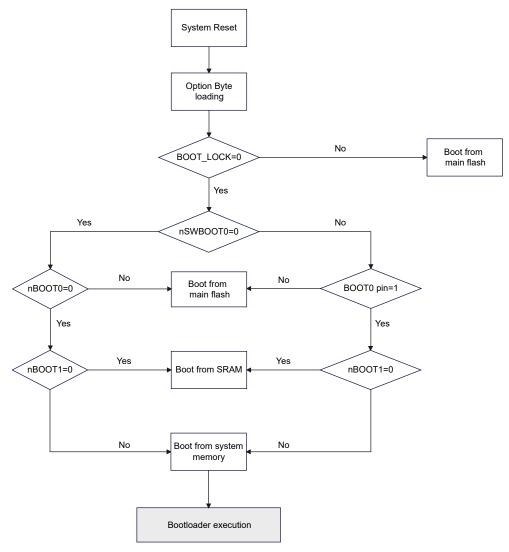

## 2.1 Boot Mode

Flash memory, system memory, and SRAM are the three common types of memory that can be used for storing programs. TPS325M devices support booting from these three types of memory.

The boot mode is controlled by following user option byte bits in the FMC\_OPTR register.

| BOOT_<br>LOCK | nSWBOOT0<br>FMC_OPTR[26] | BOOT0<br>Pin | nBOOT0<br>FMC_OPTR[27] | nBOOT1<br>FMC_OPTR[23] | DBANK<br>FMC_OPTR[22] | SWAPBANK<br>FMC_OPTR[20] | Boot Memory<br>Space Alias                |   |                                           |   |   |                                           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|---------------|--------------------------|--------------|------------------------|------------------------|-----------------------|--------------------------|-------------------------------------------|---|-------------------------------------------|---|---|-------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|

| 1             | x                        | х            | х                      | x                      | х                     | х                        | Main Flash<br>memory Bank0 is<br>selected |   |                                           |   |   |                                           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|               |                          |              |                        |                        | 0                     | х                        | Main Flash<br>memory Bank0 is<br>selected |   |                                           |   |   |                                           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 0             | 1                        | 0            | х                      | x                      | 1                     | 0                        | Main Flash<br>memory Bank0 is<br>selected |   |                                           |   |   |                                           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|               |                          |              |                        |                        | 1                     | 1                        | Main Flash<br>memory Bank1 is<br>selected |   |                                           |   |   |                                           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|               |                          |              |                        |                        |                       |                          | 0                                         | х | Main Flash<br>memory Bank0 is<br>selected |   |   |                                           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 0             | 0                        | 0            | 0                      | 0 X 1 X                | х                     | 1                        | 1                                         | 1 | . 1                                       | 1 | 0 | Main Flash<br>memory Bank0 is<br>selected |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|               |                          |              |                        |                        |                       |                          |                                           |   |                                           |   |   |                                           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 0             | 1                        | 1            | х                      | 0                      | x                     | х                        | Embedded<br>SRAM1 is<br>selected          |   |                                           |   |   |                                           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 0             | 0                        | х            | 0                      | 0                      | x                     | х                        | Embedded<br>SRAM1 is<br>selected          |   |                                           |   |   |                                           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 0             | 1                        | 1            | Х                      | 1                      | х                     | Х                        | System memory<br>is selected              |   |                                           |   |   |                                           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 0             | 0                        | х            | 0                      | 1                      | х                     | Х                        | System memory<br>is selected              |   |                                           |   |   |                                           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

#### Table 2-1 Boot Mode

### **Boot Process**

The boot process is shown in Figure 2-1.

Figure 2-1 Boot Process

If users need the device to execute the bootloader function, they must configure the appropriate control bits in option byte. Setting these control bits will force the device to boot from system memory.

## 2.2 Serial Peripherals

The bootloader for a given TPS32 device may be compatible with various embedded serial peripherals to download code into internal Flash memory. Bootloader identifiers (IDs) are used to identify the supported serial peripherals.

The bootloader ID for the TPS32 device is encoded in one byte format, 0xAB, where:

- A indicates serial peripherals used

- X=1: One USART and one IIC

- B indicates the software version

Moreover, the communication protocols for the various peripherals vary and are indicated by the bootloader version code.

| Des des 4 Ocerica | Support Serial Bootloader ID |      | De offender Versien |                          |

|-------------------|------------------------------|------|---------------------|--------------------------|

| Product Series    | Peripherals                  | ID   | Memory              | Bootloader Version       |

| TPS325Mx          | USART0<br>IIC1               | 0x11 | 0xFFE0000           | USART(V1.1)<br>IIC(V1.1) |

Users may use the GET ID and GET VERSION commands to retrieve the related information.

## 2.3 Memory Management

TPS325M series devices have several internal memory types:

Main Flash Memory

This memory is designated for storing the user's application program.

System Memory

The bootloader is programmed into system memory by 3PEAK during manufacturing and is not user-accessible. It offers a straightforward method for users to upload their applications.

SRAM

Used to store data while the program is running. When power off, the data in SRAM will be lost.

- Other Memories

- OTP

- NVR

- Option bytes

Both OTP and NVR can store specific user data, while option bytes allow users to configure the device before running the application.

Currently, the bootloader only supports modification of the main Flash and option bytes areas, as shown in Table 2-2.

| Memory Area   | Write Command | Read Command | Erase Command | Go Command   |

|---------------|---------------|--------------|---------------|--------------|

| Main Flash    | $\checkmark$  | $\checkmark$ | $\checkmark$  | $\checkmark$ |

| System memory | ×             | ×            | ×             | ×            |

| SRAM          | ×             | ×            | ×             | ×            |

| Option bytes  | $\checkmark$  | $\checkmark$ | ×             | ×            |

| NVR           | ×             | ×            | ×             | ×            |

| OTP           | ×             | ×            | ×             | ×            |

Table 2-2 Supported Memory Operations

(1)  $\sqrt{-Supported}$

(2) × - Not supported

# 2.4 Programming Constraints

Bootloader write commands require data boundary alignment:

- Single bank mode: Addresses must be aligned to 16 bytes.

- Dual bank mode: Addresses must be aligned to 8 bytes.

# Chapter 3 Bootloader

# 3.1 Configuration

When the device boots from system memory, the bootloader will execute and occupy the following hardware resources.

| Bootloader                | Peripherals      | State            | Comment                                                                                                                                                                               |

|---------------------------|------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           | RCC              | IHS              | System clock is 8 MHz.                                                                                                                                                                |

|                           | SYSCFG           | Enabled          | Enable the clock so that the SYSCFG registers can be accessed.                                                                                                                        |

|                           | System<br>memory | -                | 32 Kbytes starting from address 0xFFE0000 contain the bootloader firmware.                                                                                                            |

| Common to all bootloaders | FMC              | -                | All Flash operations through Flash Memory Controller (FMC).                                                                                                                           |

|                           | Main Flash       | -                | Flash memory for users to store their application program.                                                                                                                            |

|                           | SRAM             | -                | 336 Kbytes starting from address 0x20000000 are used by the bootloader.                                                                                                               |

|                           | Systick          | -                | Used to handle timeout in communication                                                                                                                                               |

|                           | USART0           | Enabled          | Once initialized, the USART0 configuration is 8 bits, even parity and 1 Stop bit.                                                                                                     |

| USART bootloader p        | USART0_RX<br>pin | Input            | PA2 pin: USART0 in reception mode.<br>Used in input pull-up mode.                                                                                                                     |

|                           | USART0_TX<br>pin | Output           | PA1 pin: USART0 in transmission mode.<br>Used in alternate push-pull, pull-up mode.                                                                                                   |

|                           | IIC1             | Enabled          | The IIC1 configuration is IIC1 speed: up to 200 kHz,<br>7-bit address, slave mode, analog filter ON.<br>Slave 7-bit address: 0b0000100x<br>(where x = 0 for write and x = 1 for read) |

| IIC bootloader            | IIC1_SCL pin     | Input/<br>Output | PC9 pin: clock line is used in open-drain no pull mode.                                                                                                                               |

|                           | IIC1_SDA pin     | Input/<br>Output | PC8 pin: data line is used in open-drain no pull mode.                                                                                                                                |

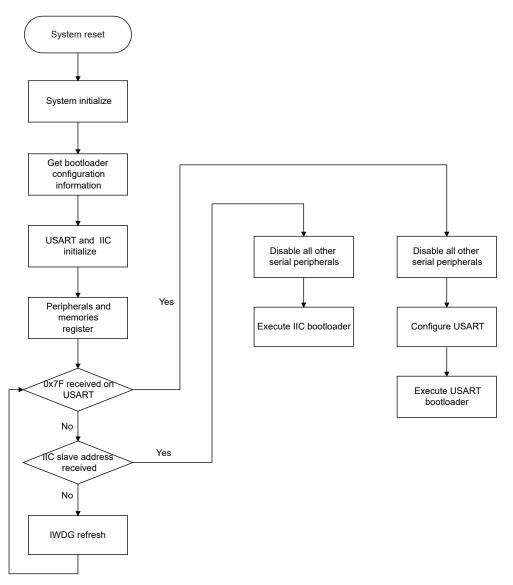

# 3.2 Flow Chart

## 3.3 Command Set

| Туре           | Command <sup>(1)</sup>                                 | Code | Description                                                                                  |

|----------------|--------------------------------------------------------|------|----------------------------------------------------------------------------------------------|

|                | Get <sup>(2)</sup>                                     | 0x11 | Get the version and the allowed commands supported by the current version of the bootloader. |

| Get Infomation | Get Version & Read<br>Protection Status <sup>(2)</sup> | 0x12 | Get the bootloader version.                                                                  |

|                | Get ID <sup>(2)</sup>                                  | 0x13 | Get the bootloader ID.                                                                       |

| Туре                 | Command <sup>(1)</sup> | Code                                                                            | Description                                                                                                   |

|----------------------|------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

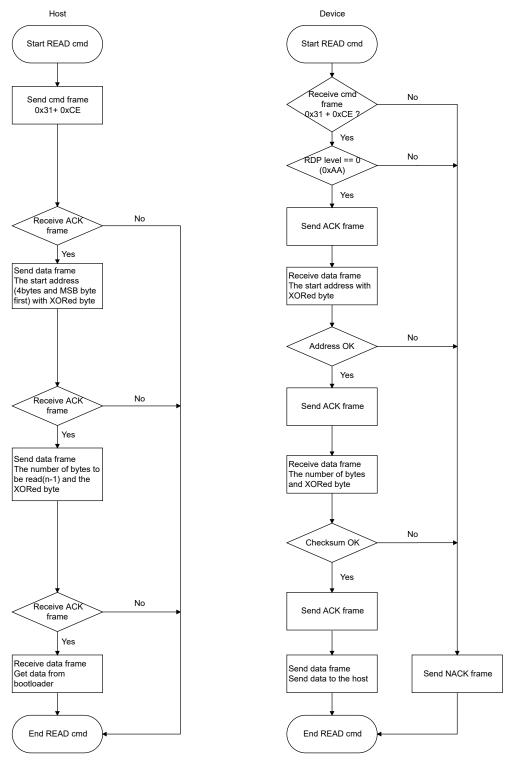

|                      | Read <sup>(3)</sup>    | 0x31                                                                            | Read up to 256 bytes of memory starting from an address specified by the application.                         |

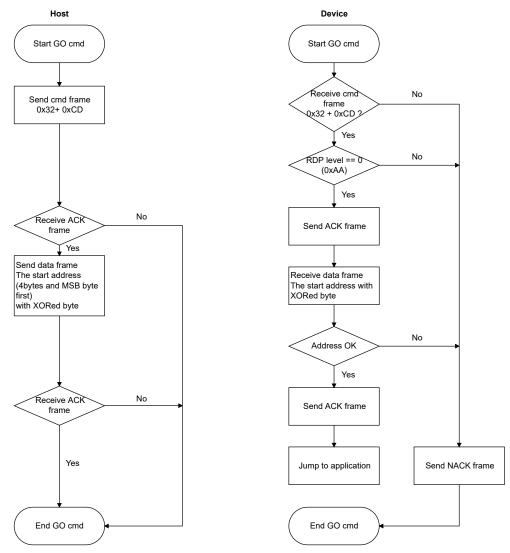

|                      | Go <sup>(3)</sup>      | 0x32                                                                            | Jump to the user application code located in the internal Flash memory or in the SRAM.                        |

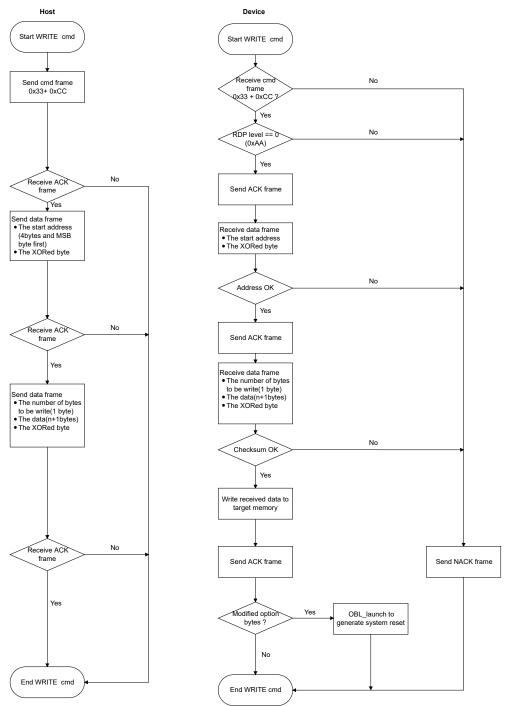

| Memory Operation     | Write <sup>(3)</sup>   | 0x33                                                                            | Write up to 256 bytes to the RAM or Flash<br>memory starting from an address specified by<br>the application. |

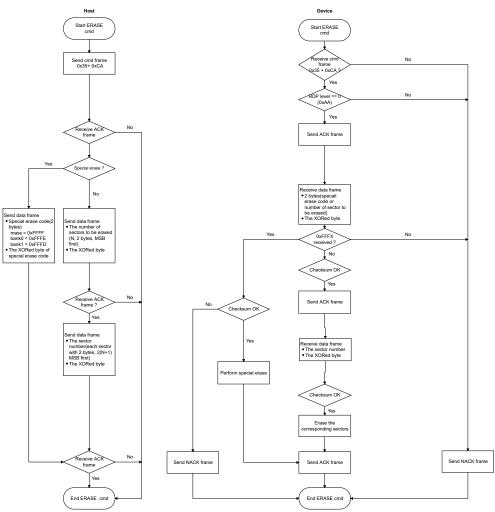

| Erase <sup>(3)</sup> | 0x35                   | Erases from one to all the Flash memory pages using a two-byte addressing mode. |                                                                                                               |

- (1) If a denied command is received or an error occurs during the command execution, the bootloader sends NACK byte and goes back to the command checking.

- (2) Read protection. When the Read protection (RDP) option is active, only this limited subset of commands is available. All other commands are NACK-ed and have no effect on the device. Once the RDP has been removed, the other commands become active.

- (3) Refer to TPS32 product datasheets and technical reference manual to know the valid memory areas for these commands.

## 3.4 Communication Security

All communication from the programming tool (PC) to the device undergoes verification:

- **1.** The received data block bytes are XORed. The computed XOR value of all previous bytes is added to the end of each communication (checksum byte).

- 2. For each command, the host sends a byte and its complement (XOR = 0x00).

- 3. UART: Parity check is active (even parity).

- **4.** Each data packet is either accepted (ACK response, 0xA3) or discarded (NACK response, 0x1A).

## 3.5 USART Bootloader

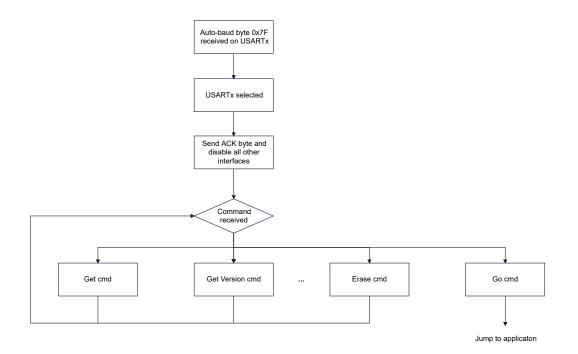

### 3.5.1 USART Bootloader Process

When the system memory boot mode is selected and a system reset occurs, the bootloader program starts to scan the USART interface for auto-baud rate detection byte(0x7F). Once the 0x7F data frame is captured, the baud rate is updated at the end of the  $6^{th}$  bit. Then bootloader program sends the ACK byte (0xA3) to the host and is ready to get command.

Figure 3-2 USART Bootloader Flow Chart

### 3.5.2 USART Baud Rate

Calculating the USARTx baud rate from the first received byte enables boot loader operation across a wide range of baud rates. However, upper and lower limits must be enforced to ensure reliable data transmission.

To properly transfer data from host to microcontroller, the maximum deviation between USARTx's initial internal baud rate and the host's actual baud rate must be less than 2%. The deviation between the host and microcontroller baud rates (E, expressed in percentage) is calculated as:

(1)

- Minimum baud rate: 1200 bit/s

- Maximum baud rate: 115200 bit/s

### **3.5.3 Command Implementation**

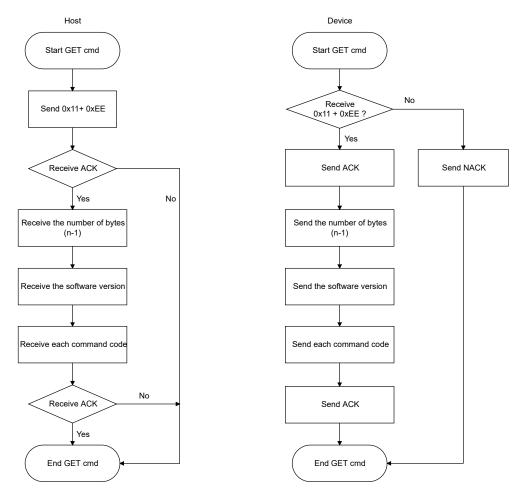

#### 3.5.3.1 GET Command

Upon receiving the GET command, the bootloader transmits the supported command codes, command count, and bootloader version to the host. See the following figures for the exchange flow chart:

**NOTE:** All the number of bytes exchanged during communication is the actual byte number minus one.

The device sends the bytes as below:

| Byte 1  | 0xA3 | ACK                                                     |

|---------|------|---------------------------------------------------------|

| Byte 2  | 0x7  | The number of bytes to be transmitted (exact number -1) |

| Byte 3  | 0×11 | software version                                        |

| Byte 4  | 0×11 | GET code                                                |

| Byte 5  | 0x12 | GET VERSION code                                        |

| Byte 6  | 0x13 | GET ID code                                             |

| Byte 7  | 0x31 | MEMORY READ code                                        |

| Byte 8  | 0x32 | MEMORY WRITE code                                       |

| Byte g  | 0x33 | GO code                                                 |

| Byte 10 | 0x35 | MEMORY ERASE code                                       |

| Byte 11 | 0xA3 | ACK                                                     |

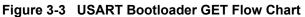

#### 3.5.3.2 GET VERSION Command

The Get VERSION command is used to obtain the bootloader version. Once the command is received, the bootloader sends the version to the host.

Figure 3-4 USART Bootloader GET VERSION Flow Chart

The device sends the bytes as below:

| Byte 1 | 0xA3 | АСК                    |

|--------|------|------------------------|

| Byte 2 | 0x11 | The bootloader version |

| Byte 3 | 0xA3 | ACK                    |

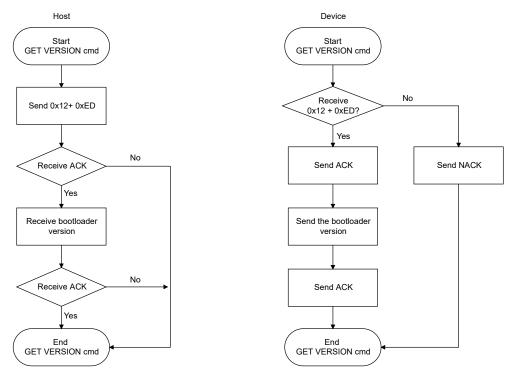

#### 3.5.3.3 GET ID Command

The Get ID command is used to get the chip device ID that has information about serial interfaces supported and communication protocol version.

Figure 3-5 USART Bootloader GET ID Flow Chart

The device sends the bytes as below:

| Byte1 | 0xA3 | ACK                 |  |

|-------|------|---------------------|--|

| Byte2 | 0x3  | The number of bytes |  |

| Byte3 | 0x23 | ID MSB              |  |

| Byte4 | 0x0  |                     |  |

| Byte5 | 0×0  |                     |  |

| Byte6 | 0x1  | ID LSB              |  |

| Byte7 | 0xA3 | ACK                 |  |

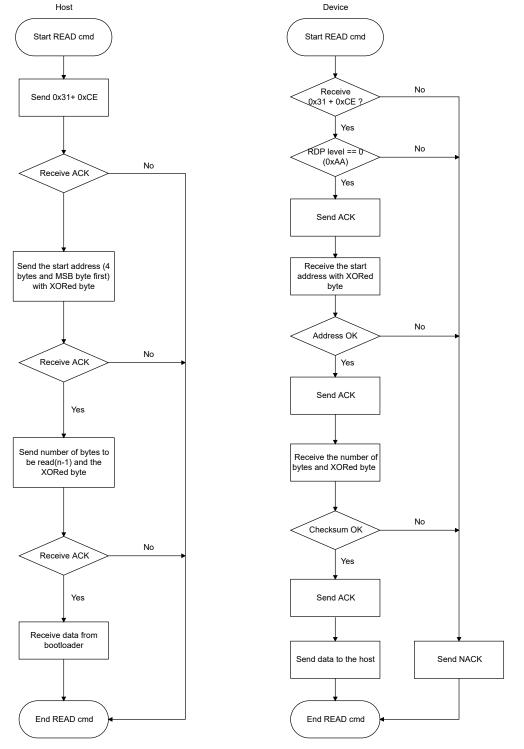

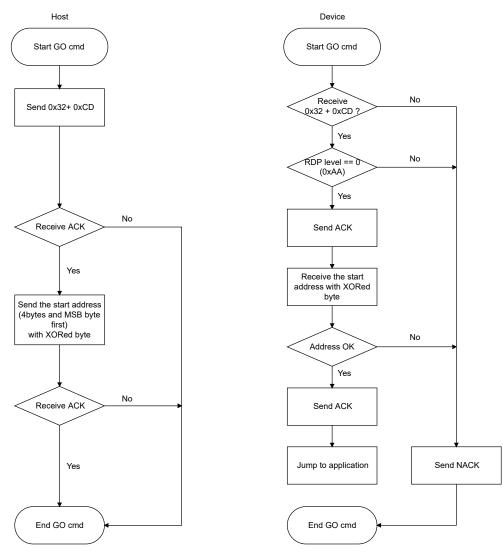

#### 3.5.3.4 READ Command

The READ command is used to read data from memory supported by bootloader, including main Flash memory and option byte area. The maximum size of the data to be read is 256 bytes.

The host sends the bytes as an example:

| Byte | 9 1     | 0x31 | cmd code                                  |

|------|---------|------|-------------------------------------------|

| Byte | 2       | 0×CE | XORed byte of cmd code                    |

| Wait | for ACK |      |                                           |

| Byte | 9 3     | 0×08 | Address MSB byte                          |

| Byte | 9 4     | 0×0  |                                           |

| Byte | 9 5     | 0×0  |                                           |

| Byte | 9 6     | 0×0  | Address LSB byte                          |

| Byte | 9 7     | 0×08 | XORed byte of bytes 3 to 5                |

| Wait | for ACK |      |                                           |

| Byte | 8       | 0×FF | The number of bytes to be read -1 (0~255) |

| Byte | 9       | 0×0  | XORed byte of byte 8                      |

|      |         |      |                                           |

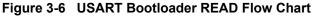

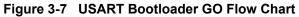

#### 3.5.3.5 GO Command

The GO command is used to jump to application code, which is programmed in the main Flash through the bootloader.

When device gets the GO command and a valid address to jump, the bootloader will:

- **1.** Deinitialize all the peripherals used in the bootloader code.

- **2.** Initialize the main stack pointer of the application code.

- **3.** Jump to the application entrance address.

The host sends the bytes as an example:

| Byte 1       | 0x32 | cmd code                   |  |

|--------------|------|----------------------------|--|

| Byte 2       | 0xCD | XORed byte of cmd code     |  |

| Wait for ACK |      |                            |  |

| Byte 3       | 0x08 | Address MSB byte           |  |

| Byte 4       | 0x0  |                            |  |

| Byte 5       | 0×0  |                            |  |

| Byte 6       | 0×0  | Address LSB byte           |  |

| Byte 7       | 0x08 | XORed byte of bytes 3 to 6 |  |

| Wait for ACK |      |                            |  |

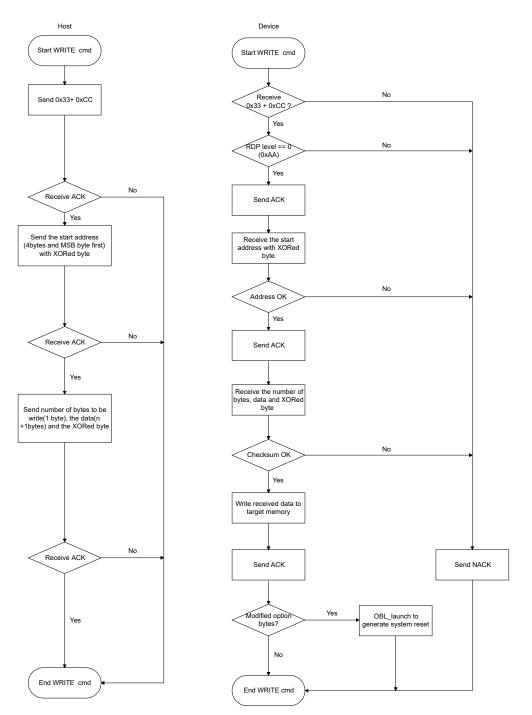

#### 3.5.3.6 WRITE command

The WRITE command is used to write data to memory supported by the bootloader, including the main Flash memory and option byte area. The maximum size of the data to be written is 256 bytes.

- **NOTE: 1.** The main Flash and OTP area must be erased first before the write operation being performed.

- 2. For OTP, the address to be written must be 8 bytes aligned.

- **3.** For main Flash, the address must be:

- 16 bytes aligned in single bank mode.

- 8 bytes aligned in dual bank mode.

Host sends the bytes like below to write 0x11111111 and 0x22222222 to address 0x8000000.

| Byte 1       | 0x33 | cmd code                                      |

|--------------|------|-----------------------------------------------|

| Byte 2       | 0xCC | XORed byte of cmd code                        |

| Wait for ACK |      |                                               |

| Byte 3       | 0x08 | Address MSB byte                              |

| Byte 4       | 0x0  |                                               |

| Byte 5       | 0x0  |                                               |

| Byte 6       | 0x0  | Address LSB byte                              |

| Byte 7       | 0x08 | XORed byte of bytes 3 to 5                    |

| Wait for ACK |      |                                               |

| Byte 8       | 0x7  | N: the number of bytes to be write -1 (0~255) |

| Byte 9       | 0x11 | The first byte of data                        |

| Byte 10      | 0x11 |                                               |

| Byte 11      | 0x11 |                                               |

| Byte 12      | 0x11 |                                               |

| Byte 13      | 0x22 |                                               |

| Byte 14      | 0x22 |                                               |

| Byte 15      | 0x22 |                                               |

| Byte 16      | 0x22 | The last byte of data                         |

| Byte 17      | 0x7  | XORed checksum                                |

| Wait for ACK |      |                                               |

|              |      |                                               |

Figure 3-8 USART Bootloader WRITE Flow Chart

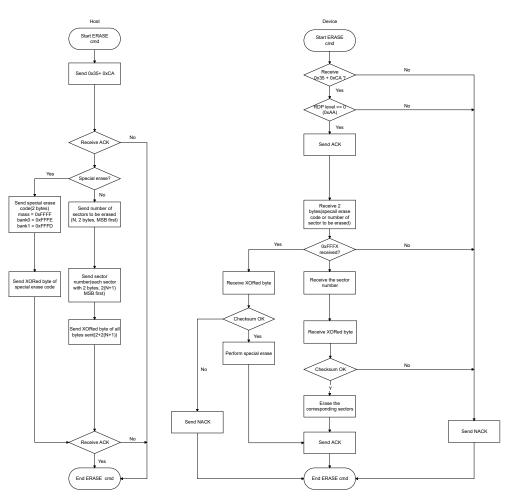

#### 3.5.3.7 ERASE command

The ERASE command allows the host to erase the main Flash memory of the device, and it supports mass erase, bank erase, and sector erase.

Figure 3-9 USART Bootloader ERASE Command Flow Chart

From perspective of the device, when receiving the ERASE command and sending ACK to the host, it starts to wait for 2 bytes (N):

- Either special erase code in special erase mode,

- N = 0xFFFF: mass erase

- N = 0xFFFE: bank0 erase

- N = 0xFFFD: bank1 erase

- Or the number of sectors to be erased in sector erase mode.

- 0  $\leq$  N  $\leq$  the maximum sector number of the device

- **NOTE:** The exact number of sectors to be erased is (N+1), and the bootloader receives 2× (N+1) bytes representing corresponding sectors.

The host sends the bytes as below to perform bank 0 erase:

| Byte 1       | 0x35 | cmd code                   |  |

|--------------|------|----------------------------|--|

| Byte 2       | 0xCA | XORed byte of cmd code     |  |

| Wait for ACK |      |                            |  |

| Byte 3       | 0×FF | Special erase code MSB     |  |

| Byte 4       | 0×FE | Special erase code LSB     |  |

| Byte 5       | 0×01 | XORed byte of bytes 3 to 4 |  |

| Wait for ACK |      |                            |  |

The host performs sector erase to erase sector 2, 4, 6 (the sector index starts from 0).

| Byte 1       | 0x35 | cmd code                               |

|--------------|------|----------------------------------------|

| Byte 2       | 0xCA | XORed byte of cmd code                 |

| Wait for ACK |      |                                        |

| Byte 3       | 0×0  | The number of sectors to be erased MSB |

| Byte 4       | 0×2  | The number of sectors to be erased LSB |

| Byte 5       | 0×0  | The first sector number MSB            |

| Byte 6       | 0×1  | The first sector number LSB            |

| Byte 7       | 0×0  | The second sector number MSB           |

| Byte 8       | 0×3  | The second sector number LSB           |

| Byte 9       | 0×0  | The third sector number MSB            |

| Byte 10      | 0×5  | The third sector number LSB            |

| Byte 11      | 0×5  | The XORed byte                         |

| Wait for ACK |      |                                        |

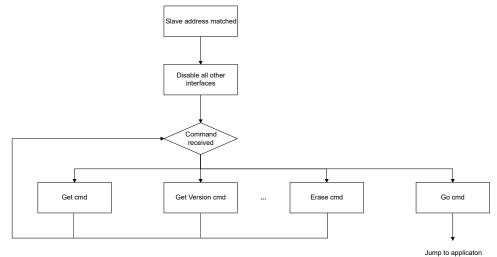

# 3.6 IIC Bootloader

### 3.6.1 IIC Bootloader Process

### 3.6.2 Command Implementation

The application layer data exchanged between the host and the device are same comparing with USART bootloader , but the logical link layer data frame is different.

In USART transmission, each byte is a data frame.

The order and definition of the bits appearing on the IIC bus and how they are clocked are determined by IIC protocol. The IIC data frame is shown below:

|      |        | Host wri  | te to device data frame  |           |         |      |   |         |      |   |          |

|------|--------|-----------|--------------------------|-----------|---------|------|---|---------|------|---|----------|

|      |        | start bit | 7bits address            | write bit | ack bit |      | n | data by | rtes |   | stop bit |

| Host | Device | s         | slave address            | W         | A       | data | А |         | data | A | Р        |

|      |        |           |                          |           |         |      |   |         |      |   |          |

|      |        | Host rea  | d from device data frame |           |         |      |   |         |      |   |          |

|      |        | start bit | 7bits address            | read bit  | ack bit |      | n | data by | tes  |   | stop bit |

|      |        | s         | slave address            | R         | A       | data | A |         | data |   | D        |

Figure 3-11 IIC Data Frame

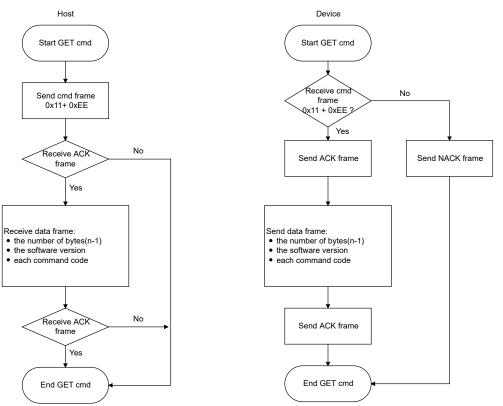

#### 3.6.2.1 GET Command

The device sends the frames and bytes:

| Frame 1 | Byte 1 | 0xA3 | ACK frame                                               |

|---------|--------|------|---------------------------------------------------------|

| Frame 2 | Byte 1 | 0x7  | The number of bytes to be transmitted (exact number -1) |

|         | Byte 2 | 0x11 | Software version                                        |

|         | Byte 3 | 0x11 | GET code                                                |

|         | Byte 4 | 0x12 | GET VERSION code                                        |

|         | Byte 5 | 0x13 | GET ID code                                             |

|         | Byte 6 | 0x31 | MEMORY READ code                                        |

|         | Byte 7 | 0x32 | MEMORY WRITE code                                       |

|         | Byte 8 | 0x33 | GO code                                                 |

|         | Byte 9 | 0x35 | MEMORY ERASE code                                       |

| Frame 3 | Byte 1 | 0xA3 | ACK frame                                               |

NOTE: The slave address of device is 0x8.

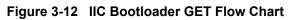

#### 3.6.2.2 GET VERSION Command

Figure 3-13 IIC Bootloader GET VERSION Flow Chart

The device sends the frames and bytes:

| Frame 1 | Byte 1 | 0xA3 | ACK                    |

|---------|--------|------|------------------------|

| Frame 2 | Byte 1 | 0x11 | The bootloader version |

| Frame 3 | Byte 1 | 0xA3 | ACK                    |

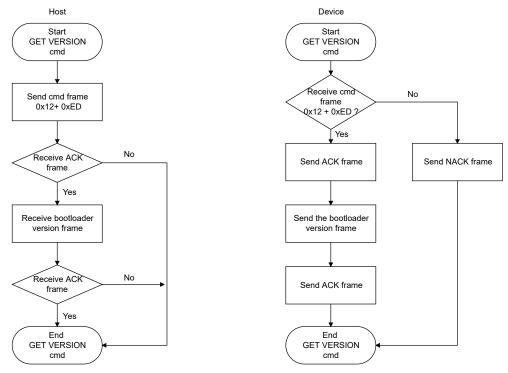

#### 3.6.2.3 GET ID Command

Figure 3-14 IIC Bootloader GET ID Flow Chart

The device sends the frames and bytes:

| Byte1 | 0xA3 | ACK                 |  |

|-------|------|---------------------|--|

| Byte2 | 0x3  | The number of bytes |  |

| Byte3 | 0x23 | ID MSB              |  |

| Byte4 | 0x0  |                     |  |

| Byte5 | 0x0  |                     |  |

| Byte6 | 0x1  | ID LSB              |  |

| Byte7 | 0xA3 | ACK                 |  |

#### 3.6.2.4 READ Command

Figure 3-15 IIC Bootloader READ Flow Chart

| Frame 1  | Byte 1    | 0x31 | cmd code                                     |

|----------|-----------|------|----------------------------------------------|

|          | Byte 2    | 0xCE | XORed byte of cmd code                       |

| Wait for | ACK frame |      |                                              |

| Frame 2  | Byte 1    | 0x08 | Address MSB byte                             |

|          | Byte 2    | 0x0  |                                              |

|          | Byte 3    | 0x0  |                                              |

|          | Byte 4    | 0x0  | Address LSB byte                             |

|          | Byte 5    | 0x08 | XORed byte of bytes 3 to 5                   |

| Wait for | ACK frame |      |                                              |

| Frame 3  | Byte 1    | OxFF | N: the number of bytes to be read -1 (0~255) |

|          | Byte 2    | 0x0  | XORed byte of byte 1 in frame 3              |

### 3.6.2.5 GO Command

| 0xCD<br>0x08 | XORed byte of cmd code<br>Address MSB byte |                                                                                |

|--------------|--------------------------------------------|--------------------------------------------------------------------------------|

| 0×08         | Address MSB byte                           |                                                                                |

|              | Address MSB byte                           |                                                                                |

|              |                                            |                                                                                |

| 0x0          |                                            |                                                                                |

| 0×0          |                                            |                                                                                |

| 0×0          | Address LSB byte                           |                                                                                |

| 0×08         | XORed byte of bytes 3 to 6                 |                                                                                |

|              | 0×0<br>0×0<br>0×08                         | 0x0         Address LSB byte           0x08         XORed byte of bytes 3 to 6 |

#### 3.6.2.6 WRITE command

Figure 3-17 IIC Bootloader WRITE Flow Chart

| Frame 1            | Byte 1    | 0x33 | cmd code                                      |

|--------------------|-----------|------|-----------------------------------------------|

|                    | Byte 2    | 0xCC | XORed byte of cmd code                        |

| Wait for ACK frame |           |      |                                               |

| Frame 2            | Byte 1    | 0×08 | Address MSB byte                              |

|                    | Byte 2    | 0x0  |                                               |

|                    | Byte 3    | 0x0  |                                               |

|                    | Byte 4    | 0x0  | Address LSB byte                              |

|                    | Byte 5    | 0x08 | XORed byte of bytes 1 to 4                    |

| Wait for ACK frame |           |      |                                               |

| Frame 3            | Byte 1    | 0x7  | N: the number of bytes to be write -1 (0~255) |

|                    | Byte 2    | 0×11 | The first byte of data                        |

|                    | Byte 3    | 0x11 |                                               |

|                    | Byte 4    | 0x11 |                                               |

|                    | Byte 5    | 0x11 |                                               |

|                    | Byte 6    | 0x22 |                                               |

|                    | Byte 7    | 0x22 |                                               |

|                    | Byte 8    | 0x22 |                                               |

|                    | Byte 9    | 0x22 | The last byte of data                         |

|                    | Byte 10   | 0x7  | XORed checksum                                |

| Wait for           | ACK frame |      |                                               |

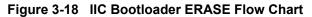

### 3.6.2.7 ERASE command

| Frame 1    | Byte 1    | 0x35 | cmd code                   |

|------------|-----------|------|----------------------------|

|            | Byte 2    | 0×CA | XORed byte of cmd code     |

| Wait for . | ACK frame |      |                            |

| Frame 2    | Byte 1    | 0×FF | Special erase code MSB     |

|            | Byte 2    | 0×FE | Special erase code LSB     |

|            | Byte 3    | 0×01 | XORed byte of bytes 3 to 4 |

| Frame 1  | Byte 1    | 0×35 | cmd code                               |

|----------|-----------|------|----------------------------------------|

|          | Byte 2    | 0xCA | XORed byte of cmd code                 |

| Wait for | ACK frame |      |                                        |

| Frame 2  | Byte 1    | 0x0  | The number of sectors to be erased MSB |

|          | Byte 2    | 0x2  | The number of sectors to be erased LSB |

|          | Byte 3    | 0×FD | XORed byte of bytes 1 and 2            |

| Wait for | ACK frame |      |                                        |

| Frame 3  | Byte 1    | 0×0  | The first sector number MSB            |

|          | Byte 2    | 0×1  | The first sector number LSB            |

|          | Byte 3    | 0×0  | The second sector number MSB           |

|          | Byte 4    | 0×3  | The second sector number LSB           |

|          | Byte 5    | 0×0  | The third sector number MSB            |

|          | Byte 6    | 0×5  | The third sector number LSB            |

|          | Byte 7    | 0x7  | The XORed byte                         |

| Wait for | ACK frame |      |                                        |

### **Revision History**

| Date       | Version | Changes                                                                                                                                           |

|------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 2024-04-10 | Rev.A.2 | <ul> <li>Modified part of the table data information in Section 3.1<br/>Configuration.</li> <li>Some editorial changes have been made.</li> </ul> |

| 2023-12-07 | Rev.A.1 | <ul><li>Updated Figure 2-1.</li><li>Updated Table 2-1.</li></ul>                                                                                  |

| 2023-11-30 | Rev.A.0 | Initial release                                                                                                                                   |

### **IMPORTANT NOTICE AND DISCLAIMER**

Copyright<sup>©</sup> 3PEAK 2012-2024. All rights reserved.

**Trademarks**. Any of the 思瑞浦 or 3PEAK trade names, trademarks, graphic marks, and domain names contained in this document /material are the property of 3PEAK. You may NOT reproduce, modify, publish, transmit or distribute any Trademark without the prior written consent of 3PEAK.

**Performance Information**. Performance tests or performance range contained in this document/material are either results of design simulation or actual tests conducted under designated testing environment. Any variation in testing environment or simulation environment, including but not limited to testing method, testing process or testing temperature, may affect actual performance of the product.

**Disclaimer**. 3PEAK provides technical and reliability data (including data sheets), design resources (including reference designs), application or other design recommendations, networking tools, security information and other resources "As Is". 3PEAK makes no warranty as to the absence of defects, and makes no warranties of any kind, express or implied, including without limitation, implied warranties as to merchantability, fitness for a particular purpose or non-infringement of any third-party's intellectual property rights. Unless otherwise specified in writing, products supplied by 3PEAK are not designed to be used in any life-threatening scenarios, including critical medical applications, automotive safety-critical systems, aviation, aerospace, or any situations where failure could result in bodily harm, loss of life, or significant property damage. 3PEAK disclaims all liability for any such unauthorized use.