#### **Features**

- Exceeds the M-LVDS Standard TIA/EIA-899 for Multipoint Data Interchange

- Low-Voltage Differential  $30-\Omega$  to  $55-\Omega$  Line Drivers and Receivers for Signaling Rates, up to 200 Mbps

- Type-2 Receivers Provide an Offset (80 mV) Threshold to Detect Open-Circuit and Idle-Bus

- Conditions:

- -1-V to 3.4-V Common-Mode Voltage Range

- · Allows Data Transfer with 2 V of Ground Noise

- Bus Pins High Impedance when Disabled or V<sub>CC</sub> ≤ 1.5 V

- Bus-Pin Protection: ±8-kV HBM Model

- -40°C to 85°C Operation Temperature Range

#### **Applications**

- Backplane Multipoint Data/ Clock Transmission

- Cellular Base Stations

- Network Switches and Routers

- Industrial Control

- Communication Infrastructure

#### **Description**

The TPT9H221A is a 3.3-V Multipoint-Low-Voltage Differential (M-LVDS) line driver and receiver, which can operate at signaling rates up to 200 Mbps. Driver outputs and receiver inputs are protected against  $\pm 8$ -kV ESD strikes without latch-up. The driver output has been designed to support multipoint buses presenting loads as low as 30  $\Omega$ , and incorporates controlled transition times to allow for stubs off of the backbone transmission line.

The TPT9H221A is a Type-2 receiver that detects the bus state with a differential input of 50 mV over a common-mode voltage range from −1 V to 3.4 V. Type-2 receiver includes an offset threshold to provide a known output state under open-circuit fail-safe, idle-bus fail-safe. The device is characterized for operation from −40°C to 85°C. The device is available as a half-duplex in an 8-pin SOP package.

### **Typical Application Circuits**

## **Table of Contents**

| Applications                                |      |

|---------------------------------------------|------|

|                                             |      |

| Description                                 | 1    |

| Typical Application Circuits                | 1    |

| Revision History                            | 3    |

| Pin Configuration and Functions             | 4    |

| Specifications                              | 6    |

| Absolute Maximum Ratings <sup>(1)</sup>     | 6    |

| ESD, Electrostatic Discharge Protection     | 6    |

| Recommended Operating Conditions            | 6    |

| Thermal Information                         | 6    |

| Electrical Characteristics                  | 7    |

| Test Circuits, Configurations and Waveforms | . 11 |

| Detailed Description                        | . 16 |

| Overview                                    | .16  |

| Tape and Reel Information                   | . 17 |

| Package Outline Dimensions                  | 18   |

| SOP8                                        | . 18 |

| Order Information                           | . 19 |

| IMPORTANT NOTICE AND DISCLAIMER             | . 20 |

# **Revision History**

| Date       | Revision  | Notes            |

|------------|-----------|------------------|

| 2024-03-21 | Rev. A. 0 | Released version |

www.3peak.com 3 / 20 CA20230901A0

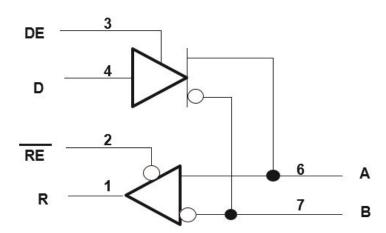

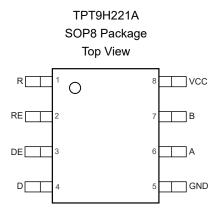

# **Pin Configuration and Functions**

Table 1. Pin Functions: TPT9H221A

| Pin No. | Name | I/O            | Description                 |

|---------|------|----------------|-----------------------------|

| 1       | R    | Digital output | Receiver Output             |

| 2       | /RE  | Digital input  | Receiver Output Enable      |

| 3       | DE   | Digital input  | Driver Output Enable        |

| 4       | D    | Digital input  | Driver Input                |

| 5       | GND  | Ground         | Ground                      |

| 6       | Α    | Bus input      | Noninverting Receiver Input |

| 7       | В    | Bus input      | Inverting Receiver Input    |

| 8       | Vcc  | Power          | Power Supply                |

#### **Device Function Tables**

**Table 2. Truth Table Abbreviations**

| Abbreviation | Description          |

|--------------|----------------------|

| Н            | High level           |

| L            | Low level            |

| X            | Don't care           |

| I            | Indeterminate        |

| Z            | High impedance (off) |

| NC           | Disconnected         |

www.3peak.com 4 / 20 CA20230901A0

Table 3. Driver

| Input | Enable | Outputs |   |  |

|-------|--------|---------|---|--|

| D     | DE     | A       | В |  |

| L     | Н      | L       | Н |  |

| Н     | Н      | н       | L |  |

| OPEN  | Н      | L       | Н |  |

| X     | OPEN   | Z       | Z |  |

| X     | L      | z       | Z |  |

- (1) H = high level

- (2) L = low level

- (3) Z = high impedance

- (4) X = Don't care

- (5) ? = indeterminate

Table 4. Type-2 Receiver

| Inputs                                            | Output |   |

|---------------------------------------------------|--------|---|

| V <sub>ID</sub> = V <sub>A</sub> - V <sub>B</sub> | RE     | R |

| V <sub>ID</sub> ≥ 150 mV                          | L      | Н |

| 50 mV < V <sub>ID</sub> < 150 mV                  | L      | ? |

| V <sub>ID</sub> ≤ 50 mV                           | L      | L |

| X                                                 | Н      | Z |

| X                                                 | Open   | Z |

| Open Circuit                                      | L      | L |

Table 5. Type-2 Receiver Input Threshold Test Voltages

| Applied Voltage |                 | Differential<br>Input Voltages | Common Mode<br>Input Voltage | Receiver Output (1) |

|-----------------|-----------------|--------------------------------|------------------------------|---------------------|

| VIA             | V <sub>IB</sub> | V <sub>ID</sub>                | V <sub>IC</sub>              |                     |

| 2.400           | 0.000           | 2.400                          | 1.200                        | Н                   |

| 0.000           | 2.400           | -2.400                         | 1.200                        | L                   |

| 3.800           | 3.650           | 0.150                          | 3.725                        | Н                   |

| 3.800           | 3.750           | 0.050                          | 3.775                        | L                   |

| -1.250          | -1.400          | 0.150                          | -1.325                       | Н                   |

| -1.350          | -1.400          | 0.050                          | -1.375                       | L                   |

<sup>(1)</sup> H = high level, L = low level, output state assumes receiver is enabled (RE = L).

www.3peak.com 5 / 20 CA20230901A0

### **Specifications**

#### Absolute Maximum Ratings (1)

|                  | Parameter                                          | Min  | Max | Unit |

|------------------|----------------------------------------------------|------|-----|------|

|                  | V <sub>CC</sub> to GND                             | -0.5 | 4   | V    |

|                  | Voltage at Logic pin: D, DE, /RE, R <sup>(2)</sup> | -0.3 | 4   | \ \  |

|                  | Voltage at Bus pin: A, B                           | -1.8 | 4   | V    |

|                  | Operating Temeprature Range                        | -40  | 85  | °C   |

| T <sub>stg</sub> | Storage Temperature Range                          | -65  | 150 | ů    |

| TJ               | Maximum Junction Temperature                       |      | 150 | °C   |

|                  | Lead Temperature (Soldering, 10 sec)               |      | 260 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

#### **ESD, Electrostatic Discharge Protection**

|      | Parameter              | Condition              | Value | Unit |

|------|------------------------|------------------------|-------|------|

| НВМ, | ANSI/ESDA/JEDEC JS-001 | Bus Pin                | 8     | kV   |

|      |                        | All Pin Except Bus Pin | 4     | kV   |

| CDM  | ANSI/ESDA/JEDEC JS-002 | All Pin                | 1     | kV   |

#### **Recommended Operating Conditions**

|                 | Parameter                                                  | Min  | Тур | Max | Unit |

|-----------------|------------------------------------------------------------|------|-----|-----|------|

| Vcc             | Supply Voltage                                             | 3    | 3.3 | 3.6 | V    |

| V <sub>IH</sub> | High-Level Input Voltage                                   | 2    |     | VCC | V    |

| V <sub>IL</sub> | Low-Level Input Voltage                                    | GND  |     | 0.8 | V    |

|                 | Voltage at any Bus Terminal V <sub>A</sub> ,V <sub>B</sub> | -1.4 |     | 3.8 | V    |

| V <sub>ID</sub> | Magnitude of Differential Input Voltage                    | 0.05 |     | VCC | V    |

| T <sub>A</sub>  | Operating Temperature Range                                | -40  |     | 85  | °C   |

#### **Thermal Information**

| Package Type | θја | θυς | Unit |

|--------------|-----|-----|------|

| SOP8         | 130 | 52  | °C/W |

<sup>(1)</sup>  $\theta_{JA}$  = 130°C/W is typical value of SOP8 provided by package assembly house.

www.3peak.com 6 / 20 CA20230901A0

<sup>(2)</sup> This data was taken with the JEDEC low effective thermal conductivity test board.

#### **Electrical Characteristics**

All test conditions:  $V_{CC}$  = 3.0 V ~ 3.6 V,  $T_A$  = -40 ~ +85°C, unless otherwise noted.

|                      | Parameter                                                                          | Conditions                                                                                                 | Min           | Тур | Max | Unit |

|----------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|---------------|-----|-----|------|

| Power S              | upply                                                                              |                                                                                                            |               |     |     |      |

| Vcc                  | Supply Voltage                                                                     |                                                                                                            | 3             |     | 3.6 | V    |

|                      | Driver only                                                                        | RE and DE at $V_{CC}$ , $R_L$ = 50 $\Omega$ , All others open                                              |               | 13  | 22  | mA   |

| lcc<br>Supply        | Both Disabled                                                                      | RE at $V_{CC}$ , DE at 0 V, $R_L$ = No Load, All others open                                               |               | 2   | 4   | mA   |

| Supply<br>Current    | Both Enabled                                                                       | RE at 0 V, DE at V <sub>CC</sub> , R <sub>L</sub> = 50 $\Omega$ , All others open                          |               | 15  | 24  | mA   |

|                      | Receiver only                                                                      | RE at 0 V, DE at 0 V, R <sub>L</sub> = 50 $\Omega$ , All others open                                       |               | 4   | 13  | mA   |

|                      |                                                                                    | V <sub>A</sub> = 3.8 V, V <sub>B</sub> = 1.2 V,                                                            | 0             |     | 32  | μA   |

| $I_{Am}$             | Receiver or Transceiver with Driver Disabled Input Current                         | V <sub>A</sub> = 0 V or 2.4 V, V <sub>B</sub> = 1.2 V                                                      | -20           |     | 20  | μA   |

|                      | Disabled input durient                                                             | V <sub>A</sub> = -1.4 V, V <sub>B</sub> = 1.2 V                                                            | -32           |     | 0   | μA   |

|                      | Receiver or Transceiver with Driver<br>Disabled Input Current                      | V <sub>B</sub> = 3.8 V, V <sub>A</sub> = 1.2 V                                                             | 0             |     | 32  | μA   |

| lΒ                   |                                                                                    | V <sub>B</sub> = 0 V or 2.4 V, V <sub>A</sub> = 1.2 V                                                      | -20           |     | 20  | μA   |

|                      |                                                                                    | V <sub>B</sub> = -1.4 V, V <sub>A</sub> = 1.2 V                                                            | -32           |     | 0   | μΑ   |

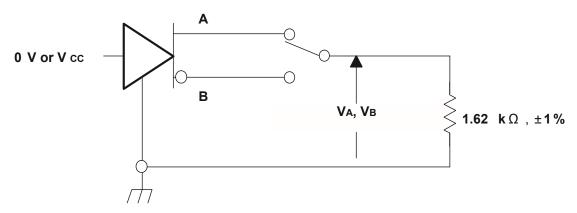

| I <sub>AB</sub>      | Receiver or Transceiver with Driver  Disabled Differential Input Current  (IA— IB) | V <sub>A</sub> = V <sub>B</sub> , 1.4 ≤ V <sub>A</sub> ≤ 3.8 V                                             | -4            |     | 4   | μА   |

|                      | Receiver or Transceiver Power-off Input Current                                    | $V_A = 3.8 \text{ V}, V_B = 1.2 \text{ V},$<br>$0 \text{ V} \leq V_{CC} \leq 1.5 \text{ V}$                | 0             |     | 32  | μA   |

| I <sub>A (OFF)</sub> |                                                                                    | $V_A = 0 \text{ V or } 2.4 \text{ V}, V_B = 1.2 \text{ V},$<br>$0 \text{ V} \le V_{CC} \le 1.5 \text{ V}$  | -20           |     | 20  | μA   |

|                      |                                                                                    | $V_A = -1.4 \text{ V}, V_B = 1.2 \text{ V},$<br>$0 \text{ V} \le V_{CC} \le 1.5 \text{ V}$                 | -32           |     | 0   | μA   |

|                      |                                                                                    | $V_B = 3.8 \text{ V}, V_A = 1.2 \text{ V},$<br>$0 \text{ V} \le V_{CC} \le 1.5 \text{ V}$                  | 0             |     | 32  | μA   |

| I <sub>B (OFF)</sub> | Receiver or Transceiver Power-off Input Current                                    | $V_B = 0 \text{ V or } 2.4 \text{ V}, V_A = 1.2 \text{ V}, $<br>$0 \text{ V} \le V_{CC} \le 1.5 \text{ V}$ | -20           |     | 20  | μA   |

|                      |                                                                                    | $V_B = -1.4 \text{ V}, V_A = 1.2 \text{ V},$ $0 \text{ V} \le V_{CC} \le 1.5 \text{ V}$                    | -32           |     | 0   | μA   |

| lances:              | Receiver Input or Transceiver                                                      | $V_A = V_B, \ 0 \ V \le V_{CC} \le 1.5 \ V,$                                                               | -4            |     | 4   | ^    |

| I <sub>AB(OFF)</sub> | Power-off Differential Input Current (I <sub>A</sub> – I <sub>B</sub> )            | -1.4 ≤ V <sub>A</sub> ≤ 3.8 V                                                                              | <del>-4</del> |     | 4   | μA   |

| Driver E             | lectrical Characteristics                                                          |                                                                                                            |               |     |     |      |

www.3peak.com 7 / 20 CA20230901A0

| Parameter                  |                                                                               | Conditions                                                                                                  | Min                  | Тур | Max                 | Unit |

|----------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------|-----|---------------------|------|

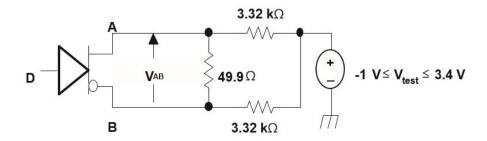

| V <sub>AB</sub>            | Differential Output Voltage Magnitude                                         |                                                                                                             | 480                  |     | 650                 | mV   |

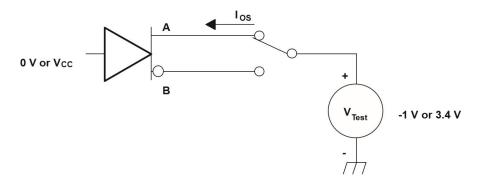

| $\Delta  V_{AB} $          | Change in Differential Output Voltage<br>Magnitude between Logic States       | See Figure 1                                                                                                | -50                  |     | 50                  | mV   |

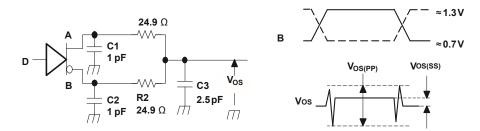

| Vos(ss)                    | Steady-state Common-Mode Output Voltage                                       |                                                                                                             | 0.8                  |     | 1.2                 | V    |

| $\Delta V_{\text{OS(SS)}}$ | Change in Steady-State Common-<br>Mode Output Voltage Between Logic<br>States | See Figure 2                                                                                                | -50                  |     | 50                  | mV   |

| V <sub>OS(PP)</sub>        | Peak-to-peak Common-Mode Output Voltage                                       |                                                                                                             |                      |     | 150                 | mV   |

| V <sub>A(OC)</sub>         | Maximum Steady-State Open-Circuit Output Voltage                              | Saa Figura 6                                                                                                | 0                    |     | VCC                 | V    |

| $V_{B(OC)}$                | Maximum Steady-State Open-Circuit Output Voltage                              | See Figure 6                                                                                                | 0                    |     | VCC                 | ٧    |

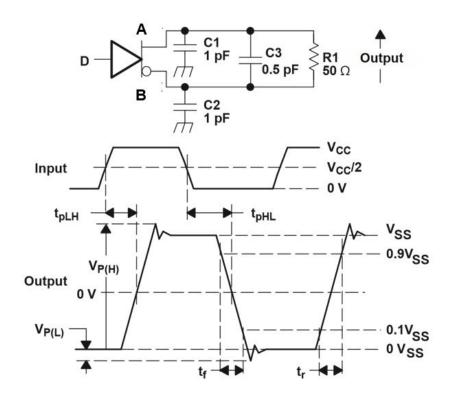

| $V_{P(H)}$                 | Voltage Overshoot, Low-to-High-<br>Level Output                               | 0 5                                                                                                         |                      |     | 1.2 V <sub>SS</sub> | ٧    |

| $V_{P(L)}$                 | Voltage Overshoot, High-to-Low-<br>Level Output                               | See Figure 4                                                                                                | -0.2 V <sub>SS</sub> |     |                     | V    |

| I <sub>IH</sub>            | High-Level Input Current (D, DE)                                              | V <sub>IH</sub> = 2 V                                                                                       | 0                    |     | 10                  | μA   |

| I <sub>IL</sub>            | Low-Level Input Current (D, DE)                                               | V <sub>IL</sub> = 0.8 V                                                                                     | 0                    |     | 10                  | μA   |

| los                        | Differential Short-Circuit Output<br>Current Magnitude                        | See Figure 3                                                                                                |                      |     | 75                  | mA   |

| l <sub>OZ</sub>            | High-Impedance State Output Current (driver only)                             | $-1.4 \text{ V} \le \text{V}_{\text{A}} \text{ or V}_{\text{B}} \le 3.8 \text{ V},$<br>Other output = 1.2 V | -32                  |     | 32                  | μΑ   |

| Driver Sv                  | witching Characteristics                                                      |                                                                                                             |                      |     |                     |      |

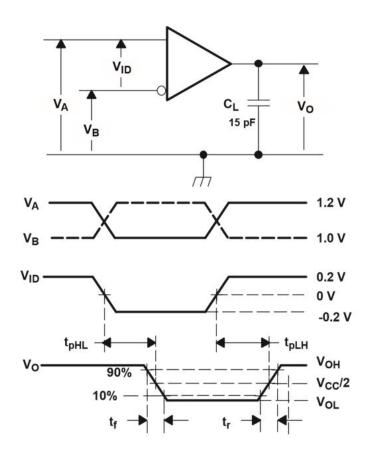

| t <sub>PLH</sub>           | Propagation Delay Time, Low-To-<br>High-Level Output <sup>(1)</sup>           |                                                                                                             |                      | 2.8 |                     | ns   |

| t <sub>PHL</sub>           | Propagation Delay Time, High-To-<br>Low-Level Output <sup>(1)</sup>           |                                                                                                             |                      | 3.2 |                     | ns   |

| t <sub>r</sub>             | Differential Output Signal Rise Time                                          | See Figure 4                                                                                                |                      | 1.6 |                     | ns   |

| t <sub>f</sub>             | Differential Output Signal Fall Time (1)                                      |                                                                                                             |                      | 1.8 |                     | ns   |

| t <sub>sk(p)</sub>         | Pulse Skew ( t <sub>PHL</sub> - t <sub>PLH</sub>  ) <sup>(1)</sup>            |                                                                                                             |                      | 433 |                     | ps   |

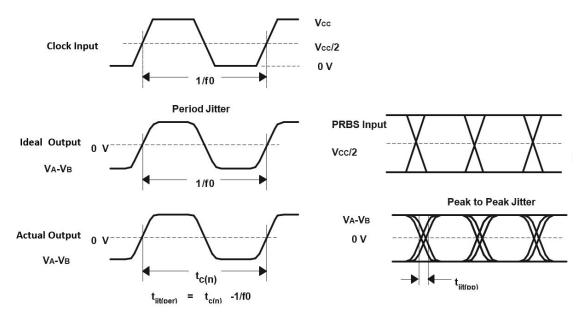

| t <sub>jit(per)</sub>      | Period Jitter, rms (1 standard deviation) <sup>(1)</sup>                      | 100 MHz clock input                                                                                         |                      | 1   |                     | ps   |

|                                  | Parameter                                                            | Conditions                                                        | Min  | Тур | Max  | Unit |

|----------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------|------|-----|------|------|

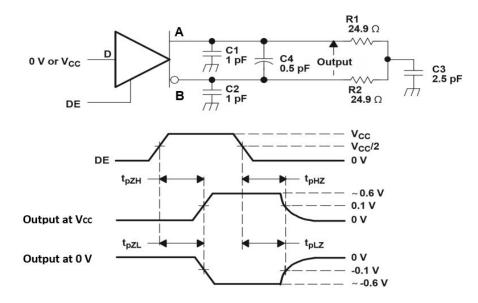

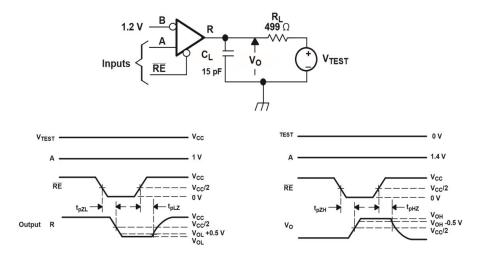

| t <sub>PHZ</sub>                 | Disable Time, High-Level-To-High-<br>Impedance Output <sup>(1)</sup> |                                                                   |      | 4.5 |      | ns   |

| t <sub>PLZ</sub>                 | Disable Time, Low-Level-To-High-<br>Impedance Output <sup>(1)</sup>  | Soo Eiguro E                                                      |      | 3.2 |      | ns   |

| t <sub>PZH</sub>                 | Enable Time, High-Impedance-To-<br>High-Level Output <sup>(1)</sup>  | See Figure 5                                                      |      | 3.2 |      | ns   |

| t <sub>PZL</sub>                 | Enable Time, High-Impedance-To-<br>Low-Level Output <sup>(1)</sup>   |                                                                   |      | 5   |      | ns   |

| Receiver                         | Electrical Characteristics                                           |                                                                   |      |     | _    |      |

| V <sub>IT+</sub>                 | Positive-Going Differential Input Voltage Threshold                  |                                                                   |      |     | 150  | mV   |

| V <sub>IT</sub> -                | Negative-Going Differential Input<br>Voltage Threshold               | See Figure 8 and Table 1 and Table 2                              | 50   |     |      | mV   |

| V <sub>HYS</sub>                 | Differential Input Voltage Hysteresis, $(V_{IT+}-V_{IT})^{(1)}$      |                                                                   |      | 0   |      | mV   |

| V <sub>OH</sub>                  | High-Level Output Voltage                                            | I <sub>OH</sub> = -8 mA                                           | 2.4  |     |      | V    |

| $V_{\text{OL}}$                  | Low-Level Output Voltage                                             | I <sub>OL</sub> = 8 mA                                            |      |     | 0.4  | V    |

| I <sub>IH</sub>                  | High-Level Input Current (RE)                                        | V <sub>IH</sub> = 2 V                                             | -10  |     | 0    | μA   |

| I <sub>IL</sub>                  | Low-Level Input Current (RE)                                         | V <sub>IL</sub> = 0.8 V                                           | -10  |     | 0    | μA   |

| C <sub>A</sub> or C <sub>B</sub> | Input Capacitance (1)                                                | V <sub>I</sub> = 0.4 sin(30E6πt) + 0.5 V,<br>Other input at 1.2 V |      | 7   |      | pF   |

| С <sub>АВ</sub>                  | Differential Input Capacitance (1)                                   | V <sub>AB</sub> = 0.4 sin(30E6πt) V                               |      | 7   |      | pF   |

| C <sub>A/B</sub>                 | Input Capacitance Balance, (C <sub>A</sub> /C <sub>B</sub> ) (1)     |                                                                   | 0.99 |     | 1.01 |      |

| Receiver                         | Switching Characteristics                                            |                                                                   |      |     |      |      |

| t <sub>pLH</sub>                 | Propagation Delay Time, Low-to-<br>High-Level Output <sup>(1)</sup>  |                                                                   | 4    | 6   | 8    | ns   |

| t <sub>pHL</sub>                 | Propagation Delay Time, High-to-<br>Low-Level Output <sup>(1)</sup>  | C <sub>L</sub> = 15 pF, See Figure 9                              | 4    | 6   | 8    | ns   |

| t <sub>r</sub>                   | Output Signal Rise Time                                              | · · · · · · · · · · · · · · · · · ·                               |      | 0.9 | 2.3  | ns   |

| t <sub>f</sub>                   | Output Signal Fall Time                                              | ]                                                                 |      | 0.8 | 2.3  | ns   |

| t <sub>sk(p)</sub>               | Pulse Skew ( t <sub>phl</sub> - t <sub>plh</sub>  )                  |                                                                   |      | 200 |      | ps   |

| t <sub>jit(per)</sub>            | Period Jitter, rms (1 standard deviation) (1)                        | 100 MHz clock input                                               |      | 1   |      | ps   |

www.3peak.com 9 / 20 CA20230901A0

| Parameter        |                                                                      | Conditions    |  | Тур | Max | Unit |

|------------------|----------------------------------------------------------------------|---------------|--|-----|-----|------|

| t <sub>pHZ</sub> | Disable Time, High-Level-to-High-<br>Impedance Output <sup>(1)</sup> |               |  | 4.5 |     | ns   |

| $t_{pLZ}$        | Disable Time, Low-Level-to-High-<br>Impedance Output <sup>(1)</sup>  | See Figure 10 |  | 3.5 |     | ns   |

| t <sub>pZH</sub> | Enable Time, High-Impedance-to-<br>High-Level Output <sup>(1)</sup>  |               |  | 7.5 |     | ns   |

| $t_{pZL}$        | Enable Time, High-Impedance-to-<br>Low-Level Output <sup>(1)</sup>   |               |  | 3.5 |     | ns   |

<sup>(1)</sup> Spec data is provided by lab bench test, NOT test in production.

www.3peak.com 10 / 20 CA20230901A0

### **Test Circuits, Configurations and Waveforms**

Figure 1. Differential Output Voltage Test Circuit

Figure 2. Test Circuit and Definitions for the Driver Common-Mode Output Voltage

Figure 3. Driver Short-Circuit Test Circuit

www.3peak.com 11 / 20 CA20230901A0

Figure 4. Driver Test Circuit, Timing, and Voltage Definitions for the Differential Output Signal

Figure 5. Driver Enable and Disable Time Circuit and Definitions

www.3peak.com 12 / 20 CA20230901A0

Figure 6. Maximum Steady State Output Voltage

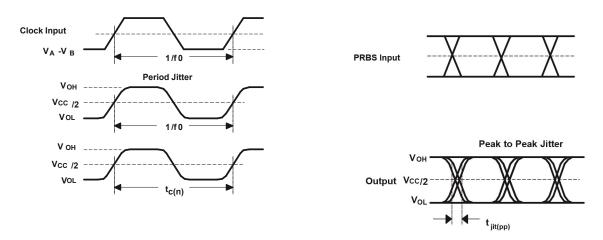

Figure 7. Driver Jitter Measurement Waveforms

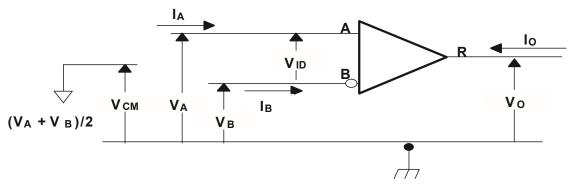

Figure 8. Receiver Voltage and Current Definitions

www.3peak.com 13 / 20 CA20230901A0

Figure 9. Receiver Timing Test Circuit and Waveforms

Figure 10. Receiver Timing Test Circuit and Waveforms

www.3peak.com 14 / 20 CA20230901A0

Figure 11. Receiver Jitter Measurement Waveforms

www.3peak.com 15 / 20 CA20230901A0

## **Detailed Description**

#### Overview

The TPT9H221A is a 3.3-V Multipoint-Low-Voltage Differential (M-LVDS) line driver and receiver, which can operate at signaling rates up to 200 Mbps. Driver outputs and receiver inputs are protected against  $\pm 8$ -kV ESD strikes without latch-up. The driver output has been designed to support multipoint buses presenting loads as low as 30  $\Omega$ , and incorporates controlled transition times to allow for stubs off of the backbone transmission line.

www.3peak.com 16 / 20 CA20230901A0

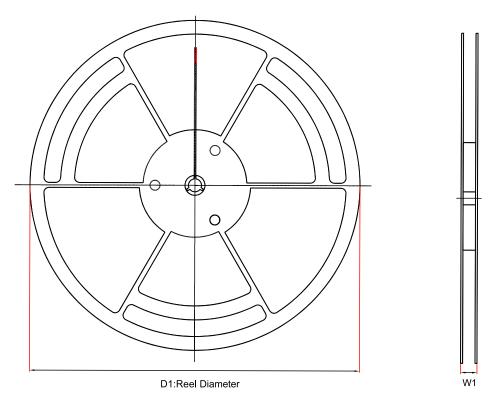

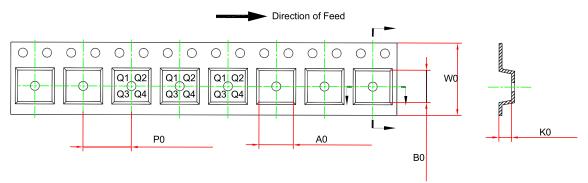

# **Tape and Reel Information**

| Order Number         | Package | D1 (mm) | W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P0 (mm) | W0 (mm) | Pin1<br>Quadrant |

|----------------------|---------|---------|---------|---------|---------|---------|---------|---------|------------------|

| TPT9H221A-<br>SO1R-S | SOP8    | 330.0   | 17.6    | 6.5     | 5.4     | 2.0     | 8.0     | 12.0    | Q1               |

www.3peak.com 17 / 20 CA20230901A0

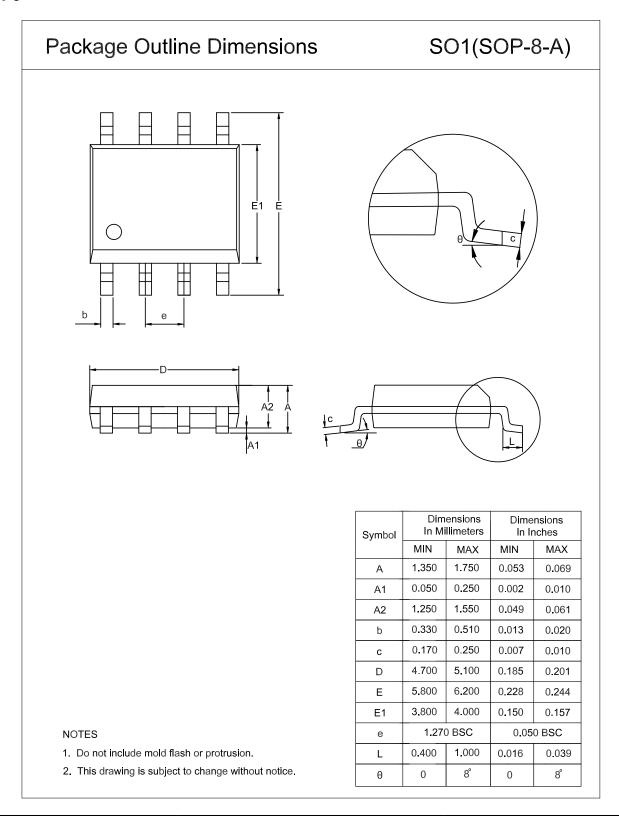

## **Package Outline Dimensions**

#### SOP8

#### **Order Information**

| Order Number     | Operating Temperature Range | Package | Marking Information | MSL | Transport Media, Quantity | Eco Plan |

|------------------|-----------------------------|---------|---------------------|-----|---------------------------|----------|

| TPT9H221A-SO1R-S | −40 to 85°C                 | SOP8    | H221A               | 1   | Tape and Reel, 4000       | Green    |

**Green**: 3PEAK defines "Green" to mean RoHS compatible and free of halogen substances.

www.3peak.com 19 / 20 CA20230901A0

#### IMPORTANT NOTICE AND DISCLAIMER

Copyright<sup>©</sup> 3PEAK 2012-2024. All rights reserved.

**Trademarks.** Any of the 思瑞浦 or 3PEAK trade names, trademarks, graphic marks, and domain names contained in this document /material are the property of 3PEAK. You may NOT reproduce, modify, publish, transmit or distribute any Trademark without the prior written consent of 3PEAK.

**Performance Information.** Performance tests or performance range contained in this document/material are either results of design simulation or actual tests conducted under designated testing environment. Any variation in testing environment or simulation environment, including but not limited to testing method, testing process or testing temperature, may affect actual performance of the product.

**Disclaimer.** 3PEAK provides technical and reliability data (including data sheets), design resources (including reference designs), application or other design recommendations, networking tools, security information and other resources "As Is". 3PEAK makes no warranty as to the absence of defects, and makes no warranties of any kind, express or implied, including without limitation, implied warranties as to merchantability, fitness for a particular purpose or non-infringement of any third-party's intellectual property rights. Unless otherwise specified in writing, products supplied by 3PEAK are not designed to be used in any life-threatening scenarios, including critical medical applications, automotive safety-critical systems, aviation, aerospace, or any situations where failure could result in bodily harm, loss of life, or significant property damage. 3PEAK disclaims all liability for any such unauthorized use.

www.3peak.com 20 / 20 CA20230901A0