## Features

- I<sup>2</sup>C-bus to 16-bit GPIO Expander

- Operating Power Supply Voltage from 1.65 V to 3.6 V

- Low Standby Current Consumption:

- 1.5 μA (typical at 3.3 V V<sub>CC</sub>)

- 400-kHz Fast-mode I<sup>2</sup>C-bus

- 5-V Tolerant I/Os

- Internal Power-on Reset

- Open-drain Active LOW Interrupt Output ( INT )

- Configurable Slave Address with 2 Address Pins

- Latch-Up Performance exceeds 200 mA per JESD 78

- ESD Protection Exceeds JESD 22

- ±4000-V Human Body Model

- ±1500-V Charged Device Model

- AEC Q100: Automotive Grade 1

## Applications

- Automotive ASAS, Infotainment,

- Automotive Body Electronics, EV/HEV

- Servers/Storages/Routers (Telecom Switching Equipment)

- Personal Computers

## Description

The TPT29539Q is a 16-bit GPIO expander with interrupt and weak pull-up resistors for  $l^2$ C-bus applications. The power supplier voltage ranges from 1.65 V to 3.6 V, allowing for the TPT29539Q to interconnect with 1.8-V microcontrollers.

The TPT29539Q contains 16-bit Input and Output. The open-drain interrupt ( $\overline{\rm INT}$ ) output is changeable when any input state changes from its related register state. The device is used to indicate the system master that an input state has changed. ( $\overline{\rm INT}$ ) can be connected to the interrupt input of a microcontroller. The TPT29539Q can remain a simple slave device. The power-on reset sets the registers to their default values and initializes the device state machine. The TPT29539Q also has a hardware  $\overline{\rm INT}$  pin to reset the device to its default state.

All input/output pins do not have internal pull-up resistors, thus the device can save power consumption as communicating with external I/Os. Two hardware pins (A0, A1) select the fixed  $I^2$ C-bus address and allow up to eight devices to share the same  $I^2$ C-bus.

The TPT29539Q is available in the TSSOP24 package, and is characterized from  $-40^{\circ}$ C to  $+125^{\circ}$ C to meet automotive application requirements.

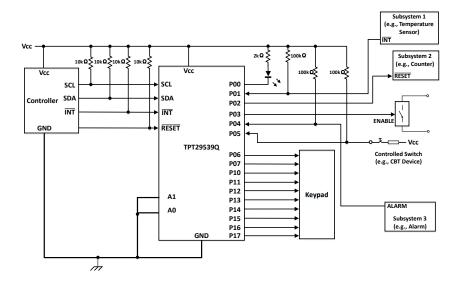

# **Typical Application Circuit**

# **Table of Contents**

| Applications       1         Description       1         Typical Application Circuit       1         Revision History       3         Pin Configuration and Functions       4         Specifications       6         Absolute Maximum Ratings (1)       6         ESD, Electrostatic Discharge Protection       6         Recommended Operating Conditions       7         Thermal Information       7         Electrical Characteristics       8         Electrical Characteristics (Continued)       9         I <sup>2</sup> C Interface Timing Requirements (1)       10         Switching Characteristics       11         Parameter Measurement Waveforms       11         Typical Performance Characteristics       12         Detailed Description       13         Overview       13         Functional Block Diagram       13         Functional Molementation       17         Application Information       17         Application                                             | Features                                                      | 1  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----|

| Typical Application Circuit         1           Revision History         3           Pin Configuration and Functions         4           Specifications         6           Absolute Maximum Ratings (1)         6           ESD, Electrostatic Discharge Protection         6           Recommended Operating Conditions         7           Thermal Information         7           Telectrical Characteristics         8           Electrical Characteristics (Continued)         9           I <sup>2</sup> C Interface Timing Requirements (1)         10           Switching Characteristics         11           Typical Performance Characteristics         12           Detailed Description         13           Overview         13           Functional Block Diagram         13           Functional Block Diagram         14           Device Address         14           Application Information         17           Typical Application         18           Layout Guideline         18           Layout Guideline         18           Layout Example         18           Topolication Information         21           Topolication Information         21           Topolication | Applications                                                  | 1  |

| Avision History       3         Pin Configuration and Functions       4         Specifications       6         Absolute Maximum Ratings <sup>(1)</sup> 6         ESD, Electrostatic Discharge Protection       6         Recommended Operating Conditions       7         Thermal Information       7         Electrical Characteristics       8         Electrical Characteristics (Continued)       9         I <sup>2</sup> C Interface Timing Requirements <sup>(1)</sup> 10         Switching Characteristics       11         Parameter Measurement Waveforms       11         Typical Performance Characteristics       12         Detailed Description       13         Overview       13         Facture Description       14         Device Address       14         Application and Implementation       17         Application and Implementation       17         Application and Implementation       17         Application and Implementation       17         Typical Application       18         Layout Guideline       18         Layout Guideline       18         Layout Guideline       18         Captare and Reel Information       20                                         | Description                                                   | 1  |

| Pin Configuration and Functions.       4         Specifications       6         Absolute Maximum Ratings <sup>(1)</sup> 6         ESD, Electrostatic Discharge Protection       6         Recommended Operating Conditions       7         Thermal Information       7         Electrical Characteristics       8         Electrical Characteristics (Continued)       9         I <sup>2</sup> C Interface Timing Requirements <sup>(1)</sup> 10         Switching Characteristics       11         Parameter Measurement Waveforms       11         Typical Performance Characteristics       12         Detailed Description       13         Overview       13         Feature Description       14         Device Address       14         Application Information       17         Application Information       17         rypical Application       18         Layout Guideline       18         Layout Guideline       18         Layout Example       18         Tapout Example       12         Device Address       21         Typical Application       17         Functional Block Diagram       17         Application Information       1                                               | Typical Application Circuit                                   | 1  |

| Specifications       6         Absolute Maximum Ratings <sup>(1)</sup> 6         ESD, Electrostatic Discharge Protection       6         Recommended Operating Conditions       7         Thermal Information       7         Electrical Characteristics       8         Electrical Characteristics (Continued)       9         I <sup>2</sup> C Interface Timing Requirements <sup>(1)</sup> 10         Switching Characteristics       11         Parameter Measurement Waveforms       11         Typical Performance Characteristics       12         Detailed Description       13         Overview       13         Feature Description       14         Device Address       14         Application Information       17         Application Information       17         Typical Application       17         Application Information       17         Typical Application       18         Layout Guideline       18         Layout Example       18         Tape and Reel Information       20         Package Outline Dimensions       21         TSSOP24-A       21         Order Information       22 <th>Revision History</th> <th>3</th>                                                 | Revision History                                              | 3  |

| Absolute Maximum Ratings <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -                                                             |    |

| ESD, Electrostatic Discharge Protection.       6         Recommended Operating Conditions.       7         Thermal Information.       7         Electrical Characteristics.       8         Electrical Characteristics (Continued).       9         I <sup>2</sup> C Interface Timing Requirements <sup>(1)</sup> 10         Switching Characteristics.       11         Parameter Measurement Waveforms.       11         Typical Performance Characteristics.       12         Detailed Description.       13         Overview.       13         Functional Block Diagram.       13         Feature Description.       14         Device Address.       14         Application and Implementation.       17         Application Information       17         Typical Application.       18         Layout Guideline.       18         Layout Example.       18         Tape and Reel Information.       20         Package Outline Dimensions.       21         TSSOP24-A.       21         Order Information.       22                                                                                                                                                                               | Specifications                                                | 6  |

| Recommended Operating Conditions.       7         Thermal Information.       7         Electrical Characteristics       8         Electrical Characteristics (Continued).       9         I <sup>2</sup> C Interface Timing Requirements <sup>(1)</sup> 10         Switching Characteristics       11         Parameter Measurement Waveforms.       11         Typical Performance Characteristics.       12         Detailed Description.       13         Overview.       13         Functional Block Diagram.       13         Feature Description.       14         Device Address.       14         Application Information       17         Typical Application.       17         Application Information       17         Typical Application.       18         Layout Guideline.       18         Layout Example.       18         Cape and Reel Information.       20         Package Outline Dimensions.       21         TSSOP24-A.       21         Order Information.       22                                                                                                                                                                                                            | Absolute Maximum Ratings <sup>(1)</sup>                       | 6  |

| Thermal Information       7         Electrical Characteristics       8         Electrical Characteristics (Continued)       9         I <sup>2</sup> C Interface Timing Requirements <sup>(1)</sup> 10         Switching Characteristics       11         Parameter Measurement Waveforms       11         Typical Performance Characteristics       12         Detailed Description       13         Overview       13         Fautre Description       13         Feature Description       14         Device Address       14         Application and Implementation       17         Application Information       17         Typical Application       18         Layout Guideline       18         Layout Example       18         Tape and Reel Information       20         Package Outline Dimensions       21         TSSOP24-A       21         Order Information       22                                                                                                                                                                                                                                                                                                                   | ESD, Electrostatic Discharge Protection                       | 6  |

| Electrical Characteristics       8         Electrical Characteristics (Continued).       9         I <sup>2</sup> C Interface Timing Requirements <sup>(1)</sup> 10         Switching Characteristics       11         Parameter Measurement Waveforms       11         Typical Performance Characteristics       12         Detailed Description       13         Overview       13         Functional Block Diagram       13         Feature Description       14         Device Address       14         Application and Implementation       17         Application Information       17         Typical Application       18         Layout Guideline       18         Layout Example       18         Sage Outline Dimensions       21         TSSOP24-A       21         Order Information       22                                                                                                                                                                                                                                                                                                                                                                                              | Recommended Operating Conditions                              | 7  |

| Electrical Characteristics (Continued).       9         I <sup>2</sup> C Interface Timing Requirements <sup>(1)</sup> 10         Switching Characteristics.       11         Parameter Measurement Waveforms.       11         Typical Performance Characteristics.       12         Detailed Description.       13         Overview.       13         Functional Block Diagram.       13         Feature Description.       14         Device Address.       14         Application and Implementation.       17         Application Information       17         Typical Application.       18         Layout Guideline.       18         Layout Example.       18         Tape and Reel Information.       20         Package Outline Dimensions.       21         TSSOP24-A.       21                                                                                                                                                                                                                                                                                                                                                                                                               | Thermal Information                                           | 7  |

| I <sup>2</sup> C Interface Timing Requirements <sup>(1)</sup> 10         Switching Characteristics       11         Parameter Measurement Waveforms       11         Typical Performance Characteristics       12         Detailed Description       13         Overview       13         Functional Block Diagram       13         Feature Description       14         Device Address       14         Application and Implementation       17         Application Information       17         Typical Application       18         Layout Guideline       18         Layout Example       18         TSSOP24-A       21         Order Information       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Electrical Characteristics                                    | 8  |

| Switching Characteristics       11         Parameter Measurement Waveforms       11         Typical Performance Characteristics       12         Detailed Description       13         Overview       13         Functional Block Diagram       13         Feature Description       14         Device Address       14         Application and Implementation       17         Application Information       17         Typical Application       18         Layout Guideline       18         Layout Example       18         Tase and Reel Information       20         Package Outline Dimensions       21         TSSOP24-A       21         Drder Information       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Electrical Characteristics (Continued)                        | 9  |

| Parameter Measurement Waveforms       11         Typical Performance Characteristics       12         Detailed Description       13         Overview       13         Functional Block Diagram       13         Feature Description       14         Device Address       14         Application and Implementation       17         Application Information       17         Typical Application       17         Application Information       17         Typical Application       17         Application Information       17         Typical Application       17         Tayout       18         Layout Guideline       18         Layout Example       18         Tape and Reel Information       20         Package Outline Dimensions       21         TSSOP24-A       21         Order Information       22                                                                                                                                                                                          | I <sup>2</sup> C Interface Timing Requirements <sup>(1)</sup> | 10 |

| Typical Performance Characteristics.       12         Detailed Description.       13         Overview.       13         Functional Block Diagram.       13         Feature Description.       14         Device Address.       14         Application and Implementation.       17         Application Information       17         Typical Application.       17         Application Information       17         Typical Application.       18         Layout Guideline.       18         Layout Example.       18         Tape and Reel Information.       20         Package Outline Dimensions.       21         TSSOP24-A.       21         Order Information.       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Switching Characteristics                                     | 11 |

| Detailed Description       13         Overview       13         Functional Block Diagram       13         Feature Description       14         Device Address       14         Application and Implementation       17         Application Information       17         Typical Application       17         ayout       18         Layout Guideline       18         Tape and Reel Information       20         Package Outline Dimensions       21         Order Information       21         Order Information       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Parameter Measurement Waveforms                               | 11 |

| Overview.       13         Functional Block Diagram.       13         Feature Description.       14         Device Address.       14         Application and Implementation.       17         Application Information       17         Typical Application.       17         ayout.       18         Layout Guideline.       18         Layout Example.       18         Tape and Reel Information.       20         Package Outline Dimensions.       21         Drder Information.       21         Order Information.       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Typical Performance Characteristics                           | 12 |

| Functional Block Diagram       13         Feature Description       14         Device Address       14         Application and Implementation       17         Application Information       17         Typical Application       17         ayout       18         Layout Guideline       18         Layout Example       18         Fape and Reel Information       20         Package Outline Dimensions       21         Drder Information       21         Order Information       21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Detailed Description                                          | 13 |

| Feature Description       14         Device Address       14         Application and Implementation       17         Application Information       17         Typical Application       17         .ayout       18         Layout Guideline       18         Layout Example       18         Fape and Reel Information       20         Package Outline Dimensions       21         TSSOP24-A       21         Order Information       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Overview                                                      | 13 |

| Device Address       14         Application and Implementation       17         Application Information       17         Typical Application       17         .ayout       18         Layout Guideline       18         Layout Example       18         Tape and Reel Information       20         Package Outline Dimensions       21         TSSOP24-A       21         Order Information       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Functional Block Diagram                                      | 13 |

| Application and Implementation.17Application Information17Typical Application.17.ayout.18Layout Guideline.18Layout Example.18Fape and Reel Information.20Package Outline Dimensions.21TSSOP24-A.21Order Information.22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Feature Description                                           | 14 |

| Application Information 17   Typical Application 17   ayout 18   Layout Guideline 18   Layout Example 18   Tape and Reel Information 20   Package Outline Dimensions 21   TSSOP24-A 21   Order Information 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Device Address                                                | 14 |

| Typical Application       17         .ayout       18         Layout Guideline       18         Layout Example       18         Fape and Reel Information       20         Package Outline Dimensions       21         TSSOP24-A       21         Order Information       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Application and Implementation                                | 17 |

| Layout       18         Layout Guideline       18         Layout Example       18         Fape and Reel Information       20         Package Outline Dimensions       21         TSSOP24-A       21         Order Information       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Application Information                                       | 17 |

| Layout Guideline.       18         Layout Example.       18         Tape and Reel Information.       20         Package Outline Dimensions.       21         TSSOP24-A.       21         Order Information.       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Typical Application                                           | 17 |

| Layout Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Layout                                                        | 18 |

| Fape and Reel Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Layout Guideline                                              | 18 |

| Package Outline Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Layout Example                                                |    |

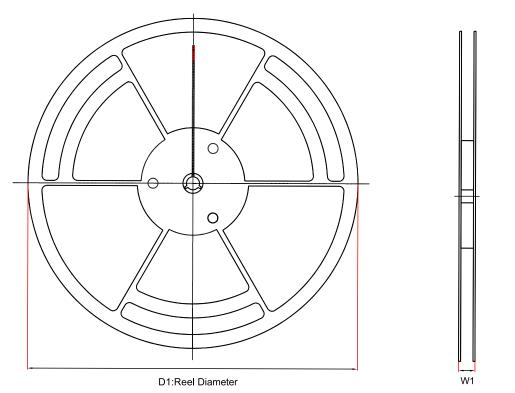

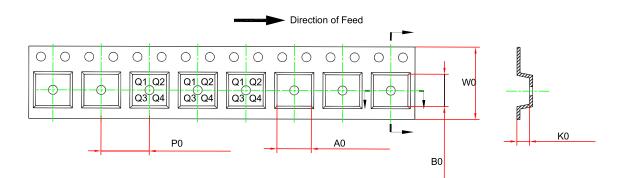

| TSSOP24-A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Tape and Reel Information                                     | 20 |

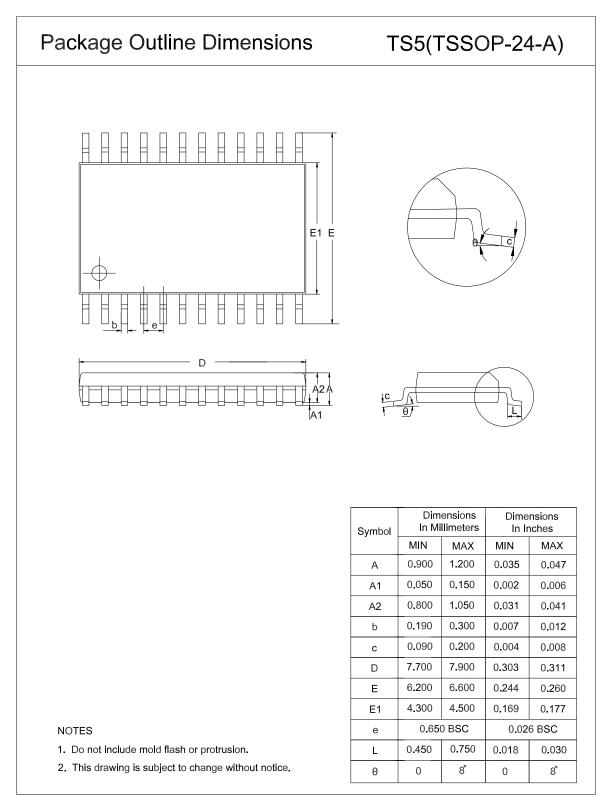

| Order Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Package Outline Dimensions                                    | 21 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | TSSOP24-A                                                     | 21 |

| MPORTANT NOTICE AND DISCLAIMER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Order Information                                             | 22 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | IMPORTANT NOTICE AND DISCLAIMER                               | 23 |

# **Revision History**

| Date       | Revision | Notes                                                                                      |

|------------|----------|--------------------------------------------------------------------------------------------|

| 2023-12-18 | Rev.A.0  | Released version                                                                           |

| 2024-02-07 | Rev.A.1  | Updated Typical Application Circuit                                                        |

| 2024-02-20 | Rev.A.2  | Updated the V <sub>OH</sub> /I <sub>OL</sub> /I <sub>CC</sub> test condition               |

| 2024-03-31 | Rev.A.3  | Updated the standby $I_{CC}$ as input low condition                                        |

| 2024-06-26 | Rev.A.4  | Added the Reset timing and updated the tps spec                                            |

| 2024-08-12 | Rev.A.5  | Corrected the typo of the K0 value of 1.6 to 1.25 in the Tape and Reel Information section |

# **Pin Configuration and Functions**

|      | TSSOP24 Packag<br>Top View | je |         |

|------|----------------------------|----|---------|

|      |                            |    |         |

|      | $^{1}$                     | 24 |         |

| A1   | 2                          | 23 | SDA SDA |

|      | 3                          | 22 |         |

| P0_0 | 4                          | 21 | A0      |

| P0_1 | 5                          | 20 | P1_7    |

| P0_2 | 6                          | 19 | P1_6    |

| P0_3 | 7                          | 18 | P1_5    |

| P0_4 | 8                          | 17 | P1_4    |

| P0_5 | 9                          | 16 | P1_3    |

| P0_6 | 10                         | 15 | P1_2    |

| P0_7 | 11                         | 14 | P1_1    |

|      | 12                         | 13 | P1_0    |

| 0.10 |                            | 10 |         |

TPT29539Q

#### Table 1. Pin Functions: TPT29539Q

| Pin No. | Name  | I/O    | Description                                                                         |

|---------|-------|--------|-------------------------------------------------------------------------------------|

| 21      | A0    | Input  | Address input 0. Connect directly to VCC or ground                                  |

| 2       | A1    | Input  | Address input 1. Connect directly to VCC or ground                                  |

| 3       | RESET | Input  | RESET input, active LOW                                                             |

| 12      | GND   | GND    | Ground                                                                              |

| 1       | ĪNT   | Output | Interrupt output. Connect to VCC through a pull-up resistor                         |

| 4       | P0_0  | I/O    | P-port I/O. Push-pull design structure. At power on, P0_0 is configured as an input |

| 5       | P0_1  | I/O    | P-port I/O. Push-pull design structure. At power on, P0_1 is configured as an input |

| 6       | P0_2  | I/O    | P-port I/O. Push-pull design structure. At power on, P0_2 is configured as an input |

| 7       | P0_3  | I/O    | P-port I/O. Push-pull design structure. At power on, P0_3 is configured as an input |

| 8       | P0_4  | I/O    | P-port I/O. Push-pull design structure. At power on, P0_4 is configured as an input |

| 9       | P0_5  | I/O    | P-port I/O. Push-pull design structure. At power on, P0_5 is configured as an input |

| 10      | P0_6  | I/O    | P-port I/O. Push-pull design structure. At power on, P0_6 is configured as an input |

| 11      | P0_7  | I/O    | P-port I/O. Push-pull design structure. At power on, P0_7 is configured as an input |

| 13      | P1_0  | I/O    | P-port I/O. Push-pull design structure. At power on, P1_0 is configured as an input |

| 14      | P1_1  | I/O    | P-port I/O. Push-pull design structure. At power on, P1_1 is configured as an input |

| 15      | P1_2  | I/O    | P-port I/O. Push-pull design structure. At power on, P1_2 is configured as an input |

| 16      | P1_3  | I/O    | P-port I/O. Push-pull design structure. At power on, P1_3 is configured as an input |

| 17      | P1_4  | I/O    | P-port I/O. Push-pull design structure. At power on, P1_4 is configured as an input |

| 18      | P1_5  | I/O    | P-port I/O. Push-pull design structure. At power on, P1_5 is configured as an input |

| 19      | P1_6  | I/O    | P-port I/O. Push-pull design structure. At power on, P1_6 is configured as an input |

| 20      | P1_7  | I/O    | P-port I/O. Push-pull design structure. At power on, P1_7 is configured as an input |

| Pin No. | Name | I/O    | Description                                                 |

|---------|------|--------|-------------------------------------------------------------|

| 22      | SCL  | Input  | Serial clock bus. Connect to VCC through a pull-up resistor |

| 23      | SDA  | I/O    | Serial data bus. Connect to VCC through a pull-up resistor  |

| 24      | VCC  | Supply | Supply voltage                                              |

# **Specifications**

### Absolute Maximum Ratings <sup>(1)</sup>

|                  | Parameter                                               | Min  | Max  | Unit |

|------------------|---------------------------------------------------------|------|------|------|

| Vcc              | Supply Voltage                                          | -0.5 | 3.6  | V    |

| VI               | Input Voltage                                           | -0.5 | 3.6  | V    |

| Vo               | Output Voltage                                          | -0.5 | 3.6  | V    |

| I <sub>IK</sub>  | Input Clamp Current, VI < 0                             |      | -20  | mA   |

| loк              | Output Clamp Current, V <sub>O</sub> < 0                |      | -20  | mA   |

| I <sub>IOK</sub> | Input-Output Clamp Current, $V_0 < 0$ or $V_0 > V_{CC}$ |      | ±20  | mA   |

| I <sub>OL</sub>  | Continuous Output Low Current, Vo = 0 to Vcc            |      | 50   | mA   |

| I <sub>OH</sub>  | Continuous Output High Current, $V_0 = 0$ to $V_{CC}$   |      | -50  | mA   |

|                  | Continuous Current through GND                          |      | -250 | mA   |

| Icc              | Continuous Current through V <sub>CC</sub>              |      | 160  | mA   |

| TJ               | Maximum Junction Temperature                            |      | 135  | °C   |

| T <sub>stg</sub> | Storage Temperature                                     | -65  | 150  | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

(2) This data was taken with the JEDEC low effective thermal conductivity test board.

(3) This data was taken with the JEDEC standard multilayer test boards.

### ESD, Electrostatic Discharge Protection

|     | Parameter                | Condition                             | Minimum Level | Unit |

|-----|--------------------------|---------------------------------------|---------------|------|

| НВМ | Human Body Model ESD     | ANSI/ESDA/JEDEC JS-001 (1)            | ±4            | kV   |

| CDM | Charged Device Model ESD | ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ±1.5          | kV   |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### **Recommended Operating Conditions**

Over-operating free-air temperature range (unless otherwise noted).

|                 | Par                                        | rameter                                  | Min                      | Max                      | Unit |

|-----------------|--------------------------------------------|------------------------------------------|--------------------------|--------------------------|------|

| Vcc             | Supply Voltage                             |                                          | 1.65                     | 3.6                      | V    |

|                 | Output IO Voltage                          | P0_7 ~ P0_0, P1_7 ~ P1_0                 | 0                        | 3.6                      | V    |

| VIO             | Input IO Voltage                           | P0_7 ~ P0_0, P1_7 ~ P1_0                 | 0                        | 3.6                      | V    |

|                 | IO Voltage                                 | SCL, SDA, A1, A0, RESET, INT             | 0                        | 3.6                      | V    |

| VIH             |                                            | SCL, SDA                                 | 0.7 ×<br>V <sub>CC</sub> | V <sub>cc</sub>          | V    |

|                 | High-Level Input Voltage                   | RESET, A2 ~ A0, P0_7 ~ P0_0, P1_7 ~ P1_0 | 0.7 ×<br>Vcc             | Vcc                      | V    |

|                 |                                            | SCL, SDA                                 | -0.5                     | 0.3 ×<br>V <sub>CC</sub> | mV   |

| VIL             | Low-Level Input Voltage                    | RESET, A2 ~ A0, P0_7 ~ P0_0, P1_7 ~ P1_0 | -0.5                     | 0.3 ×<br>V <sub>CC</sub> | mV   |

| Іон             | High-Level Output Current                  | P0_7 ~ P0_0, P1_7 ~ P1_0                 |                          | -10                      | mA   |

|                 |                                            | P0_7 ~ P0_0, P1_7 ~ P1_0                 |                          | 25                       | mA   |

| I <sub>OL</sub> | Low-Level Output Current                   | ĪNT, SDA                                 |                          | 6                        | mA   |

| TA              | T <sub>A</sub> Operating Temperature Range |                                          | -40                      | 125                      | °C   |

### Thermal Information

| Package Type | θ <sub>JA</sub> | θ」ϲ | Unit |

|--------------|-----------------|-----|------|

| TSSOP24      | 68              | 21  | °C/W |

### **Electrical Characteristics**

All test conditions:  $V_{CC}$  = 1.65 V ~ 3.6 V,  $T_A$  = -40 ~ +125°C, unless otherwise noted.

|                 | Parameter                                       | Conditions                                                                    | Min | Тур  | Max | Unit |

|-----------------|-------------------------------------------------|-------------------------------------------------------------------------------|-----|------|-----|------|

| Input El        | ectrical Specifications                         |                                                                               |     |      |     |      |

| .,              | Power-on Reset Voltage , $V_{\text{CC}}$ rising | $V_I = V_{CC}$ or GND; $I_0 = 0$ mA                                           |     | 1.25 | 1.5 | V    |

| Vpor            | Power-on Reset Voltage , $V_{CC}$ falling       | VI = Vcc or GND; Io = 0 mA                                                    | 0.7 | 1.2  |     | V    |

|                 | LOW-level Output Current, SDA                   | $V_{OL}$ = 0.4 V; $V_{CC}$ = 1.65 V to 3.6 V                                  | 3   |      |     | mA   |

|                 | LOW-level Output Current, INT                   | $V_{OL}$ = 0.4 V; $V_{CC}$ = 1.65 V to 3.6 V                                  | 3   |      |     | mA   |

|                 |                                                 | V <sub>OL</sub> = 0.5 V; V <sub>CC</sub> = 1.65 V                             | 8   |      |     | mA   |

|                 | LOW-level Output Current, P port                | $V_{OL}$ = 0.5 V; $V_{CC}$ = 2.3 V <sup>(1)</sup>                             | 8   |      |     | mA   |

| IOL             |                                                 | V <sub>OL</sub> = 0.5 V; V <sub>CC</sub> = 3.0 V                              | 8   |      |     | mA   |

|                 | LOW-level Output Current, P port                | V <sub>OL</sub> = 0.7 V; V <sub>CC</sub> = 1.65 V                             | 10  |      |     | mA   |

|                 |                                                 | $V_{OL}$ = 0.7 V; $V_{CC}$ = 2.3 V <sup>(1)</sup>                             | 10  |      |     | mA   |

|                 |                                                 | V <sub>OL</sub> = 0.7 V; V <sub>CC</sub> = 3.0 V                              | 10  |      |     | mA   |

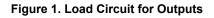

|                 |                                                 | Iон= −8 mA; V <sub>CC</sub> = 1.65 V                                          | 1.2 |      |     | V    |

|                 | HIGH-level Output Voltage, P<br>port            | $I_{OH}$ = -8 mA; $V_{CC}$ = 2.3 V <sup>(1)</sup>                             | 1.8 |      |     | V    |

|                 | port                                            | I <sub>OH</sub> = -8 mA; V <sub>CC</sub> = 3.0 V                              | 2.6 |      |     | V    |

| V <sub>он</sub> |                                                 | Iон= −10 mA; Vcc= 1.65 V                                                      | 1.0 |      |     | V    |

|                 | HIGH-level Output Voltage, P<br>port            | $I_{OH} = -10 \text{ mA}; V_{CC} = 2.3 \text{ V}^{(1)}$                       | 1.7 |      |     | V    |

|                 | port                                            | I <sub>OH</sub> = −10 mA; V <sub>CC</sub> = 3.0 V                             | 2.5 |      |     | V    |

|                 | Input Current: A0, A1, RESET                    | V <sub>CC</sub> = 1.65 V to 3.6 V, V <sub>I</sub> = V <sub>CC</sub> or<br>GND | -1  |      | 1   | μA   |

| lı              | Input Current: SCL, SDA                         | $V_{CC}$ = 1.65 V to 3.6 V, $V_{I}$ = $V_{CC}$ or GND                         | -1  |      | 1   | μA   |

| IIH             | HIGH-level Input Current: P port                | $V_{I}$ = $V_{CC}$ ; $V_{CC}$ = 1.65 V to 3.6 V                               |     |      | 1   | μA   |

| l <sub>IL</sub> | LOW-level Input Current: P Port                 | V <sub>I</sub> = GND; V <sub>CC</sub> = 1.65 V to 3.6 V                       | -1  |      |     | μA   |

(1) Parameters are provided by lab bench tests and design simulation. Not tested in production.

### **Electrical Characteristics (Continued)**

All test conditions:  $V_{CC}$  = 1.65 V ~ 3.6 V,  $T_A$  = -40 ~ +125°C, unless otherwise noted.

|                                | Parameter                | Conditions                                                                                       |                                        | Min | Тур | Max | Unit |

|--------------------------------|--------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------|-----|-----|-----|------|

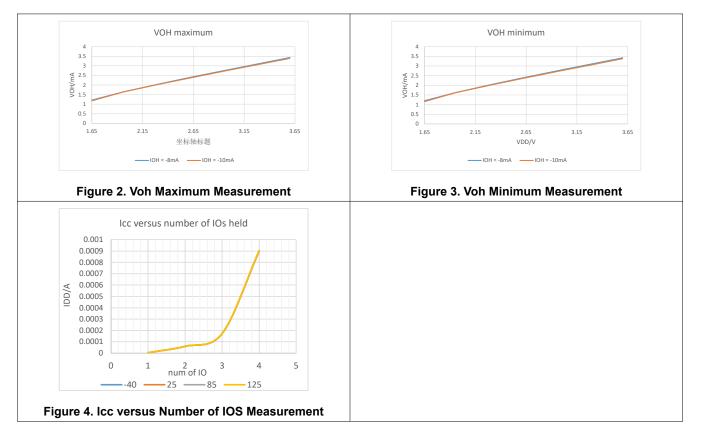

|                                |                          |                                                                                                  | V <sub>CC</sub> = 3.6 V                |     | 9   | 30  | μA   |

|                                |                          | Active mode, IO = 0 mA; I/O<br>= inputs; fSCL = 400 kHz                                          | V <sub>CC</sub> = 2.7 V <sup>(1)</sup> |     | 6.2 | 19  | μA   |

|                                |                          |                                                                                                  | Vcc= 1.95 V                            |     | 4.2 | 11  | μA   |

|                                |                          | Standby Mode, input low, IO                                                                      | V <sub>CC</sub> = 3.6 V                |     | 3.0 | 5.0 | μA   |

| Icc                            | Supply Current           | = 0 mA; I/O = inputs; $fS_{SCL}$ =                                                               | V <sub>CC</sub> = 2.7 V <sup>(1)</sup> |     | 2.0 | 4.5 | μA   |

|                                |                          | 0 kHz                                                                                            | Vcc= 1.95 V                            |     | 1.5 | 3.5 | μA   |

|                                |                          | Standby Mode, input high, IO<br>= 0 mA; I/O = inputs; f <sub>SCL</sub> = 0<br>kHz                | V <sub>CC</sub> = 3.6 V                |     | 1.5 | 5.0 | μA   |

|                                |                          |                                                                                                  | $V_{CC}$ = 2.7 V <sup>(1)</sup>        |     | 1.0 | 4.5 | μA   |

|                                |                          |                                                                                                  | Vcc= 1.95 V                            |     | 0.6 | 3.5 | μA   |

| C <sub>i</sub> <sup>(1)</sup>  | Input Capacitance        | $V_{\text{I}}\text{=}V_{\text{CC}}$ or GND; $V_{\text{CC}}\text{=}$ 1.65 V to 3.6 V $^{(1)}$     |                                        |     | 3   |     | pF   |

| C <sub>io</sub> <sup>(1)</sup> |                          | $V_{\text{I/O}}\text{=}$ $V_{\text{CC}}$ or GND; $V_{\text{D}}\text{=}$ 1.65 V to 3.6 V $^{(1)}$ |                                        |     | 3   |     | pF   |

|                                | Input/Output Capacitance | V <sub>I/O</sub> = V <sub>CC</sub> or GND; V <sub>CC</sub> = 1.65<br>V to 3.6 V <sup>(1)</sup>   |                                        |     | 5   |     | pF   |

(1) Parameters are provided by lab bench tests and design simulation. Not tested in production.

### I<sup>2</sup>C Interface Timing Requirements <sup>(1)</sup>

Over recommended operating free-air temperature range, unless otherwise noted.

| <b>-</b> <i></i>    |                                                          |                                             | Standa | Standard Mod |                                      | Fast Mode |      |

|---------------------|----------------------------------------------------------|---------------------------------------------|--------|--------------|--------------------------------------|-----------|------|

|                     | Description                                              | Conditions                                  | Min    | Max          | Min                                  | Max       | Unit |

| fscl                | I <sup>2</sup> C clock frequency                         |                                             | 0      | 100          | 0                                    | 400       | kHz  |

| tsch                | I <sup>2</sup> C clock high time                         |                                             | 4      |              | 0.6                                  |           | μs   |

| tscl                | I <sup>2</sup> C clock low time                          |                                             | 4.7    |              | 1.3                                  |           | μs   |

| tsp                 | I <sup>2</sup> C spike time                              |                                             |        | 50           |                                      | 50        | ns   |

| tsds                | I <sup>2</sup> C serial-data setup time                  |                                             | 250    |              | 100                                  |           | ns   |

| tsdh                | I <sup>2</sup> C serial-data hold time                   |                                             | 0      |              | 0                                    |           | ns   |

| ticr <sup>(2)</sup> | I <sup>2</sup> C input rise time                         |                                             |        | 1000         | 20                                   | 300       | ns   |

| ticf <sup>(3)</sup> | I <sup>2</sup> C input fall time                         |                                             |        | 300          | 20 ×<br>(Vcc/<br>3.6 V)              | 300       | ns   |

| tocf <sup>(3)</sup> | I <sup>2</sup> C output fall time                        | 10-pF to 400-pF bus                         |        | 300          | 20 ×<br>(V <sub>cc</sub> /<br>3.6 V) | 300       | ns   |

| tbuf                | I <sup>2</sup> C bus free time between stop and start    |                                             | 4.7    |              | 1.3                                  |           | μs   |

| tsts                | I <sup>2</sup> C start or repeated start condition setup |                                             | 4.7    |              | 0.6                                  |           | μs   |

| tsth                | I <sup>2</sup> C start or repeated start condition hold  |                                             | 4      |              | 0.6                                  |           | μs   |

| tsps                | I <sup>2</sup> C stop condition setup                    |                                             | 4      |              | 0.6                                  |           | μs   |

| tvd(data)           | Valid data time                                          | SCL low to SDA output valid                 |        | 3.5          |                                      | 0.9       | μs   |

| tvd(ack)            | Valid data time of ACK condition                         | ACK signal from SCL low to<br>SDA (out) low |        | 3.5          |                                      | 0.9       | μs   |

| Cb                  | I <sup>2</sup> C bus capacitive load                     |                                             |        | 400          |                                      | 400       | pF   |

(1) All timing requirements should refer to I<sup>2</sup>C standard, and all parameters in table are NOT tested in production.

(2) ticr is decided by input signal rising time.

(3) Data is provided by bench validation, test condition: 150ohm series resistor connect to SDA pin, then 2.2 Kohm pull up to VCC, 150 pF Cload pull down to GND, t<sub>icr</sub> = 29 ns, t<sub>ocf</sub> = 25 ns, V<sub>OL</sub> = 166 mv.

### **Switching Characteristics**

Over recommended operating free-air temperature range,  $C_L \leq 100 \text{ pF}$ , unless otherwise noted.

|     | Description                                                 | From    | То       | Standa | ard Mod | Fast Mode |     | 11   |

|-----|-------------------------------------------------------------|---------|----------|--------|---------|-----------|-----|------|

|     | Description                                                 | (Input) | (Output) | Min    | Max     | Min       | Max | Unit |

| tiv | Interrupt valid time                                        | P port  | ĪNT      |        | 4       |           | 4   | μs   |

| tir | Interrupt reset delay time                                  | SCL     | ĪNT      |        | 4       |           | 4   | μs   |

| 4   | Output data valid; For V <sub>CC</sub> = 2.3 V $\sim$ 3.6 V |         | Durant   |        | 400     |           | 400 | ns   |

|     | Output data valid; For V_{CC} = 1.65 V $\sim 2.3 \ V$       | SCL     | P port   |        | 400     |           | 400 | ns   |

| tps | Input data setup time                                       | P port  | SCL      | 150    |         | 150       |     | ns   |

| tph | Input data hold time                                        | P port  | SCL      | 1      |         | 1         |     | μs   |

| Parameter                 | ,                    | Condition                | min | typ | max | Unit |

|---------------------------|----------------------|--------------------------|-----|-----|-----|------|

| RESET Timing Requirements |                      |                          |     |     |     |      |

| tW                        | Reset pules duration |                          | 60  |     |     | ns   |

| tREC                      | Reset recovery time  |                          | 0   |     | 15  | ns   |

| 4DEOET                    | Time to reset        | For VCC = 2.3 V~3.6 V    | 400 |     |     |      |

| tRESET                    | Time to reset        | For VCC = 1.65 V – 2.3 V | 550 |     |     | ns   |

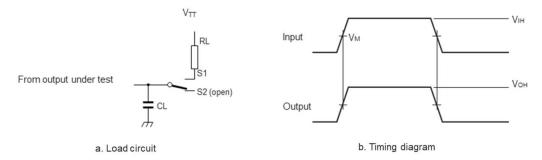

### **Parameter Measurement Waveforms**

### **Typical Performance Characteristics**

## **Detailed Description**

### Overview

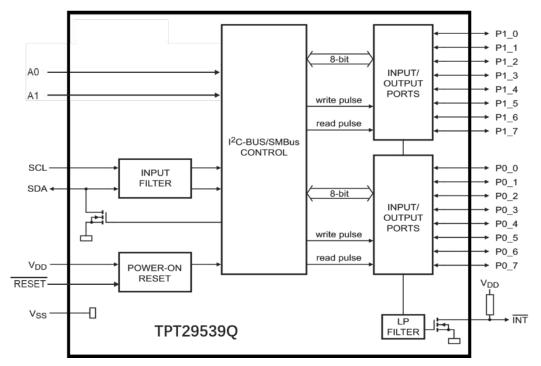

The TPT29539Q is a 16-bit GPIO expander with interrupt and weak pull-up resistors for I<sup>2</sup>C-bus applications. The power supplier voltage ranges from 1.65 V to 3.6 V, allowing for the TPT29539Q to interconnect with 1.8-V microcontrollers.

The TPT29539Q contains 16-bit Input and Output. The open-drain interrupt ( $\overline{INT}$ ) output is changeable when any input state changes from its related register state. The device is used to indicate the system master that an input state has changed. ( $\overline{INT}$ ) can be connected to the interrupt input of a microcontroller. The TPT29539Q can remain a simple slave device. The power-on reset sets the registers to their default values and initializes the device state machine. The TPT29539Q also has a hardware  $\overline{INT}$  pin to reset the device to its default state.

All input/output pins do not have internal pull-up resistors, thus the device can save power consumption as communicating with external I/Os. Two hardware pins (A0, A1) select the fixed  $I^2$ C-bus address and allow up to eight devices to share the same  $I^2$ C-bus.

The TPT29539Q is available in the TSSOP24 package, and is characterized from -40°C to +125°C to meet automotive application requirements.

#### Figure 5. Functional Block Diagram

### **Feature Description**

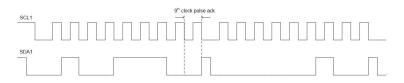

#### Figure 6. I<sup>2</sup>C BUS (1.65 V ~ 3.6 V) Waveform

#### **Device Address**

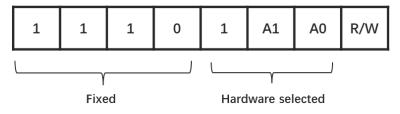

Following a START condition, the bus master must output the address of the slave it is accessing. All input/output pins have internal weak pull-up resistors to remove external components. Two hardware pins (A0, A1) select the fixed  $l^2$ C-bus address and allow up to eight devices to share the same  $l^2$ C-bus. To conserve power, address pins (A0, A1) must be pulled HIGH or LOW. The address of the TPT29539Q is shown below.

Figure 7. Slave Device Address

#### **Control Register**

#### **Command Byte**

The command byte is the first byte to follow the address byte during a write transmission. It is used as a pointer to determine which of the following registers will be written or read.

| Table 2. Command | Byte Description |

|------------------|------------------|

|------------------|------------------|

| Command | Register                  |

|---------|---------------------------|

| 0       | Input port 0              |

| 1       | Input port 1              |

| 2       | Output port 0             |

| 3       | Output port 1             |

| 4       | Polarity Inversion port 0 |

| 5       | Polarity Inversion port 1 |

| 6       | Configuration port 0      |

| 7       | Configuration port 1      |

#### Register 0 and 1: Input port registers

This register is an input-only port, which means the incoming logic levels of the pins, regardless of whether the pin is defined as an input or an output by Register 3 ( output port 1 ) ,and writes to this register have no effect.

The default value 'X' is determined by the externally logic level.

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | 10.7 | 10.6 | 10.5 | 10.4 | 10.3 | 10.2 | 10.1 | 10.0 |

| Default | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

#### Table 4. Input Port 1 Register

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | l1.7 | I1.6 | l1.5 | l1.4 | l1.3 | l1.2 | l1.1 | l1.0 |

| Default | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

#### Register 2 and 3: Output port registers

This register is an output-only port, which means the outcoming logic levels of the pins are defined as outputs by Register 6 (Configuration port 0) and 7 (Configuration port 1). Bit values in this register have no effect on pins defined as inputs. In fact, the value reading from this register is in the flip-flop controlling the output selection, not the actual pin value.

#### Table 5. Output Port 0 Register

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | O0.7 | O0.6 | O0.5 | O0.4 | O0.3 | O0.2 | O0.1 | O0.0 |

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

#### Table 6. Output Port 1 Register

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | 01.7 | O1.6 | O1.5 | 01.4 | 01.3 | 01.2 | O1.1 | O1.0 |

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

#### **Register 4 and 5: Polarity Inversion registers**

This register allows the user to invert the polarity of the input port register data. If a bit in this register is set (written with '1'), the input port data polarity is inverted. If a bit in this register is cleared (written with '0'), the input port data polarity is retained.

#### Table 7. Polarity Inversion Port 0 Register

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | N0.7 | N0.6 | N0.5 | N0.4 | N0.3 | N0.2 | N0.1 | N0.0 |

| Default | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

#### Table 8. Polarity Inversion Port 1 Register

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | N1.7 | N1.6 | N1.5 | N1.4 | N1.3 | N1.2 | N1.1 | N1.0 |

| Default | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

#### **Register 6 and 7: Configuration registers**

This register configures the directions of the I/O pins. If a bit in this register is set (written with '1'), the corresponding port pin is enabled as an input with a high-impedance output driver. If a bit in this register is cleared (written with '0'), the corresponding port pin is enabled as an output. Note that there is a high-value resistor tied to  $V_{DD}$  at each pin. At reset, the device's ports are inputs with a pull-up to  $V_{DD}$ .

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | C0.7 | C0.6 | C0.5 | C0.4 | C0.3 | C0.2 | C0.1 | C0.0 |

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

#### Table 9. Configuration port 0 Register

#### Table 10. Configuration port 1 Register

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | C1.7 | C1.6 | C1.5 | C1.4 | C1.3 | C1.2 | C1.1 | C1.0 |

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

## **Application and Implementation**

Note

Information in the following application sections is not part of the 3PEAK's component specification and 3PEAK does not warrant its accuracy or completeness. 3PEAK's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

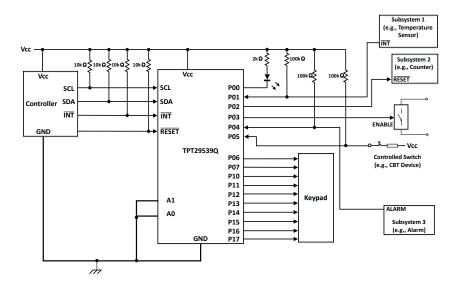

### **Application Information**

The TPT29539Q builds in 16-bit input and output, and interrupt  $\overline{\text{INT}}$  can be connected to the interrupt input of a microcontroller, then the interrupt  $\overline{\text{INT}}$  output will response to any input state change.

#### **IO Configuration Requirements**

To make sure the TPT29539Q can support the different application, the device is requested to set all GPIOs a default value after or before powering up the device. Or the backup method, after powering up the TPT29539Q, registers are reset to a default value by digital circuit while GPIOs status are not yet stable, because there is no pull-up/pull-down resistors inside. The digital circuit is monitoring and comparing the GPIOs status to the default value of the registers in real time and when they are not matched, during the unstable period, the INT is locked. This has been confirmed in lab testing by adding time delay in seconds after powering up the TPT29539Q (for GPIOs status to reach a stable status). After seconds, the INT function is ready to work, and the performance is exactly as designed. The delay time will depend on the different capacitance on board.

### **Typical Application**

One application of the TPT29539Q device is used as below.

### Layout

### Layout Guideline

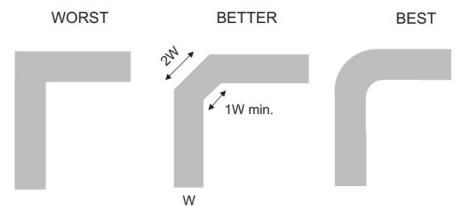

Reflections and matching are closely related to loop antenna theory, but different enough to warrant their own discussion. When a PCB trace turns a corner at a 90° angle, a reflection can occur. This is primarily due to the change in the width of the trace. At the apex of the turn, the trace width is increased to 1.414 times its width. This change in width upsets the transmission line characteristics, especially the distributed capacitance and self-inductance of the trace, thus resulting in the reflection. Not all PCB traces can be straight, so they will have to turn corners. Figure 9 shows progressively better techniques of rounding corners. Only the last example (BEST) maintains constant trace width and minimizes reflections.

Figure 9. Trace Example

Route high-speed signals using a minimum of vias and corners which reduces signal reflections and impedance changes. When a via must be used, increase the clearance size around it to minimize its capacitance. Each via introduces discontinuities in the signal's transmission line and increases the chance of picking up interference from the other layers of the board. Be careful when designing test points, through-hole pins are not recommended at high frequencies.

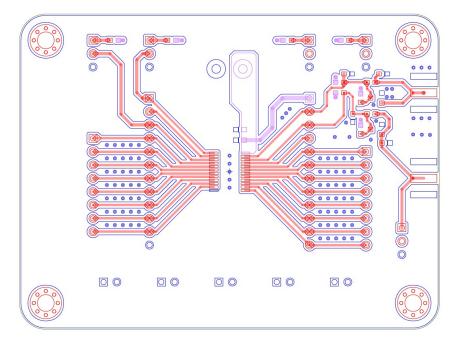

### Layout Example

Figure 10 illustrates an example of a PCB layout with the TPT29539Q. Some key considerations are as follows: