### **Features**

- Integrated 5 V or 3.3 V up to 250 mA, ±2% Accuracy,

Main Low-dropout Voltage Regulator

- Integrated 5 V up to 150 mA, ±2% Accuracy, Auxiliary Regulator with Off-board Usage Protection

- Voltage Regulator with External PNP Transistor

Configurable for Off-board Usage or for Load Sharing

- Very Low Quiescent Current Consumption in Low Power Mode

- Integrated CAN Transceiver Meets the ISO 11898-2:2024 and SAE J2284-1 to SAE J2284-5 Physical Layer Standards (Meet ISO 11898-2:2024 and CiA601-4 for Signal Improvement Capability (SIC) Option Available)

- Support Classical CAN and Optimized CAN FD SIC up to 8 Mbps Data Rates

- Support Partial Networking by Means of Selective Wake Up/Wake-Up Frame

- Local Wake-up via the WAKE Pin and Wake-up Source Recognition

- Integrated Configurable Timeout and Window Watchdog, Reset Outputs for Fail-safe and Supervision Functions

- 16-, 24- and 32- Bit SPI for Diagnostics and Configuration

- Configuration of Selected Functions via Non-volatile Memory

- Protection Feature:

- Bus Pin IEC 61000-4-2 ESD Protection up to ±8 kV

- Bus Fault Protection: ±45 V

- Undervoltage and Overvoltage Protection

- Short Circuit Protection

- Overtemperature Warning and Shutdown Protection

- Available in DFN3.5X5.5-20 Package with Improved Automated Optical Inspection (AOI) Capability

- AEC-Q100 Qualified for Automotive Applications , Grade 1

### **Applications**

- Heating, Ventilation and Air Conditioning (HVAC)

- Body Control Modules (BCM), Tailgate, Seat, Roof, Door, Trailer Modules

- Passive Keyless Entry and Start Modules, Remote Keyless Entry Modules

- · Lighting Control Modules

- Gear Shifters and Steering Column Control Module

### **Description**

The TPT1169xQ is a system basis chip (SBC) designed for automotive applications. The device functions as a main power supply for the microcontroller and as a transceiver for the CAN bus networks.

The SBC integrates 250-mA main low drop-out voltage regulator for the microcontroller as a power supply with 5-V and 3.3-V output options. Additionally, it includes another 5-V 150-mA low drop-out voltage regulator for other on-board device power supply. The X version features a voltage regulator with off-board protection, designed for off-board devices power supply. Furthermore, the SBC integrates CAN transceiver that supports partial networking and enables data rates of up to 8 Mbps. This transceiver meets the ISO 11898-2:2024 and SAE J2284-1 to SAE J2284-5 Physical Layer Standards. Variants with signal improvement capability (SIC) also meets CiA601-4 standards. Moreover, the system integrates a configurable timeout/window watchdog with a reset feature, limp home outputs, and an undervoltage reset feature. It also includes an integrated Serial Peripheral Interface (SPI) for configuration and monitoring purposes.

The SBC offers low-power modes for low-power consumption applications. The device can be woken up from low-power mode locally via wake-pin or cyclic wake-up, and remote wake-up via bus is also possible.

The TPT1169xQ is available in the exposed pad DFN3.5X5.5-20L package, featuring enhanced automated optical inspection (AOI) capabilities. Additionally, it is AEC-Q100 qualified for automotive applications.

www.3peak.com 1 / 70 CA20250706A0

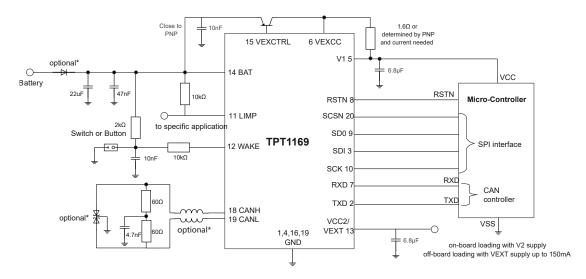

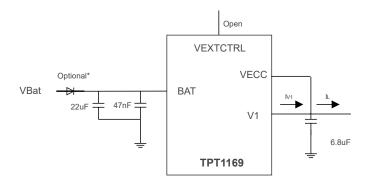

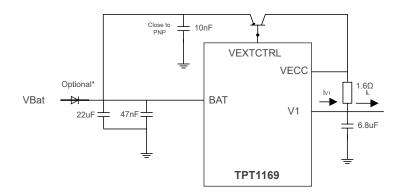

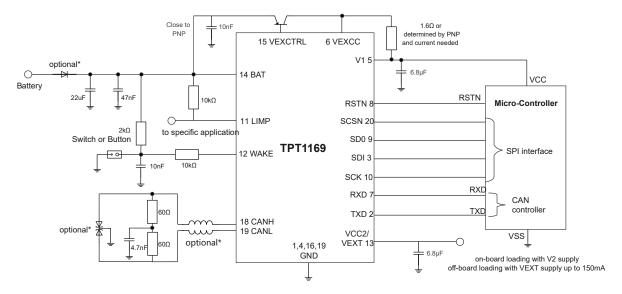

# **Typical Application Circuit**

www.3peak.com 2 / 70 CA20250706A0

### **Table of Contents**

| Features                            | 1  |

|-------------------------------------|----|

| Applications                        | 1  |

| Description                         | 1  |

| Typical Application Circuit         | 2  |

| Product Family Table                | 5  |

| Revision History                    | 5  |

| Pin Configuration and Functions     | 6  |

| Specifications                      | 8  |

| Absolute Maximum Ratings (1)        | 8  |

| ESD and Transient Ratings           | 8  |

| Recommended Operating Conditions    | 9  |

| Thermal Information                 | 9  |

| Electrical Characteristics          | 10 |

| AC Timing Requirements              | 16 |

| Typical Performance Characteristics | 20 |

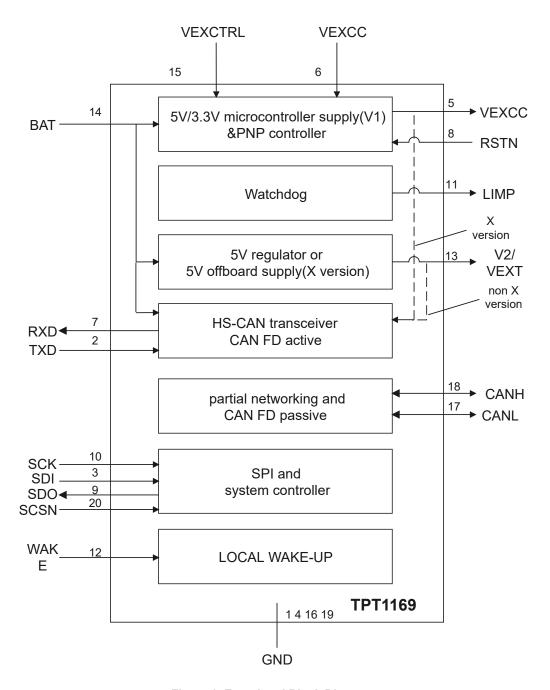

| Detailed Description                | 21 |

| Overview                            | 21 |

| Functional Block Diagram            | 22 |

| Feature Description                 | 22 |

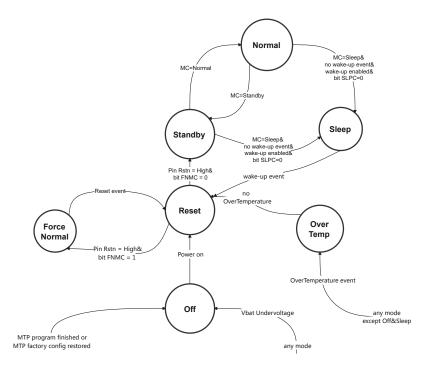

| System Controller                   | 22 |

| Watchdog                            | 27 |

| System Reset                        | 31 |

| Reset Resources                     | 32 |

| Global Temperature Protection       | 32 |

| Power Supplies                      | 33 |

| LIMP Output                         | 36 |

| High-Speed CAN Transceiver          | 38 |

| CAN Partial Networking              | 42 |

| CAN Fail-Safe Features              | 47 |

| Wake-up and Interrupt Event         | 48 |

| Non-Volatile SBC Configuration      | 54 |

| Device Identification               | 56 |

| Register Locking                    | 57 |

| General-Purpose Memory              | 58 |

| SPI                                 | 58 |

| Application and Implementation      | 65 |

| Typica     | al Application           | 65 |

|------------|--------------------------|----|

| Tape and F | Reel Information         | 66 |

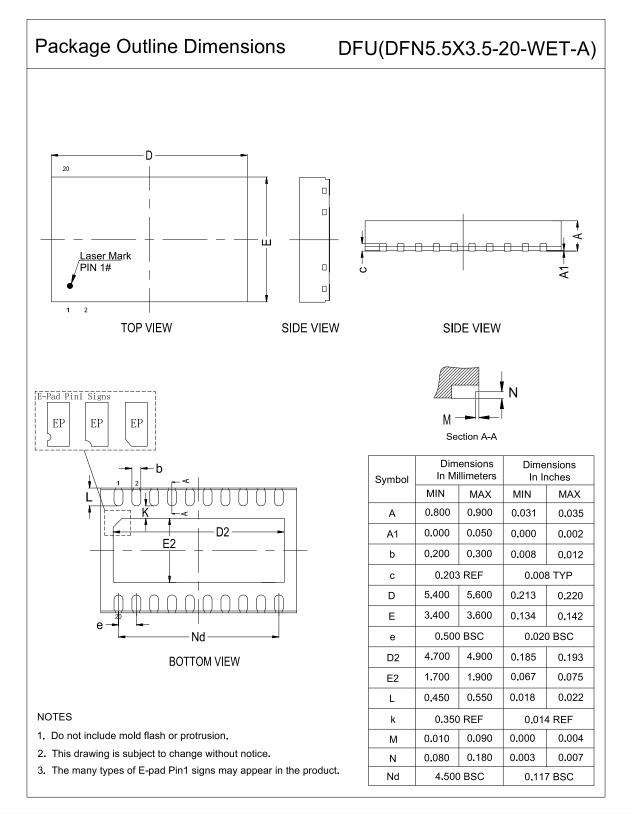

| Package C  | Outline Dimensions       | 67 |

| DFN5.      | .5X3.5-20-WET-A          | 67 |

| Order Info | ormation                 | 68 |

| IMPORTAN   | NT NOTICE AND DISCLAIMER | 69 |

# **Product Family Table**

| Order Number       | V1 Output              | V2/VEXT Output                    | CAN<br>Transceiver  | CAN FD Passive<br>and Partial<br>Networking | Device ID |

|--------------------|------------------------|-----------------------------------|---------------------|---------------------------------------------|-----------|

| TPT11695Q-DFUR-S   | 5 V for MCU only       | V2 5 V for on-board loads         | 8Mbps CAN FD<br>SIC | Disable                                     | CFh       |

| TPT11695XQ-DFUR-S  | 5 V for MCU and<br>CAN | VEXT 5 V for off-<br>board loads  | 8Mbps CAN FD<br>SIC | Disable                                     | CEh       |

| TPT11695FQ-DFUR-S  | 5 V for MCU only       | V2 5 V for on-board loads         | 8Mbps CAN FD<br>SIC | Supported                                   | EFh       |

| TPT11695XFQ-DFUR-S | 5 V for MCU and CAN    | VEXT 5 V for off-<br>board loads  | 8Mbps CAN FD<br>SIC | Supported                                   | EEh       |

| TPT11693Q-DFUR-S   | 3.3 V for MCU only     | V2 5 V for CAN and on-board loads | 8Mbps CAN FD<br>SIC | Disable                                     | C9h       |

| TPT11693FQ-DFUR-S  | 3.3 V for MCU only     | V2 5 V for CAN and on-board loads | 8Mbps CAN FD<br>SIC | Supported                                   | E9h       |

## **Revision History**

| Date       | Revision  | Notes            |

|------------|-----------|------------------|

| 2025-05-15 | Rev.Pre.0 | Initial version  |

| 2025-07-15 | Rev.A.0   | Released version |

www.3peak.com 5 / 70 CA20250706A0

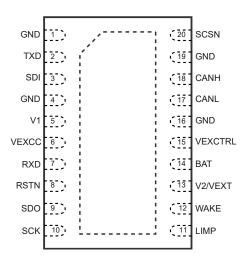

## **Pin Configuration and Functions**

TPT1169xQ DFN3.5x5.5-20L Package Top View

Table 1. Pin Functions: TPT1169xQ

| Р   | in      |                                                                                                    |

|-----|---------|----------------------------------------------------------------------------------------------------|

| No. | Name    | Description                                                                                        |

| 1   | GND     | Ground                                                                                             |

| 2   | TXD     | CAN transceiver transmit input                                                                     |

| 3   | SDI     | SPI Data input                                                                                     |

| 4   | GND     | Ground                                                                                             |

| 5   | V1      | LDO1 output                                                                                        |

| 6   | VEXCC   | External PNP transistor current measurement; connected to the collector of external PNP transistor |

| 7   | RXD     | CAN transceiver receive output                                                                     |

| 8   | RSTN    | Reset input/output; active low                                                                     |

| 9   | SDO     | SPI Data output                                                                                    |

| 10  | SCK     | SPI clock input                                                                                    |

| 11  | LIMP    | Limp home output; open-drain; active low                                                           |

| 12  | WAKE    | Local wake-up input                                                                                |

| 13  | V2/VEXT | LDO2 output (without X suffix) / LDO for off-board device (with X suffix)                          |

| 14  | BAT     | Battery supply voltage                                                                             |

| 15  | VEXCTRL | External PNP transistor control pin; connected to the base of the external PNP transistor          |

| 16  | GND     | Ground                                                                                             |

| 17  | CANL    | CAN transceiver Low-level BUS line                                                                 |

www.3peak.com 6 / 70 CA20250706A0

| Pin |      | Description                         |  |

|-----|------|-------------------------------------|--|

| No. | Name | Description                         |  |

| 18  | CANH | CAN transceiver High-level BUS line |  |

| 19  | GND  | Ground                              |  |

| 20  | SCSN | SPI chip select, active low         |  |

<sup>(1)</sup> DFN package die is connected to both the GND pin and the exposed pad. The GND pin must be soldered to board ground and for enhanced thermal and electrical performance, the exposed pad is also recommended be soldered to board ground.

www.3peak.com 7 / 70 CA20250706A0

### **Specifications**

### Absolute Maximum Ratings (1)

|                       | Parameter                                 | Conditions                            | Min  | Тур | Max                   | Unit |

|-----------------------|-------------------------------------------|---------------------------------------|------|-----|-----------------------|------|

| V <sub>BAT</sub>      | Supply Voltage Range                      | Pin VBAT                              | -0.3 |     | 45.0                  | V    |

| $V_{HV}$              | High Voltage Pin Voltage Range            | Pin LIMP, VEXCTRL                     | -0.3 |     | 45.0                  | V    |

| V <sub>OUT</sub>      | Power Output Voltage Range                | Pin VOUT1, VOUT2                      | -0.3 |     | 6.0                   | V    |

| V <sub>LOGIC</sub>    | Logic Terminal Voltage Range              | Pin TXD, RXD, SDI, SCK,<br>SCSN, RSTN | -0.3 |     | V <sub>VOUT1</sub> +0 | V    |

| V <sub>EXCC</sub>     | Pin VEXCC Voltage Range                   | Pin VEXCC                             | -0.3 |     | 6.0                   | V    |

| V <sub>EXT</sub>      | Pin VEXT Voltage Range                    | Pin VEXT                              | -0.3 |     | 45.0                  | V    |

| V <sub>WAKE</sub>     | Pin WAKE Voltage Range                    | Pin WAKE                              | -18  |     | 45.0                  | V    |

| V <sub>BUS</sub>      | CAN Bus Voltage Range                     | Pin CANH, CANL                        | -45  |     | 45.0                  | V    |

| V <sub>BUS_DIFF</sub> | Differential Output Voltage of Can<br>Bus | CANH - CANL                           | -45  |     | 45.0                  | V    |

| I <sub>LIMP_IN</sub>  | LIMP Pin Input Current                    |                                       |      |     | 20.0                  | mA   |

| TJ                    | Junction Temperature                      |                                       | -55  |     | 150.0                 | °C   |

| T <sub>STG</sub>      | Storage Temperature                       |                                       | -55  |     | 150.0                 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

### **ESD and Transient Ratings**

|                   | Parameter                                 | Condition                                                                              | Min  | Max | Unit |

|-------------------|-------------------------------------------|----------------------------------------------------------------------------------------|------|-----|------|

| V <sub>ESD</sub>  | Electrostatics Discharge                  | Contact discharge on bus pins (CANH,CANL),IEC61000-4-2(150 pF, 330Ω discharge circuit) | -8   | 8   | kV   |

|                   |                                           | Human Body Model (HBM) on bus<br>pins (CANH,CANL),AEC Q100-002                         | -15  | 15  | kV   |

|                   |                                           | Human Body Model (HBM) on any pins,AEC Q100-002 (1)                                    | -8   | 8   | kV   |

|                   |                                           | Charged Device Model (CDM) on all pins,AEC Q100-011                                    | -1.5 | 1.5 | kV   |

|                   |                                           | Pulse1                                                                                 | -100 |     | V    |

| V <sub>TRAN</sub> | Transient Immunity ISO 7637-2 on Bus Pins | Pulse2a                                                                                |      | 75  | V    |

|                   |                                           | Pulse3a                                                                                | -150 |     | V    |

|                   |                                           | Pulse3b                                                                                |      | 100 | V    |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDAJEDEC JS-001 specification.

www.3peak.com 8 / 70 CA20250706A0

## **Recommended Operating Conditions**

|                  | Parameter                    | Min | Max | Unit |

|------------------|------------------------------|-----|-----|------|

| Vs               | Battery Power Supply Voltage | 6.5 | 40  | V    |

| f <sub>SPI</sub> | SPI Frequency                |     | 4   | MHz  |

| T <sub>A</sub>   | Operating Temperature        | -40 | 125 | °C   |

### **Thermal Information**

| Package Type   | θ <sub>JA</sub> | θ <sub>JC</sub> | Unit |

|----------------|-----------------|-----------------|------|

| DFN3.5x5.5-20L | 29              | 24.74           | °C/W |

www.3peak.com 9 / 70 CA20250706A0

### **Electrical Characteristics**

All test conditions:  $V_{BAT}$  = 12 V,  $R_L$  = 60  $\Omega$ ,  $T_A$  = -40°C to 125°C, unless otherwise noted.

| Symbol                    | Parameter                                                                                           | Condition                                                                                                                                                                                                  | Min | Тур | Max      | Unit   |

|---------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|----------|--------|

| Pin V <sub>BAT</sub> ;    | Battery Supply                                                                                      |                                                                                                                                                                                                            |     |     | <u>'</u> |        |

| V <sub>BAT</sub>          | Supply Voltage                                                                                      |                                                                                                                                                                                                            | 2.8 |     | 40       | ٧      |

| V <sub>TH_DET_P</sub>     | Power-on Detection Threshold on V <sub>BAT</sub>                                                    | V <sub>BAT</sub> rising                                                                                                                                                                                    | 4.2 |     | 4.55     | V      |

| V <sub>TH_DET_P</sub>     | Power-off Detection Threshold on V <sub>BAT</sub>                                                   | V <sub>BAT</sub> falling                                                                                                                                                                                   | 2.8 |     | 3        | \<br>\ |

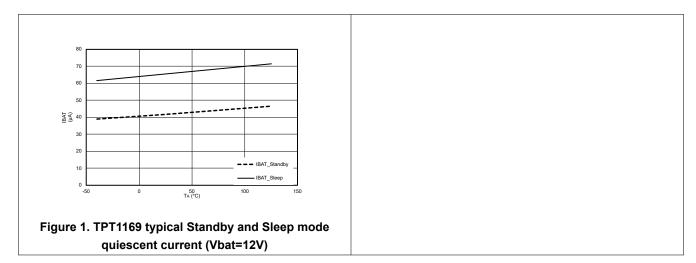

| Sleep-Mode Supply Current | MC = 001; CAN offline mode;<br>$V_{OUT2}/V_{EXT}$ off; $7 \text{ V} \leq V_{BAT} \leq 40 \text{ V}$ |                                                                                                                                                                                                            | 41  | 65  | μA       |        |

|                           | Standby-Mode Supply Current                                                                         | MC = 100; CAN offline mode;<br>$V_{OUT2}/V_{EXT}$ off; $I_{OUT1} = 0 \mu A$ ;<br>$7 \text{ V} \leq V_{BAT} \leq 40 \text{ V}$                                                                              |     | 63  | 91       | μΑ     |

|                           | Additional Supply Current                                                                           | Additional current with $V_{OUT2}$ on ( $V_{2C}$ = 01/10/11); $V_{OUT2}/V_{EXT}$ off; $I_{OUT1}$ = 0 $\mu$ A; $T_{OUT1} \leq 40 V_{OUT2}$                                                                  |     | 8   | 32       | μΑ     |

|                           |                                                                                                     | Additional current with V <sub>EXT</sub> on (V <sub>EXTC</sub> = 01/10/11); V <sub>OUT2</sub> /V <sub>EXT</sub> off; I <sub>OUT1</sub> = 0 $\mu$ A; 7 V $\leq$ V <sub>BAT</sub> $\leq$ 40 V <sup>(1)</sup> |     | 8   | 32       | μA     |

| I <sub>BAT</sub>          |                                                                                                     | Additional current in CAN offline bias mode                                                                                                                                                                |     | 52  | 65       | μА     |

|                           |                                                                                                     | Additional current when partial networking enabled; bus active; CPNC = 1; PNCOK = 1 (1)                                                                                                                    |     | 900 | 1,200    | μA     |

|                           |                                                                                                     | Additional current from WAKE input;<br>WPRE = 1; WPFE = 1                                                                                                                                                  |     | 2   | 3        | μА     |

|                           |                                                                                                     | MC = 111; CAN active mode; recessive; V <sub>TXD</sub> = V <sub>OUT1</sub>                                                                                                                                 |     | 4   | 7.5      | mA     |

|                           | Normal-Mode Supply Current                                                                          | MC = 111; CAN active mode; dominant; V <sub>TXD</sub> = 0 V                                                                                                                                                |     | 46  | 67       | mA     |

| Pin V1; Vo                | oltage Output 1                                                                                     |                                                                                                                                                                                                            |     |     |          |        |

| R <sub>ON_BAT-</sub>      | On Resistance between $V_{BAT}$ Pin and $V_{OUT1}$ Pin                                              | 2.8 V ≤ V <sub>BAT</sub> ≤ 3.25 V; I <sub>OUT1</sub> = 250 mA                                                                                                                                              |     |     | 3.2      | Ω      |

|                           |                                                                                                     | $V_{OUT1\_NORM} = 5 \text{ V}; 5.5 \text{ V} \le V_{BAT} \le 40 \text{ V};$<br>$I_{OUT1} \le 200 \text{ mA}^{(1)}$                                                                                         | 4.9 | 5   | 5.1      | V      |

| Vo                        | Output Voltage                                                                                      | $V_{OUT1\_NORM} = 5 \text{ V}; 5.65 \text{ V} \le V_{BAT} \le 40 \text{ V};$<br>$I_{OUT1} \le 250 \text{ mA}$                                                                                              | 4.9 | 5   | 5.1      | V      |

|                           |                                                                                                     | V <sub>OUT1_NORM</sub> = 5 V;<br>V <sub>BAT</sub> ≤ V <sub>UVBAT</sub> and rising; t ≤ t <sub>STARTUP</sub>                                                                                                |     |     | 5.5      | V      |

www.3peak.com 10 / 70 CA20250706A0

| Symbol                        | Parameter                                                                     | Condition                                                                                                                                                                | Min   | Тур | Max   | Unit |

|-------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|------|

|                               |                                                                               | V <sub>OUT1_NORM</sub> = 3.3 V;<br>3.834 V ≤ V <sub>BAT</sub> ≤ 40 V; I <sub>OUT1</sub> ≤ 200 mA                                                                         | 3.234 | 3.3 | 3.366 | ٧    |

|                               |                                                                               | $V_{OUT1\_NORM} = 3.3 \text{ V};$<br>3.984 V \leq V_{BAT} \leq 40 V; $I_{OUT1} \le 250 \text{ mA}$                                                                       | 3.234 | 3.3 | 3.366 | V    |

| Δ                             | RAM Retention Voltage                                                         | 2.4 V ≤ V <sub>BAT</sub> ≤ 3 V; I <sub>OUT1</sub> = 2 mA                                                                                                                 |       |     | 100   | mV   |

| V <sub>RET_RAM</sub>          | Difference between V <sub>BAT</sub> and V <sub>OUT1</sub> ; 5-V Variants Only | $2.4V \le V_{BAT} \le 3 \text{ V; } I_{OUT1} = 200  \mu\text{A}^{(1)}$                                                                                                   |       |     | 10    | mV   |

| R <sub>ON_BAT-</sub><br>VOUT1 | On Resistance between $V_{BAT}$<br>Pin and $V_{OUT1}$ Pin                     | $3.25 \text{ V} \le \text{V}_{BAT} \le 5.65 \text{ V};$ $I_{OUT1} = 250 \text{ mA}$                                                                                      |       |     | 3     | Ω    |

|                               |                                                                               | V <sub>UV_OUT1_NORM</sub> = 90%                                                                                                                                          | 4.5   |     | 4.75  | V    |

|                               | V <sub>OUT1</sub> Under-Voltage Detection                                     | Vuv_out1_norm = 80%                                                                                                                                                      | 4     |     | 4.25  | V    |

|                               | Voltage; 5-V Variants                                                         | V <sub>UV_OUT1_NORM</sub> = 70%                                                                                                                                          | 3.5   |     | 3.75  | V    |

| V <sub>UVD_OUT1</sub>         |                                                                               | V <sub>UV_OUT1_NORM</sub> = 60%                                                                                                                                          | 3     |     | 3.25  | V    |

|                               | V <sub>OUT1</sub> Under-Voltage Detection<br>Voltage; 3.3-V Variants          | Vuv_out1_norm = 90%                                                                                                                                                      | 2.97  |     | 3.135 | ٧    |

| V                             | V <sub>OUT1</sub> Under-Voltage Recovery<br>Voltage; 5-V Variants             | V <sub>UV_OUT1_NORM</sub> = 90%                                                                                                                                          | 4.5   |     | 4.75  | ٧    |

| Vuvr_out1                     | V <sub>OUT1</sub> Under-Voltage Recovery<br>Voltage; 3.3-V Variants           | V <sub>UV_OUT1_NORM</sub> = 90%                                                                                                                                          | 2.97  |     | 3.135 | V    |

| I <sub>SINK</sub>             | Sink Current                                                                  | 5.65 V ≤ V <sub>BAT</sub> ≤ 18 V                                                                                                                                         | 214   |     |       | mA   |

| lo_sc                         | Short-Circuit Output Current                                                  |                                                                                                                                                                          | -500  |     | -250  | mA   |

| I <sub>DD_CAN_IN</sub>        | Internal CAN Supply Current from V1 <sup>(1)</sup>                            | Normal mode; MC = 111; CAN active mode; CAN dominant; $V_{TXD} = 0 \text{ V}$ ; short-circuit on bus lines; $-3 \text{ V} \le V_{CANH} = V_{CANL} \le +18 \text{ V}$     |       |     | 85    |      |

| Pin V <sub>EXCTE</sub>        | RL; PNP Base                                                                  |                                                                                                                                                                          |       |     |       |      |

| I <sub>O_SC</sub>             | Short-Circuit Output Current                                                  | V <sub>EXCTRL</sub> ≥ 4.5 V; 7 V ≤ V <sub>BAT</sub> ≤ 40 V                                                                                                               | 3.4   | 5.8 | 7.5   | mA   |

|                               | PNP Activation Threshold                                                      | PDC = 0                                                                                                                                                                  | 40    | 83  | 130   | mA   |

| I <sub>TH_ACT_PN</sub>        | Current; Load Current<br>Increasing                                           | PDC = 1                                                                                                                                                                  | 18    | 50  | 70    | mA   |

| I <sub>TH_DEACT_</sub>        | PNP Deactivation Threshold                                                    | PDC = 0                                                                                                                                                                  | 16    | 44  | 60    | mA   |

| PNP                           | Current; Load Current Falling                                                 | PDC = 1                                                                                                                                                                  | 1     | 11  | 22    | mA   |

| V <sub>TH_ICTRL</sub>         | PNP Current Control Threshold Voltage                                         | Rising edge on V <sub>BAT</sub> pin                                                                                                                                      | 5.9   |     | 7.5   | ٧    |

| Pin V <sub>EXCC</sub> ;       | PNP Collector                                                                 |                                                                                                                                                                          |       |     |       |      |

| V <sub>TH_ACT_IL</sub>        | Current Limiting Activation Threshold Voltage                                 | Measured across resistor connected between $V_{EXB}$ pin and $V_{OUT1}$ pin; $2 \text{ V} \le V_{OUT1} \le 5.5 \text{ V}$ ; $7.5 \text{ V} \le V_{BAT} \le 40 \text{ V}$ | 240   |     | 360   | mV   |

| Pin V2; Vo                    | oltage Output 2                                                               |                                                                                                                                                                          | I .   |     | 1     |      |

|                               |                                                                               |                                                                                                                                                                          |       |     |       |      |

www.3peak.com 11 / 70 CA20250706A0

| Symbol                     | Parameter                                                | Condition                                                                                                                                                                     | Min                         | Тур | Max                      | Unit |

|----------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----|--------------------------|------|

| R <sub>ON_BAT-</sub>       | On Resistance between V <sub>BAT</sub>                   | 4.5 V ≤ V <sub>BAT</sub> ≤ 6.2 V;                                                                                                                                             |                             |     | 0.7                      |      |

| VOUT2                      | Pin and V <sub>OUT2</sub> Pin                            | 5 mA ≤ I <sub>OUT2</sub> ≤ 150 mA                                                                                                                                             |                             |     | 8.7                      | Ω    |

| V <sub>UVD_OUT2</sub>      | V <sub>OUT2</sub> Under-Voltage Detection Voltage        |                                                                                                                                                                               | 4.45                        |     |                          | V    |

| Vuvr_out2                  | V <sub>OUT2</sub> Under-Voltage Recovery Voltage         |                                                                                                                                                                               |                             |     | 4.8                      | V    |

| V <sub>OVD</sub> OUT2      | V <sub>OUT2</sub> Over-Voltage Detection<br>Voltage      |                                                                                                                                                                               | 5.2                         |     | 5.5                      | V    |

| V <sub>OVR_OUT2</sub>      | V <sub>OUT2</sub> Over-Voltage Recovery Voltage          |                                                                                                                                                                               | 5.2                         |     | 5.5                      | V    |

| lo_sc                      | Short-Circuit Output Current                             |                                                                                                                                                                               | -300                        |     | -180                     | mA   |

| I <sub>DD_CAN_IN</sub> TV2 | Internal CAN Supply Current from V2 (1)                  | Normal mode; MC = 111;<br>CAN active mode; CAN dominant;<br>$V_{TXD} = 0 \text{ V}$ ; short-circuit on bus lines;<br>$-3 \text{ V} \le V_{CANH} = V_{CANL} \le +18 \text{ V}$ |                             |     | 85                       | mA   |

| Pin V <sub>EXT</sub> ; V   | Voltage Output External                                  |                                                                                                                                                                               |                             |     |                          |      |

| Vo                         | Output Voltage                                           | 6.2 V ≤ V <sub>BAT</sub> ≤ 40 V; I <sub>EXT</sub> ≤ 150 mA                                                                                                                    | 4.9                         | 5   | 5.1                      | ٧    |

| R <sub>ON_BAT</sub> -      | On Resistance between $V_{BAT}$<br>Pin and $V_{EXT}$ Pin | $4.5 \text{ V} \le \text{V}_{\text{BAT}} \le 6.2 \text{ V};$<br>$5 \text{ mA} \le \text{I}_{\text{EXT}} \le 150 \text{ mA}$                                                   |                             |     | 11                       | Ω    |

| V <sub>UVD_OUT2</sub>      | V <sub>EXT</sub> Under-Voltage Detection<br>Voltage      |                                                                                                                                                                               | 4.45                        |     |                          | V    |

| V <sub>UVR_OUT2</sub>      | V <sub>EXT</sub> Under-Voltage Recovery Voltage          |                                                                                                                                                                               |                             |     | 4.8                      | V    |

| V <sub>OVD</sub> OUT2      | V <sub>EXT</sub> Over-Voltage Detection<br>Voltage       |                                                                                                                                                                               | 5.2                         |     |                          | V    |

| V <sub>OVR_OUT2</sub>      | V <sub>EXT</sub> Over-Voltage Recovery Voltage           |                                                                                                                                                                               |                             |     | 5.5                      | V    |

| I <sub>O_SC</sub>          | Short-Circuit Output Current                             |                                                                                                                                                                               | -300                        |     | -150                     | mA   |

| Pin LIMP;                  | Limp-Home Output                                         |                                                                                                                                                                               |                             |     |                          |      |

| Vo                         | Output Voltage                                           | I <sub>LIMP</sub> = 0.8 mA; LHC = 1                                                                                                                                           |                             |     | 0.4                      | V    |

| I <sub>LO</sub>            | Output Leakage Current                                   | 0 V ≤ V <sub>LIMP</sub> ≤ 28 V; LHC = 0                                                                                                                                       | -5                          |     | 5                        | μA   |

| Pin SDI, S                 | CK and SCSN; Serial Peripher                             | al Inputs                                                                                                                                                                     |                             |     |                          |      |

| V <sub>TH_SW</sub>         | Switching Threshold Voltage                              |                                                                                                                                                                               | 0.25 ×<br>V <sub>OUT1</sub> |     | 0.75 × V <sub>OUT1</sub> | V    |

| V <sub>TH_SW_HY</sub>      | Switching Threshold Voltage<br>Hysteresis                |                                                                                                                                                                               | 0.05 ×<br>V <sub>OUT1</sub> |     |                          | V    |

| R <sub>PD_SCK</sub>        | Pull-down Resistance on SCK<br>Pin                       |                                                                                                                                                                               | 40                          | 60  | 80                       | kΩ   |

| R <sub>PU_SCSN</sub>       | Pull-up Resistance on SCSN<br>Pin                        |                                                                                                                                                                               | 40                          | 60  | 80                       | kΩ   |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Symbol                 | Parameter                     | Condition                                                                            | Min     | Тур | Max    | Unit |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------------------|--------------------------------------------------------------------------------------|---------|-----|--------|------|--|--|

| Reu_S80   Pull-up Resistance on SDI Pin   Vi = Vouri                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R <sub>PD_SDI</sub>    |                               |                                                                                      | 40      | 60  | 80     | kΩ   |  |  |

| Cit         Input Capacitance (¹)         V₁ = Vour¹¹         3         6         pF           Pin SDO;         Serial Peripheral Output           Voit         High-Level Output Voltage         IoH = -4 mA         Vour¹¹ - 0.4         V         V           Voit         Low-Level Output Voltage         IoL = 4 mA         0.4         V         V           Ico_orp         Off-State Output Leakage Current         VSCS_N = VOUT¹; VSDO = 0 V Or VOUT¹         -5         5         pp           PIN TXD; CAN Transmit Data Input         VTH_TXD         Switching Threshold Voltage         0.25 × VOUT¹         0.05 × VOUT¹         VOUT¹         V           VINYS_TAX         Plysteresis Voltage on Pin TXD         0.05 × VOUT¹         0.05 × VOUT¹         V         V           Reu_TXD         Pull-up Resistance         10 + = 4 mA         0.05 × VOUT¹         V         V           Vol.         Low-Level Output Voltage         IoH = -4 mA         VOUT¹ - 0.4         V         V           Reu_RXD         Pull-up Resistance on RXD Pin         Pull-up Resistance on RXD Pin         A0         80         80         Ω           VIN_WAKE_A         Pall-up Resistance on RXD Pin         Pull-up Resistance on RXD Pin         A2.8         4.1         V           VI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Reu soi                |                               |                                                                                      | 40      | 60  | 80     | kΩ   |  |  |

| Pin SDO: Serial Peripheral Output         Von         High-Level Output Voltage         Ion = -4 mA         Vout1 = 0.4         V           Vo.         Low-Level Output Voltage         Ion = 4 mA         Vout1 = 0.4         V         V           Vo.         Low-Level Output Leakage Current         VSCS_N = VOUT1; VSDO = 0 V or VOUT1         -5         5         1         µA           CO_SDO         Output Capacitance (1)         VSCS_N = VOUT1         -5         3         6         pF           PIN TXD; CAN Transmit Data Input         VSCS_N = VOUT1         -5         0.25 x VOUT1         V         0.75 x VOUT1         V         0.75 x VOUT1         V         0.75 x VOUT1         V         V         0.25 x VOUT1         0.05 x VOUT1         V         V         V         V         0.05 x VOUT1         V         V         V         V         V         0.05 x VOUT1         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                        |                               | VI = VOLIT1                                                                          |         |     |        |      |  |  |

| Von         High-Level Output Voltage         Ioh = -4 mA         Vout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                        |                               |                                                                                      |         |     |        |      |  |  |

| Von.         High-Level Output Voltage         Iow = -4 mA         0.4         V         V           Vol.         Low-Level Output Voltage         IoL = 4 mA         0.4         V         0.4         V           Lo_0.6FF         Off-State Output Leakage Current         Vscs_N = Vourt; Vsco = 0 V or Vourt         -5         5         μA           Co_sbo         Output Capacitance (1)         Vscs_N = Vourt; Vsco = 0 V or Vourt         -5         5         μA           Pin TXD: CAN Transmit Data Input           VIND Transmit Data Input           Vint_Txxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 020,                   |                               |                                                                                      | Vouta - |     |        |      |  |  |

| ILO_OFF   Off-State Output Leakage Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | V <sub>OH</sub>        | High-Level Output Voltage     | I <sub>OH</sub> = -4 mA                                                              |         |     |        | V    |  |  |

| Lo_OFF   Current   VSCS_N = VOUTI; VSDO = U V OT VOUTI   TS   TS   PA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | VoL                    | Low-Level Output Voltage      | I <sub>OL</sub> = 4 mA                                                               |         |     | 0.4    | V    |  |  |

| Pin TXD; CAN Transmit Data Input           V <sub>TH_TXD</sub> Switching Threshold Voltage         0.25 × VOUTI         0.75 × VOUTI         V           V <sub>HYS_TXD</sub> Hysteresis Voltage on Pin TXD         0.05 × VOUTI         V           RPU_TXD         Pull-up Resistance         40         60         80         kΩ           Pin RXD; CAN Receive Data Output         Vount         High-Level Output Voltage         IoH = -4 mA         Vount         0.4         V           Vo.         Low-Level Output Voltage         IoH = -4 mA         40         60         80         Ω           Pin WAKE; Local Wake Input         VITH_WAKE         Rising Switching Threshold Voltage         2.8         4.1         V           VITH_WAKE Input         Falling Switching Threshold Voltage         2.8         4.1         V           VHYS_WAKE Fellow         Hysteresis Voltage on WAKE Fin         250         800         mV           VHYS_WAKE Fin         Input Current         1.0 V ≤ VOUT1 ≤ 5.5 V; pull-up resistor to VouT1 ≥ 900 Ω         0         0.2 × VOUT1         VOUT1           RPU_RSTN Pull-up Resistance         1.0 V ≤ VOUT1 ≤ 5.5 V; pull-up resistor to VouT1 ≥ 900 Ω         0         0.25 × VOUT1         VOUT1         VOUT1         VOUT1         VOUT1         VOUT1         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I <sub>LO_OFF</sub>    |                               | V <sub>SCS_N</sub> = V <sub>OUT1</sub> ; V <sub>SDO</sub> = 0 V or V <sub>OUT1</sub> | -5      |     | 5      | μΑ   |  |  |

| $V_{TH\_TXD}$ Switching Threshold Voltage0.25 × VourtVourtV $V_{HYS\_TXD}$ Hysteresis Voltage on Pin TXD0.05 × Vourt0.05 × VourtV $R_{PU\_TXD}$ Pull-up Resistance406080 $K\Omega$ Pin RXD; CAN Receive Data Output $V_{OH}$ High-Level Output Voltage $I_{OH} = -4 \text{ mA}$ $V_{OUT1} = -6 \text{ mA}$ V0.4 $V_{OH}$ Vol.Low-Level Output Voltage $I_{OH} = -4 \text{ mA}$ $V_{OH}$ 406080 $\Omega$ Pin WARE; Local Wake InputVTH_WAKE Receive Data Wake InputRising Switching Threshold Voltage2.84.1 $V_{OH}$ VTH_WAKE Receive Data Wake Input2.84.1 $V_{OH}$ VTH_WAKE Receive Data Wake Input2.84.1 $V_{OH}$ VHYS_WAKE Pain Resistance Receive Data Wake Receive Data Wake Receive Data Re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | C <sub>O_SDO</sub>     | Output Capacitance (1)        | V <sub>SCS_N</sub> = V <sub>OUT1</sub>                                               |         | 3   | 6      | pF   |  |  |

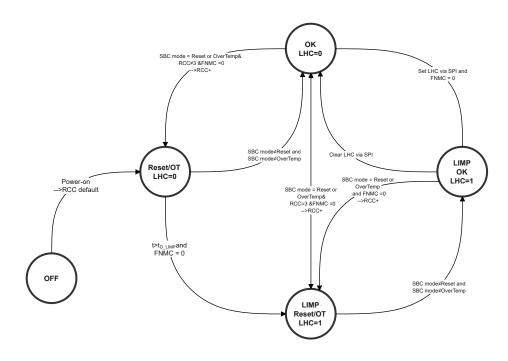

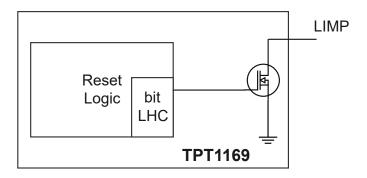

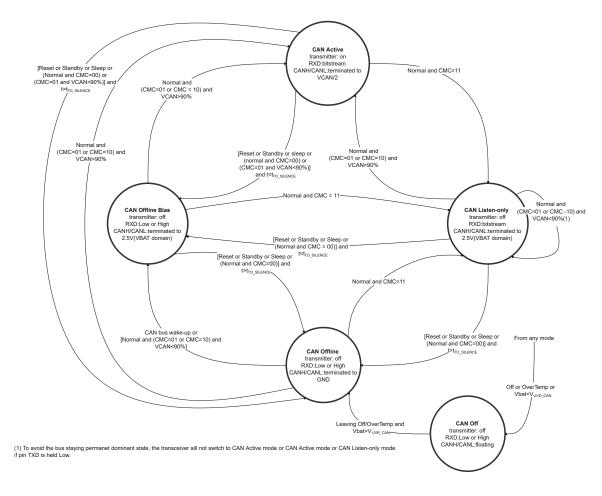

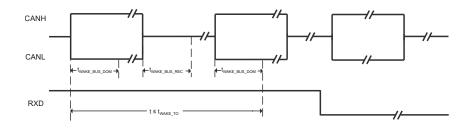

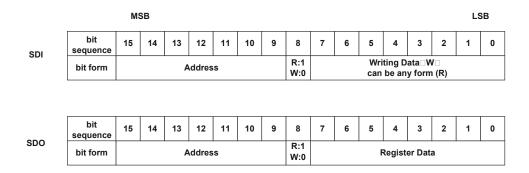

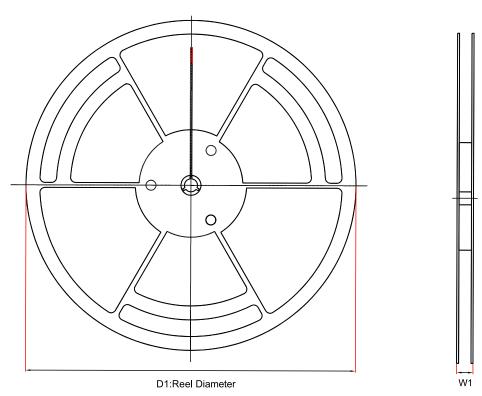

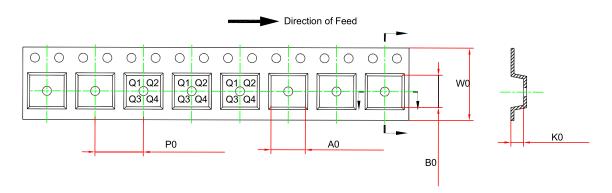

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Pin TXD;               | CAN Transmit Data Input       |                                                                                      |         |     |        |      |  |  |