### **Features**

- Compliant to LIN 2.0, LIN 2.1, LIN 2.2, LIN 2.2A and ISO 17987-4 Electrical Physical Layer (EPL) Specification

- Compliant to SAE J2602 LIN Network for Vehicle Applications

- Support LIN Data Rates up to 20 Kbps

- Wide V<sub>BAT</sub> Input Voltage Range Supports 5.5 V to 40 V

- Low-current Standby Mode and Sleep Mode with Bus Wake-up Capability

- Input Levels Compatible with 3.3 V and 5 V MCU Interface

- Ideal Passive Behavior to LIN Bus when Unpowered

- Integrated Pull-up Resistor for LIN Slave Applications

- · Protection Feature :

- Bus Pin IEC 61000-4-2 ESD Protection ±10 kV

- Bus Fault-Tolerant: ±45 V

- V<sub>BAT</sub> Undervoltage Protection

- TXD Dominant Time-out Function

- Thermal Shutdown Protection

- Available in the SOP14 Package and Leadless DFN3X4.5-14L Package with Improved Automated Optical Inspection (AOI) Capability

- AEC-Q100 Qualified for Automotive Applications, Grade 1

## **Applications**

- Automotive and Transportation

- Body Electronics / Lighting

- Power Train / Chassis

- Infotainment / Cluster

- ADAS / Safety

### **Description**

The TPT1022Q is a dual local interconnect network (LIN) physical layer transceiver that is compliant with the ISO 17987-4, SAE J2602 and LIN 2.0, LIN 2.1, LIN 2.2, and LIN 2.2-A physical layer standard. LIN is a low-speed Universal Asynchronous Receiver Transmitter (UART) communication protocol that supports automotive in-vehicle sub-networks.

The device supports LIN networks up to 20 Kbps with an enhanced timing margin. The device converts the transmitted data received at the TXD with an optimized slew rate to minimize the electro-magnetic emission (EME) and reports the state of the LIN bus at the RXD.

As designed, the device features overvoltage and loss of ground protection from -45 V to +45 V, over-temperature shutdown. The device has low-current standby and sleep mode with LIN BUS wake-up capability. The device integrates a pull high resistor for LIN slave applications and ESD protection which allows applications to operate with a reduced dependence on external components. Additionally, all devices include many protection features to enhance the device and network robustness.

The TPT1022Q is available in SOP-14 and DFN3X4.5-14L packages and is AEC-Q100 qualified for automotive applications.

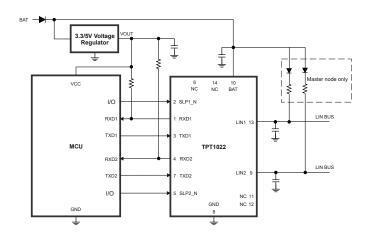

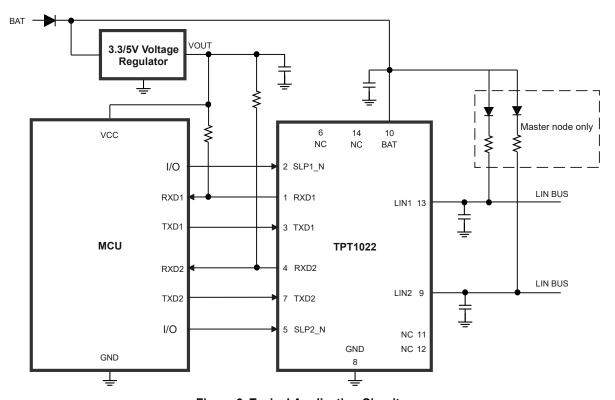

## **Typical Application Circuit**

## **Table of Contents**

| Features                                 | 1  |

|------------------------------------------|----|

| Applications                             |    |

| Description                              | 1  |

| Typical Application Circuit              | 1  |

| Revision History                         | 3  |

| Pin Configuration and Functions          | 4  |

| Specifications                           | 5  |

| Absolute Maximum Ratings <sup>(1)</sup>  | 5  |

| ESD (Electrostatic Discharge Protection) | 5  |

| Recommended Operating Conditions         | 6  |

| Thermal Information                      | 6  |

| Electrical Characteristics               | 7  |

| Duty Cycles                              | 9  |

| AC Timing Requirements                   | 10 |

| Parameter Measurement Information        | 11 |

| Test Circuit                             | 11 |

| Parameter Diagram                        | 11 |

| Detailed Description                     | 13 |

| Overview                                 | 13 |

| Functional Block Diagram                 | 13 |

| Feature Description                      | 14 |

| Device Operating Modes                   | 14 |

| Protection Features                      | 15 |

| Application and Implementation           | 17 |

| Typical Application                      | 17 |

| Tape and Reel Information                | 18 |

| Package Outline Dimensions               | 19 |

| DFN4.5X3-14-WET-B                        | 19 |

| SOP14                                    | 20 |

| Order Information                        | 21 |

| IMPORTANT NOTICE AND DISCLAIMER          | 22 |

## **Revision History**

| Date       | Revision  | Notes            |

|------------|-----------|------------------|

| 2022-12-05 | Rev.Pre.0 | Initial version  |

| 2024-2-25  | Rev.A.0   | Released version |

| 2024-7-30  | Rev.A.1   | Typo correction  |

www.3peak.com 3 / 22 CA20240704A1

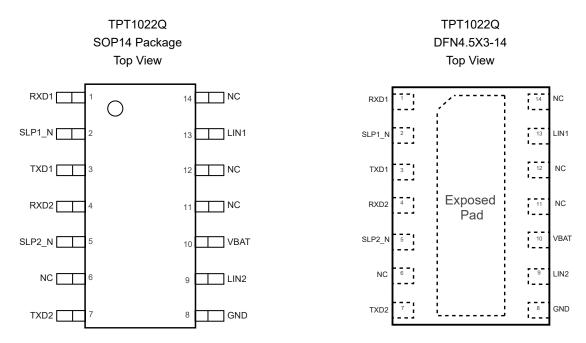

## **Pin Configuration and Functions**

Table 1. Pin Functions: TPT1024Q

| Р   | Pin    |         |                                            |  | D |

|-----|--------|---------|--------------------------------------------|--|---|

| No. | Name   | I/O     | Description                                |  |   |

| 1   | RXD1   | Output  | LIN1 receive data output                   |  |   |

| 2   | SLP1_N | Input   | LIN1 sleep mode control input, active low  |  |   |

| 3   | TXD1   | Input   | LIN1 transmit data input                   |  |   |

| 4   | RXD2   | Output  | LIN2 receive data output                   |  |   |

| 5   | SLP2_N | Input   | LIN2 sleep mode control input, active low  |  |   |

| 6   | NC     | NC      | Not connected                              |  |   |

| 7   | TXD2   | Input   | LIN2 transmit data input                   |  |   |

| 8   | GND    | Ground  | Ground                                     |  |   |

| 9   | LIN2   | Bus I/O | LIN2 bus input/output line                 |  |   |

| 10  | VBAT   | Power   | High voltage power supply from the battery |  |   |

| 11  | NC     | NC      | Not connected                              |  |   |

| 12  | NC     | NC      | Not connected                              |  |   |

| 13  | LIN1   | Bus I/O | LIN1 bus input/output line                 |  |   |

| 14  | NC     | NC      | Not connected                              |  |   |

www.3peak.com 4 / 22 CA20240704A1

## **Specifications**

## Absolute Maximum Ratings (1)

| Parameter          |                                   | Conditions                                         | Min  | Max | Unit |

|--------------------|-----------------------------------|----------------------------------------------------|------|-----|------|

| $V_{BAT}$          | Battery Supply Voltage Range      |                                                    | -0.3 | 45  | V    |

| $V_{TXD}$          | Pin TXD Voltage Range             | Pin TXDx                                           | -0.3 | 7   | V    |

| $V_{RXD}$          | Pin RXD Voltage Range             | Pin RXDx                                           | -0.3 | 7   | V    |

| V <sub>SLP_N</sub> | Pin SLP_N Voltage Range           | Pin SLPx_N                                         | -0.3 | 7   | V    |

| V <sub>LIN</sub>   | Pin LIN Voltage Range             | Pin LINx, with respect to GND and V <sub>BAT</sub> | -45  | 45  | V    |

| \DV LIN1-<br>LIN2  | Voltage between Pin LIN1 and LIN2 |                                                    | -    | 45  | V    |

| TJ                 | Junction Temperature (2)          |                                                    | -55  | 150 | °C   |

| T <sub>STG</sub>   | Storage Temperature               |                                                    | -55  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

### **ESD (Electrostatic Discharge Protection)**

| Parameter         |                                            | Condition                                                                           | Min  | Max | Unit |

|-------------------|--------------------------------------------|-------------------------------------------------------------------------------------|------|-----|------|

|                   | Electrostatics Discharge <sup>(1)(2)</sup> | IEC61000-4-2(150pF, 330Ω discharge circuit), contact discharge on LIN bus LINx pins | -10  | 10  | kV   |

| V <sub>ESD</sub>  |                                            | Human Body Model (HBM) on LIN bus LINx pins                                         | -10  | 10  | kV   |

|                   |                                            | Human Body Model (HBM) on any other pins                                            | -6   | 6   | kV   |

|                   |                                            | Charged Device Model (CDM) on all pins                                              | -1.5 | 1.5 | kV   |

|                   |                                            | Pulse1                                                                              | -100 | -   | V    |

| V <sub>TRAN</sub> | Transient Immunity ISO 7637-2 on           | Pulse2a                                                                             | -    | 75  | V    |

|                   | Bus Pins                                   | Pulse3a                                                                             | -150 | -   | V    |

|                   |                                            | Pulse3b                                                                             | -    | 100 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

www.3peak.com 5 / 22 CA20240704A1

<sup>(2)</sup> This data was taken with the JEDEC standard multilayer test boards.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## **Recommended Operating Conditions**

|                    | Parameter                                    | Min | Max  | Unit |

|--------------------|----------------------------------------------|-----|------|------|

| $V_{BAT}$          | Battery Power Supply                         | 5.5 | 40   | V    |

| V <sub>LIN</sub>   | LIN Bus Input Voltage                        | 0   | 40   | V    |

| V <sub>LOGIC</sub> | Logic Pin Voltage                            | 0   | 5.25 | V    |

| TJ                 | Operating Virtual Junction Temperature Range | -40 | 150  | °C   |

## **Thermal Information**

| Package Type | θ <sub>JA</sub> | θυς   | Unit |

|--------------|-----------------|-------|------|

| SOP14        | 85.6            | 34.24 | °C/W |

| DFN4.5x3-14  | 40.07           | 39.49 | °C/W |

www.3peak.com 6 / 22 CA20240704A1

### **Electrical Characteristics**

All test conditions:  $V_{BAT}$  = 5.5 V to 40 V,  $R_L$  = 500  $\Omega$ ,  $T_A$  = -40°C to 125°C, unless otherwise noted.

|                             | Parameter                                               | Conditions                                                                                                  | Min  | Тур | Max  | Unit |

|-----------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| Pin VBAT                    |                                                         |                                                                                                             |      |     |      |      |

| V <sub>TH_DET_PO</sub>      | Power-off Detection Threshold                           |                                                                                                             | 1.6  | 3.1 | 4.0  | V    |

| V <sub>TH_DET_PO</sub>      | Power-on Detection Threshold                            |                                                                                                             | 2.3  | 3.4 | 4.3  | V    |

| $V_{\text{HYS\_DET\_P}}$ on | Hysteresis Voltage on Power-on Detection <sup>(1)</sup> |                                                                                                             | 50   | 300 | 1000 | mV   |

| V <sub>TH_VBAT_L</sub>      | Low-level VBAT Low Threshold Voltage                    |                                                                                                             | 3.3  | 4   | 4.7  | V    |

| Vтн_vват_н                  | High-level VBAT Low Threshold Voltage                   |                                                                                                             | 3.55 | 4.2 | 4.9  | V    |

| V <sub>HYS_VBAT_L</sub>     | VBAT Low Hysteresis Voltage (1)                         |                                                                                                             | 15   | 300 | 600  | mV   |

|                             | Sleep Made Supply Current                               | Recessive; $V_{LINX} = V_{BAT}$ ; $V_{SLPX_N}$<br>= 0 V; both channels                                      |      | 7   | 12   | μA   |

|                             | Sleep Mode Supply Current                               | Dominant; $V_{LINX} = 0 \text{ V}$ ; $V_{BAT} = 12 \text{ V}$ ; $V_{SLPX\_N} = 0 \text{ V}$ ; both channels |      | 18  | 30   | μA   |

| ı                           | Standby Mode Supply Current                             | Recessive; $V_{LINx} = V_{BAT}$ ; $V_{SLPx\_N}$ = 0 V; both channels                                        |      | 7   | 20   | μA   |

| I <sub>BAT</sub>            |                                                         | Dominant; $V_{LINX} = 0 \text{ V}$ ; $V_{BAT} = 12 \text{ V}$ ; $V_{SLPX\_N} = 0 \text{ V}$ ; both channels |      | 0.8 | 1    | mA   |

|                             | Normal Mode Supply Current                              | Recessive; V <sub>LINX</sub> = V <sub>BAT</sub> ; V <sub>TXD</sub> = 5 V; V <sub>SLP_N</sub> = 5 V          |      | 0.3 | 0.6  | mA   |

|                             |                                                         | Dominant; $V_{BAT} = 12 \text{ V}$ ; $V_{TXD} = 0$ V; $V_{SLP\_N} = 5 \text{ V}$                            |      | 4   | 10   | mA   |

| Pin TXDx                    |                                                         |                                                                                                             |      |     |      |      |

| V <sub>IH</sub>             | High-Level Input Voltage                                |                                                                                                             | 2    |     | 7    | V    |

| $V_{IL}$                    | Low-Level Input Voltage                                 |                                                                                                             | -0.3 |     | 0.8  | V    |

| V <sub>HYS_TXD</sub>        | Hysteresis Voltage on Pin TXD (1)                       |                                                                                                             | 50   | 200 | 450  | mV   |

| R <sub>PD_TXD</sub>         | Pin TXD Pull-down Resistance                            | V <sub>TXD</sub> = 5 V                                                                                      | 50   | 125 | 325  | kΩ   |

| I <sub>IL</sub>             | Low-Level Input Current                                 | $V_{TXD} = 0 V$                                                                                             | -5   |     | 5    | μA   |

| Pin SLP_Nx                  |                                                         |                                                                                                             |      |     |      |      |

| V <sub>IH</sub>             | High-level Input Voltage                                |                                                                                                             | 2    |     | 7    | V    |

| $V_{IL}$                    | Low-level Input Voltage                                 |                                                                                                             | -0.3 |     | 0.8  | V    |

| V <sub>HYS_SLP_N</sub>      | Hysteresis Voltage on Pin SLP_N (1)                     |                                                                                                             | 50   | 200 | 450  | mV   |

| R <sub>PD_SLP_N</sub>       | Pin SLP_N Pull-down Resistance                          | V <sub>TXD</sub> = 5 V                                                                                      | 125  | 250 | 650  | kΩ   |

www.3peak.com 7 / 22 CA20240704A1

|                         | Parameter                                  | Conditions                                                                                | Min                         | Тур                       | Max                         | Unit |

|-------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------|---------------------------|-----------------------------|------|

| I <sub>IL</sub>         | Low-level Input Current                    | $V_{TXD} = 0 V$                                                                           | -5                          |                           | 5                           | μA   |

| Pin RXDx                |                                            |                                                                                           |                             |                           |                             |      |

| loL                     | Low-level Output Current                   | Normal mode; V <sub>LIN</sub> = 0 V, V <sub>RXDX</sub> = 0.4 V                            | 2                           |                           |                             | mA   |

| I <sub>LH</sub>         | High-level Leakage Current (1)             | Normal mode; $V_{LIN} = V_{BAT}$ , $V_{RXD}$<br>= 5 V                                     | -5                          | 0                         | 5                           | μA   |

| Pin LIN                 |                                            |                                                                                           |                             |                           |                             |      |

| I <sub>BUS_LIN</sub>    | Dominant Output Current<br>Limitation      | V <sub>BAT</sub> = V <sub>LIN</sub> = 18 V; V <sub>TXDx</sub> = 0 V                       | 40                          |                           | 200                         | mA   |

| I <sub>PU_SLP</sub>     | Pull-up Current                            | Sleep mode; V <sub>SLP_N</sub> = 0 V                                                      | -20                         |                           | -2                          | μA   |

| I <sub>BUS_PAS_RE</sub> | Receiver Recessive Input Leakage Current   | V <sub>BAT</sub> = 5.5 V; V <sub>LIN</sub> = 40 V; V <sub>TXD</sub> = 5 V                 |                             | 0                         | 20                          | μΑ   |

| IBUS_PAS_DO             | Receiver Dominant Input Leakage<br>Current | Normal mode; $V_{BAT} = 12 \text{ V}$ ; $V_{LIN} = 0 \text{ V}$ ; $V_{TXD} = 5 \text{ V}$ | -600                        |                           |                             | μΑ   |

| V <sub>SerDiode</sub>   | Voltage Drop at the Serial Diode           | Pull-up path with R <sub>SLAVE</sub> ; I <sub>SerDiode</sub> = 10 μA                      | 0.4                         |                           | 1                           | V    |

| I <sub>BUS_NO_GN</sub>  | Ground Loss Bus Current                    | V <sub>BAT</sub> = 40 V; V <sub>LIN</sub> = 0 V                                           | -750                        |                           | 10                          | μΑ   |

| I <sub>BUS_NO_BAT</sub> | Battery Loss Bus Current                   | V <sub>BAT</sub> = 0 V; V <sub>LIN</sub> = 40 V                                           |                             |                           | 20                          | μA   |

| V <sub>BUS_PAS_D</sub>  | Receiver Dominant                          |                                                                                           |                             |                           | 0.4 x<br>V <sub>BAT</sub>   | V    |

| V <sub>BUS_PAS_R</sub>  | Receiver Recessive                         |                                                                                           | 0.6 x<br>V <sub>BAT</sub>   |                           |                             | V    |

| V <sub>BUS_CNT</sub>    | Receiver Center Voltage                    |                                                                                           | 0.475 x<br>V <sub>BAT</sub> | 0.5 x<br>V <sub>BAT</sub> | 0.525 x<br>V <sub>BAT</sub> | V    |

| V <sub>HYS</sub>        | Receiver Hysteresis Voltage                |                                                                                           |                             |                           | 0.175 x<br>V <sub>BAT</sub> | V    |

| R <sub>SLAVE</sub>      | Slave Resistance                           | Between LIN and VBAT; V <sub>BAT</sub> = 12 V; V <sub>LIN</sub> = 0 V                     | 20                          | 30                        | 60                          | kΩ   |

| C <sub>LIN</sub>        | Pin LIN Capacitance (1)                    |                                                                                           |                             |                           | 20                          | pF   |

| V <sub>O_DOM</sub>      | Dominant Output Voltage                    | Normal mode; V <sub>TXD</sub> = 0 V                                                       |                             |                           | 1.4                         | V    |

| Temperature Detection   |                                            |                                                                                           |                             |                           |                             |      |

| T <sub>J_SD</sub>       | Shutdown Junction Temperature (1)          |                                                                                           | 160                         | 180                       | 200                         | °C   |

| T <sub>J_SD_R</sub>     | Recover Shutdown Junction Temperature (1)  |                                                                                           | 130                         | 145                       | 160                         | °C   |

<sup>(1)</sup> The data is based on bench tests and design simulation.

www.3peak.com 8 / 22 CA20240704A1

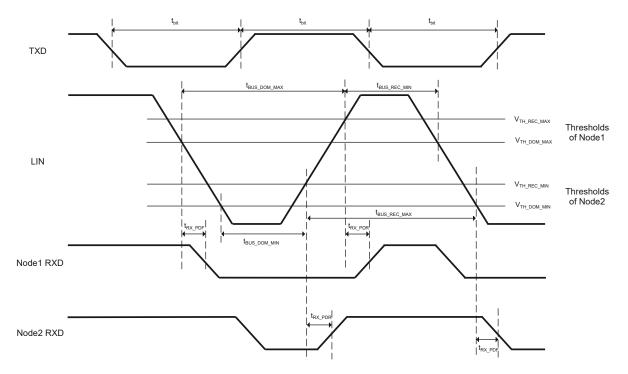

## **Duty Cycles**

All test conditions:  $V_{BAT}$ = 5.5 V to 40 V,  $R_L$ = 500  $\Omega$ ,  $T_A$ = -40°C to 125°C, see Figure 2, unless otherwise noted.

| Parar | neter                                                             | Conditions                                                                                                                                                                                                                | Min   | Тур | Max   | Unit |

|-------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|------|

| D1    | Duty cycle 1; D1= t <sub>BUS_REC_MIN</sub> / 2 x t <sub>BIT</sub> | $V_{TH\_REC\_MAX}$ = 0.744 x $V_{BAT}$ ; $V_{TH\_DOM\_MAX}$ = 0.581 x $V_{BAT}$ ; 20 kbps; $t_{BIT}$ = 50 $\mu$ s; $T_{ABT}$ $V_{ABT}$ $V_{ABT}$ $V_{ABT}$ $V_{ABT}$                                                      | 0.396 |     |       |      |

| D1    | Duty cycle 1; D1= t <sub>BUS_REC_MIN</sub> / 2 x t <sub>BIT</sub> | $V_{TH\_REC\_MAX} = 0.744 \text{ x } V_{BAT};$<br>$V_{TH\_DOM\_MAX} = 0.581 \text{ x } V_{BAT};$<br>$20 \text{ kbps}; t_{BIT} = 50  \mu\text{s};$<br>$5.5 \text{ V} \leq V_{BAT} < 7 \text{ V}$                           | 0.396 |     |       |      |

| D2    | Duty cycle 2; D2= t <sub>BUS_REC_MAX</sub> / 2 x t <sub>BIT</sub> | V <sub>TH_REC_MIN</sub> = 0.422 x V <sub>BAT</sub> ;<br>V <sub>TH_DOM_MIN</sub> = 0.284 x V <sub>BAT</sub> ;<br>20 kbps; t <sub>BIT</sub> = 50 µs;<br>7.6 V ≤ V <sub>BAT</sub> ≤ 40 V                                     |       |     | 0.581 |      |

| D2    | Duty cycle 2; D2= t <sub>BUS_REC_MAX</sub> / 2 x t <sub>BIT</sub> | $V_{TH\_REC\_MIN}$ = 0.464 x $V_{BAT}$ ; $V_{TH\_DOM\_MIN}$ = 0.312 x $V_{BAT}$ ; 20 kbps; $t_{BIT}$ = 50 $\mu$ s; 5.5 $V \le V_{BAT} < 7.6 V$                                                                            |       |     | 0.581 |      |

| D3    | Duty cycle 3; D3= t <sub>BUS_REC_MIN</sub> / 2 x t <sub>BIT</sub> | $\begin{split} &V_{TH\_REC\_MAX} = 0.778 \text{ x } V_{BAT};\\ &V_{TH\_DOM\_MAX} = 0.616 \text{ x } V_{BAT};\\ &10.4 \text{ kbps; } t_{BIT} = 96  \mu\text{s;}\\ &7 \text{ V} \leq V_{BAT} \leq 40 \text{ V} \end{split}$ | 0.417 |     |       |      |

| D3    | Duty cycle 3; D3= t <sub>BUS_REC_MIN</sub> / 2 x t <sub>BIT</sub> | $V_{TH\_REC\_MAX} = 0.778 \text{ x } V_{BAT};$ $V_{TH\_DOM\_MAX} = 0.616 \text{ x } V_{BAT};$ $10.4 \text{ kbps}; t_{BIT} = 96 \text{ \mus};$ $5.5 \text{ V} \leq V_{BAT} < 7 \text{ V}$                                  | 0.417 |     |       |      |

| D4    | Duty cycle 4; D4= t <sub>BUS_REC_MAX</sub> / 2 x t <sub>BIT</sub> | $V_{TH\_REC\_MIN}$ = 0.389 x $V_{BAT}$ ; $V_{TH\_DOM\_MIN}$ = 0.251 x $V_{BAT}$ ; 10.4 kbps; $t_{BIT}$ = 96 $\mu$ s; 7.6 $V \le V_{BAT} \le 40V$                                                                          |       |     | 0.590 |      |

| D4    | Duty cycle 4; D4= t <sub>BUS_REC_MAX</sub> / 2 x t <sub>BIT</sub> | $V_{TH\_REC\_MIN} = 0.389 \text{ x V}_{BAT};$ $V_{TH\_DOM\_MIN} = 0.251 \text{ x V}_{BAT};$ $10.4 \text{ kbps}; t_{BIT} = 96 \mu\text{s};$ $5.5 \text{ V} \leq V_{BAT} < 7.6 \text{ V}$                                   |       |     | 0.590 |      |

www.3peak.com 9 / 22 CA20240704A1

## **AC Timing Requirements**

All test conditions:  $V_{BAT}$  = 5.5 V to 40 V,  $R_L$  = 500  $\Omega$ ,  $T_A$  = -40°C to 125°C, unless otherwise noted. unless otherwise noted.

|                         | Parameter                              | Conditions                                                    | Min | Тур | Max | Unit |

|-------------------------|----------------------------------------|---------------------------------------------------------------|-----|-----|-----|------|

| t <sub>RX_PD</sub>      | Receiver Propagation Delay             | Rising and falling                                            |     |     | 6   | μs   |

| t <sub>RX_SYM</sub>     | Receiver Propagation Delay<br>Symmetry | Rising edge with respect to falling edge                      | -2  |     | 2   | μs   |

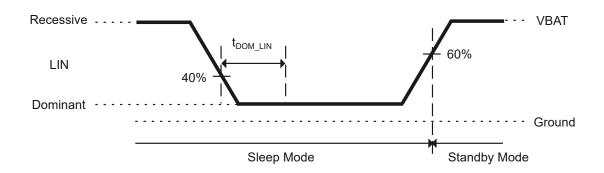

| twake_dom_lin           | LIN Dominant Wake-up Time              | Sleep mode                                                    | 30  | 80  | 150 | μs   |

| tgotonorm               | Go-to-Normal Time                      | Mode change time from Sleep,<br>Standby mode into Normal mode | 2   | 5   | 10  | μs   |

| t <sub>INITNORM</sub>   | Normal Mode Initialization Time        |                                                               | 7   | 12  | 20  | μs   |

| tgotosleep              | Go-to-Sleep Time                       | Mode change time from Normal into Sleep mode                  | 2   | 5   | 10  | μs   |

| t <sub>TO_DOM_TXD</sub> | TXD dominant time-out time             | V <sub>TXD</sub> = 0 V                                        | 17  | 30  | 50  | ms   |

<sup>(1)</sup> The data is based on bench tests and design simulation.

www.3peak.com 10 / 22 CA20240704A1

## **Parameter Measurement Information**

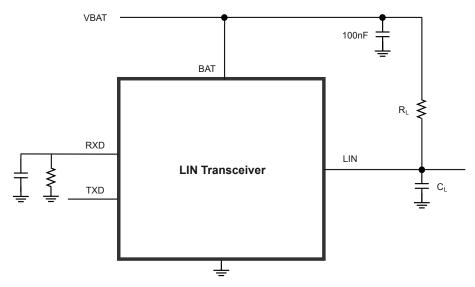

### **Test Circuit**

Figure 1. LIN Transceiver Timing Parameter Test Circuit

## **Parameter Diagram**

Figure 2. LIN Transceiver Timing Diagram

www.3peak.com 11 / 22 CA20240704A1

Figure 3. Remote Wake-up Diagram

www.3peak.com 12 / 22 CA20240704A1

### **Detailed Description**

### Overview

The TPT1022Q is a dual local interconnect network (LIN) physical layer transceiver that is compliant with the ISO 17987-4, SAE J2602 and LIN 2.0, LIN 2.1, LIN 2.2, and LIN 2.2-A physical layer standard. LIN is a low-speed universal asynchronous receiver transmitter (UART) communication protocol that supports automotive in-vehicle sub-networks. The device supports LIN networks up to 20 Kbps with an enhanced timing margin. The device converts the transmitted data received at the TXD with an optimized slew rate to minimize the electro-magnetic emission (EME) and reports the state of the LIN bus at the RXD. As designed, the device features overvoltage and loss of ground protection from ~45 V to +45 V, over-temperature shutdown. The device has low-current standby and sleep mode with LIN BUS wake-up capability. The device integrates a pull high resistor for LIN slave applications and ESD protection which allows applications to operate with a reduced dependence on external components. Additionally, all devices include many protection features to enhance the device and network robustness. The TPT1022Q is available in SOP-14 and DFN3X4.5-14L packages and is AEC-Q100 qualified for automotive applications.

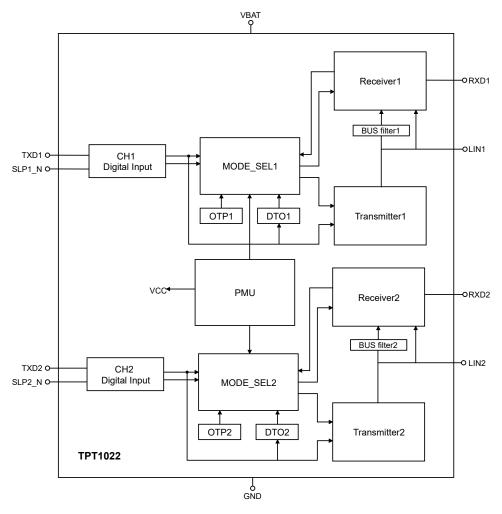

### **Functional Block Diagram**

Figure 4. Functional Block Diagram

www.3peak.com 13 / 22 CA20240704A1

### **Feature Description**

### **Device Operating Modes**

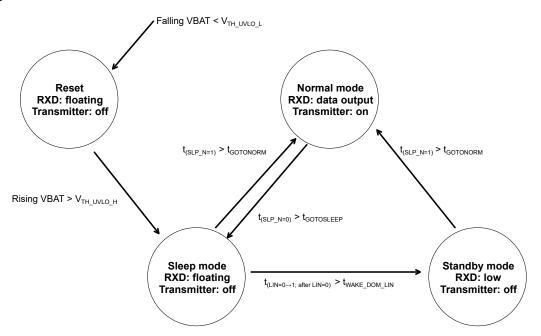

The TPT1022Q supports modes for normal mode, power-on mode, standby mode, and sleep mode. The figure below shows the state diagram.

Figure 5. State Diagram

**Table 2. Operation Mode Table**

| Mode    | SLP_Nx | TXDx                                      | RXDx                                      | Transmitter | Comments                  |

|---------|--------|-------------------------------------------|-------------------------------------------|-------------|---------------------------|

| Normal  | High   | High: recessive state Low: dominant state | High: recessive state Low: dominant state | Normal      |                           |

| Sleep   | Low    | Weak pull-down                            | Floating                                  | Off         | No wake-up event detected |

| Standby | Low    | Weak pull-down                            | Low                                       | Off         | Wake-up event detected    |

#### **Normal Mode**

In Normal mode, the device can transmit and receive data through the LIN bus line. The receiver detects the data stream at the LIN bus input pin and transfers it to the microcontroller via the RXD pin. On the bus, a HIGH level corresponds to a recessive state, while a LOW level represents a dominant state. The receiver incorporates a voltage-dependent threshold with hysteresis and an integrated filter to suppress noise on the bus.

The transmit data stream from the protocol controller at the TXD input is converted by the transmitter into a bus signal with optimized slew rate and wave shaping, aiming to minimize electromagnetic emissions (EME). The LIN bus output pin is pulled HIGH through an internal slave termination resistor. For master applications, an external resistor in series with a diode should be connected between pin VBAT and pin LIN.

www.3peak.com 14 / 22 CA20240704A1

### Sleep Mode

The device offers an energy-efficient mode known as the power-saving mode. Despite its extremely low current consumption, the device retains the capability to be remotely awakened via the LIN pin or directly activated through the SLP\_N pin. Input filters are incorporated at the receiver (LIN), and SLP\_N pin to prevent undesired wake-up events caused by automotive transients or electromagnetic interference (EMI).

To initiate Sleep mode from Normal mode, a falling edge on the SLP\_N pin is required. In order to successfully enter Sleep mode, the sleep command (SLP\_N pin set to LOW) must be sustained for a minimum duration of tgotosleep.

During Sleep mode, the internal slave termination between the LIN and VBAT pins is disabled to minimize power dissipation if the LIN pin is short-circuited to ground. Only a weak pull-up is present between the LIN and VBAT pins.

When VBAT voltage drops below the undervoltage threshold, the device transitions into Sleep mode.

#### **Standby Mode**

Whenever a local or remote wake-up occurs while the device is in Sleep mode, Standby mode is automatically activated. These wake-up events enable the slave termination resistor at the LIN pin.

Standby mode is indicated by a low level on the RXD pin, which can serve as an interrupt for the microcontroller.

#### Wake-up

When VBAT voltage exceeds the undervoltage threshold voltage, the device transitions into Sleep mode. In this mode, both the transmitter and receiver remain inactive. If SLP\_N is HIGH for a duration greater than t\_gotonorm, the device enters Normal mode.

To wake up a device that is in Sleep mode, there are two methods:

Remote wake-up through the LIN bus by receiving a dominant bus state that is sustained for a duration of at least  $t_{WAKE\ DOM\ LIN}$  then followed by a rising edge.

Mode change by setting the SLP\_N pin to a HIGH level. This change in pin state signals the device to exit Sleep mode and enter Normal mode.

### **Protection Features**

#### **TXD Dominant Time-out**

The device will detect TXD dominant time-out and prevent a permanent low on pin TXD driving the LIN bus into permanent dominant blocking the LIN bus network. If the TXD remains low for longer than  $t_{TXD\_DTO}$  the transmitter will disable until the fault flag has been cleared.

### **Under-voltage Lockout (UVLO)**

The device integrated under-voltage detect and lockout circuit of the supply terminal to keep the device in protected mode if the supply voltage drops below the threshold until the supply voltage is higher than the UVLO threshold. This protects the device and system during undervoltage events on supply terminals.

### **Over-Temperature Protection (OTP)**

The output drivers are protected against overtemperature conditions. If the virtual junction temperature exceeds the shutdown junction temperature  $T_{J\_SD}$ , the output drivers will be disabled until the virtual junction temperature falls below  $T_{J\_SD\_R}$  and TXD becomes recessive again. Including the TXD condition ensures that output driver oscillation due to temperature drift is avoided.

### Fail-safe Features

An internal pull-down to GND on the TXD pin to establish a predetermined level in case the TXD pin is disconnected.

www.3peak.com 15 / 22 CA20240704A1

An internal pull-down to GND on the SLP\_N pin to establish a predetermined level in case the SLP\_N pin is disconnected.

The RXD pin is set to floating when the VBAT pin is unpowered.

The current limit is applied to LIN transmitter output to protect LIN bus short circuits to VBAT or GND

VBAT and GND loss will not impact the LIN bus or the MCU. No reverse current flow from the bus into pin LIN. The internal integrated LIN slave termination resistor remains to keep the current path from VBAT to LIN. Disconnecting the LIN transceiver from the power supply does not affect the LIN bus.

www.3peak.com 16 / 22 CA20240704A1

## **Application and Implementation**

### Note

Information in the following application sections is not part of the 3PEAK's component specification and 3PEAK does not warrant its accuracy or completeness. 3PEAK's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### **Typical Application**

Figure 6. Typical Application Circuit

www.3peak.com 17 / 22 CA20240704A1

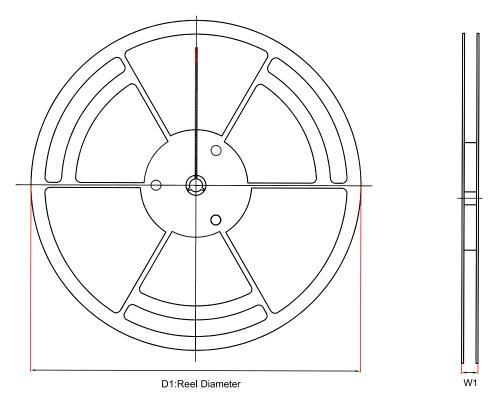

## **Tape and Reel Information**

| Order Number    | Package     | D1<br>(mm) | W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | W0<br>(mm) | Pin1<br>Quadrant |

|-----------------|-------------|------------|------------|------------|------------|------------|------------|------------|------------------|

| TPT1022Q-DFKR-S | DFN4.5X3-14 | 330        | 17.6       | 3.3        | 4.8        | 1.1        | 8          | 12         | Q1               |

| TPT1022Q-SO2R-S | SOP-14      | 330        | 21.6       | 6.5        | 9.0        | 2.1        | 8          | 16         | Q1               |

www.3peak.com 18 / 22 CA20240704A1

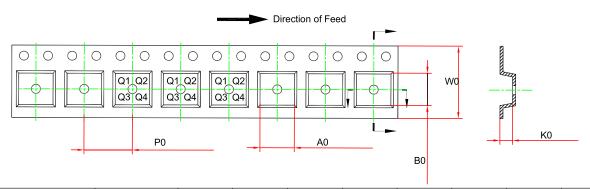

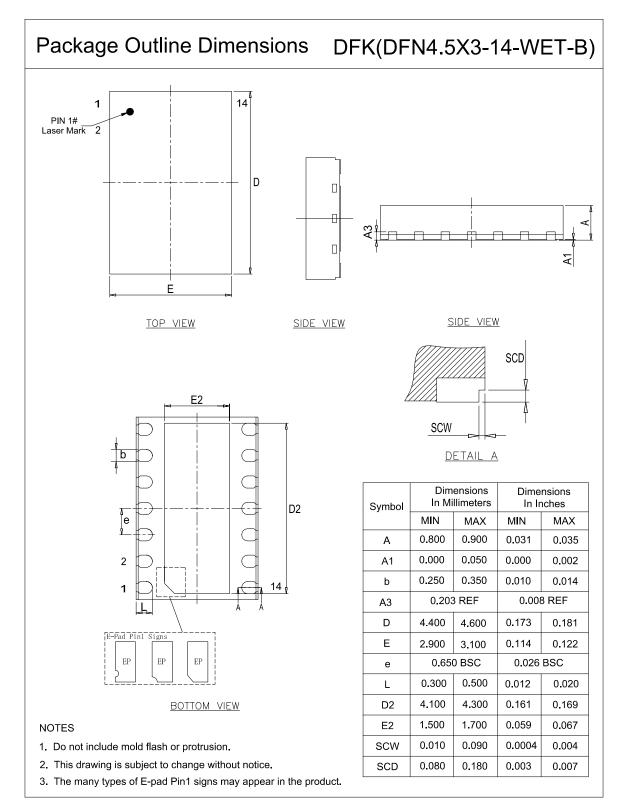

## **Package Outline Dimensions**

### **DFN4.5X3-14-WET-B**

### SOP14

www.3peak.com 20 / 22 CA20240704A1

### **Order Information**

| Orde   | r Number   | Operating Temperature Package |             | Marking Information | MSL  | Transport Media, Quantity | Eco Plan |

|--------|------------|-------------------------------|-------------|---------------------|------|---------------------------|----------|

| TPT102 | 22Q-DFKR-S | −40 to 125°C                  | DFN4.5X3-14 | 1022Q               | MSL1 | Tape and Reel,4000        | Green    |

| TPT102 | 22Q-SO2R-S | -40 to 125°C                  | SOP-14      | 1022Q               | MSL1 | Tape and Reel,2500        | Green    |

**Green**: 3PEAK defines "Green" to mean RoHS compatible and free of halogen substances.

www.3peak.com 21 / 22 CA20240704A1

### IMPORTANT NOTICE AND DISCLAIMER

Copyright<sup>©</sup> 3PEAK 2012-2025. All rights reserved.

**Trademarks.** Any of the 思瑞浦 or 3PEAK trade names, trademarks, graphic marks, and domain names contained in this document /material are the property of 3PEAK. You may NOT reproduce, modify, publish, transmit or distribute any Trademark without the prior written consent of 3PEAK.

**Performance Information.** Performance tests or performance range contained in this document/material are either results of design simulation or actual tests conducted under designated testing environment. Any variation in testing environment or simulation environment, including but not limited to testing method, testing process or testing temperature, may affect actual performance of the product.

**Disclaimer.** 3PEAK provides technical and reliability data (including data sheets), design resources (including reference designs), application or other design recommendations, networking tools, security information and other resources "As Is". 3PEAK makes no warranty as to the absence of defects, and makes no warranties of any kind, express or implied, including without limitation, implied warranties as to merchantability, fitness for a particular purpose or non-infringement of any third-party's intellectual property rights. Unless otherwise specified in writing, products supplied by 3PEAK are not designed to be used in any life-threatening scenarios, including critical medical applications, automotive safety-critical systems, aviation, aerospace, or any situations where failure could result in bodily harm, loss of life, or significant property damage. 3PEAK disclaims all liability for any such unauthorized use.

www.3peak.com 22 / 22 CA20240704A1