### **Features**

Wide Input Voltage Range

Normal Operation: 5 V to 75 V

- Maximum: 100 V Transient

External N-channel MOSFET Driver

Charge Pump with Integrated Capacitor

- Gate Driver for External N-Channel MOSFET

13-mV V<sub>SD</sub> for Regulated Conduction Mode

-10-mV V<sub>SD</sub> for Reverse Current Blocking

1.9-A Sink Current to Turn-off NMOS

Dedicate OFF Pin for MOSFET Test Function

· Fast Reverse Current Blocking: 25 ns typical

SOT23-6 Package

### **Applications**

- · Industry Control, Factory Automation

- Server, Network, and Enterprise Power Supply

- · Active OR-ing for Redundant Power Supplies

### **Description**

The TPS75R01B is an ideal diode controller that operates with an external N-channel MOSFET for reverse protection applications or redundant power supply applications. The forward voltage drop is controlled at as low as 13 mV, which can significantly reduce power loss to replace an ordinary Schottky Diode in power distribution networks.

The TPS75R01B supports a wide operating voltage range from 5 V to 75 V, with an absolute maximum rating of 100 V. The support for a transient 100-V input voltage is particularly suitable to meet the severe requirements in 48-V power supply systems.

The TPS75R01B integrates a charge pump to drive the external N-channel MOSFET. The device provides precise gate control to regulate the voltage drop between the source and drain at 13 mV. When it detects a reverse voltage of −10 mV from IN to OUT, the TPS75R01B turns off the external MOSFET within 25 ns typical to ensure no reverse current flows. The TPS75R01B also features a MOSFET test mode. It allows the MCU controller to test the shorted MOSFET.

The TPS75R01B provides a small SOT23-6 package, and it is qualified to operate within the junction temperature range from  $-40^{\circ}$ C to  $+125^{\circ}$ C.

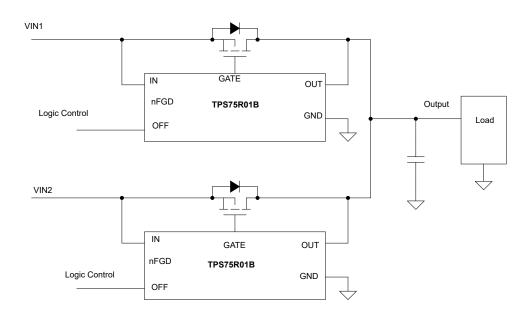

## **Typical Application Circuit**

## **Table of Contents**

| Features                                | 1  |

|-----------------------------------------|----|

| Applications                            | 1  |

| Description                             | 1  |

| Typical Application Circuit             | 1  |

| Product Family Table                    | 3  |

| Revision History                        | 3  |

| Pin Configuration and Functions         | 4  |

| Specifications                          | 5  |

| Absolute Maximum Ratings (1) (2) (3)    | 5  |

| ESD, Electrostatic Discharge Protection | 5  |

| Recommended Operating Conditions        | 5  |

| Thermal Information                     | 5  |

| Electrical Characteristics              | 6  |

| Typical Performance Characteristics     | 8  |

| Detailed Description                    | 10 |

| Overview                                | 10 |

| Functional Block Diagram                | 10 |

| Feature Description                     | 11 |

| Application and Implementation          | 13 |

| Application Information                 | 13 |

| Typical Application                     | 13 |

| Layout                                  | 14 |

| Layout Guideline                        | 14 |

| Layout Example                          | 14 |

| Tape and Reel Information               | 15 |

| Package Outline Dimensions              | 16 |

| SOT23-6                                 | 16 |

| Order Information                       | 17 |

| IMPORTANT NOTICE AND DISCLAIMED         | 10 |

# **Product Family Table**

| Order Number     | Voltage Range (V) | Regulated Forward<br>Voltage (mV) | Reverse Protection<br>Threshold (mV) | Package |

|------------------|-------------------|-----------------------------------|--------------------------------------|---------|

| TPS75R01B-S6TR-S | 5 to 75           | 13                                | -10                                  | SOT23-6 |

## **Revision History**

| Date       | Revision | Notes            |

|------------|----------|------------------|

| 2025-11-15 | Rev.A.0  | Initial release. |

www.3peak.com 3 / 18 DA20250901A0

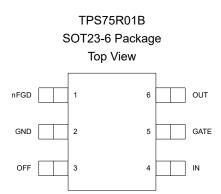

# **Pin Configuration and Functions**

Table 1. Pin Functions: TPS75R01B

| Pin No. | Pin Name | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5       | GATE     | 0   | Gate drive output pin. Connect this pin to the gate of the external N-channel MOSFET.                                                                                                                                                                                                                                                                                                                                                                              |

| 2       | GND      | -   | Ground reference pin.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4       | IN       | I   | Input supply voltage sense pin. Connect this pin to the source of the external N-channel MOSFET.                                                                                                                                                                                                                                                                                                                                                                   |

| 1       | nFGD     | 0   | External MOSFET test open-drain output pin. Combined with the OFF pin to achieve the MOSFET test function. When the OFF pin is logic high, an active low output of nFGD indicates the forward voltage from source to drain of the MOSFET is greater than 350 mV, and the MOSFET is not shorted. Left this pin open when the MOSFET test function is not used. Pull up this pin to a voltage below 5.5 V through an external resistor for the MOSFET test function. |

| 3       | OFF      | I   | External MOSFET test control pin. When the OFF pin is logic low or left open, the MOSFET test function is disabled. When the OFF pin is logic high, the GATE pin is pulled down and MOSFET is turned off, and the MOSFET test function is enabled.                                                                                                                                                                                                                 |

| 6       | OUT      | I   | Output voltage sense pin. Connect this pin to the drain of the external N-channel MOSFET.                                                                                                                                                                                                                                                                                                                                                                          |

www.3peak.com 4 / 18 DA20250901A0

## **Specifications**

### Absolute Maximum Ratings (1) (2) (3)

|                  | Parameter                           | Min  | Max | Unit |

|------------------|-------------------------------------|------|-----|------|

| IN, OUT          |                                     | -0.3 | 100 | V    |

| GATE             |                                     | -0.3 | 100 | V    |

| OFF              |                                     | -0.3 | 7   | V    |

| nFGD             |                                     | -0.3 | 7   | V    |

| TJ               | Junction Temperature Range          | -40  | 150 | °C   |

| T <sub>A</sub>   | Ambient Temperature Range           | -40  | 125 | °C   |

| T <sub>STG</sub> | Storage Temperature Range           | -65  | 150 | °C   |

| TL               | Lead Temperature (Soldering 10 sec) |      | 260 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

### **ESD, Electrostatic Discharge Protection**

| Parameter |                          | Condition                  | Minimum Level | Unit |

|-----------|--------------------------|----------------------------|---------------|------|

| НВМ       | Human Body Model ESD     | ANSI/ESDA/JEDEC JS-001 (1) | ±4            | kV   |

| CDM       | Charged Device Model ESD | ANSI/ESDA/JEDEC JS-002 (2) | ±1.5          | kV   |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### **Recommended Operating Conditions**

|                   | Parameter                  | Min | Max | Unit |

|-------------------|----------------------------|-----|-----|------|

| V <sub>IN</sub>   | DC Power Supply Voltage    | 5   | 75  | V    |

| V <sub>OUT</sub>  | Output Voltage             | 5   | 75  | V    |

| Voff              | OFF Control Voltage        | 0   | 5.5 | V    |

| V <sub>nFGD</sub> | MOSFET Status Output       | 0   | 5.5 | V    |

| TJ                | Junction Temperature Range | -40 | 125 | °C   |

#### **Thermal Information**

| Package Type | θ <sub>JA</sub> | <b>Ө</b> ЈВ <b>Ө</b> ЈС,ТОР |    | Unit |

|--------------|-----------------|-----------------------------|----|------|

| SOT23-6      | 155             | 48                          | 81 | °C/W |

www.3peak.com 5 / 18 DA20250901A0

<sup>(2)</sup> All voltage values are with respect to GND.

<sup>(3)</sup> Not subject to production test, specified by design.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **Electrical Characteristics**

All test conditions:  $T_J = -40$ °C to +125°C; typical values at  $T_J = 25$ °C,  $V_{IN} = 12$  V,  $V_{OUT} = 12$  V,  $V_{OFF} = 0$  V,  $C_{GATE} = 47$  nF, over operating free-air temperature range, unless otherwise noted.

|                                | Parameter                                                                          | Conditions                                                                                                  | Min | Тур   | Max | Unit |

|--------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----|-------|-----|------|

| IN Pin                         |                                                                                    |                                                                                                             |     |       |     |      |

| V <sub>IN</sub>                | Supply Input Voltage                                                               |                                                                                                             | 5   |       | 75  | V    |

| - III                          |                                                                                    | $V_{IN} = 5 \text{ V}, V_{OUT} = V_{IN} - 100 \text{ mV},$<br>GATE = OPEN                                   |     | 287   | 390 | μA   |

| I <sub>IN</sub>                | Supply Input Current                                                               | V <sub>IN</sub> = 12 V, V <sub>OUT</sub> = V <sub>IN</sub> - 100 mV,<br>GATE = OPEN                         |     | 412   | 525 | μA   |

|                                |                                                                                    | $V_{IN}$ = 75 V, $V_{OUT}$ = $V_{IN}$ – 100 mV, GATE = OPEN                                                 |     | 415   | 525 | μA   |

| OUT Pin                        |                                                                                    |                                                                                                             |     |       |     |      |

|                                |                                                                                    | V <sub>IN</sub> = 5 V, V <sub>OUT</sub> = V <sub>IN</sub> - 100 mV                                          |     | 78    | 110 | μA   |

| I <sub>OUT</sub>               | OUT Pin Current                                                                    | V <sub>IN</sub> = 12 V, V <sub>OUT</sub> = V <sub>IN</sub> - 100 mV                                         |     | 90    | 120 | μA   |

|                                |                                                                                    | V <sub>IN</sub> = 75 V, V <sub>OUT</sub> = V <sub>IN</sub> – 100 mV                                         |     | 107   | 180 | μA   |

| Gate Pin                       |                                                                                    |                                                                                                             |     |       |     |      |

|                                |                                                                                    | V <sub>IN</sub> = 5 V, V <sub>GATE</sub> = V <sub>IN</sub> , V <sub>OUT</sub> = V <sub>IN</sub><br>- 175 mV | 60  | 95    | 130 | μA   |

| I <sub>GATE</sub> ,ON          | GATE Pin Source Current                                                            | $V_{IN} = 12 \text{ V to } 75 \text{ V, V}_{GATE} = V_{IN},$<br>$V_{OUT} = V_{IN} - 175 \text{ mV}$         | 70  | 95    | 130 | μA   |

| I <sub>GATE,OFF</sub>          | Gate Pin Sink Current                                                              | V <sub>GATE</sub> = V <sub>IN</sub> + 3 V, V <sub>OUT</sub> > V <sub>IN</sub> + 100 mV, t ≤ 10 ms           |     | 1.9   |     | Α    |

|                                |                                                                                    | V <sub>IN</sub> = 5 V, V <sub>GATE</sub> = V <sub>IN</sub> , V <sub>OUT</sub> = V <sub>IN</sub><br>- 175 mV | 4   | 7.9   | 9   | V    |

| V <sub>GS</sub> <sup>(1)</sup> | V <sub>GATE</sub> – V <sub>IN</sub> in Forward Operation                           | V <sub>IN</sub> = 12 V, V <sub>GATE</sub> = V <sub>IN</sub> , V <sub>OUT</sub> = V <sub>IN</sub> - 175 mV   | 8   | 10.5  | 14  | V    |

|                                |                                                                                    | V <sub>IN</sub> = 75 V, V <sub>GATE</sub> = V <sub>IN</sub> , V <sub>OUT</sub> = V <sub>IN</sub> - 175 mV   | 8   | 10.5  | 14  | V    |

| $V_{\text{SD,REG}}$            | Regulated Forward V <sub>SD</sub><br>Threshold, V <sub>IN</sub> > V <sub>OUT</sub> | V <sub>IN</sub> – V <sub>OUT</sub>                                                                          | 3   | 11.8  | 23  | mV   |

| $V_{\text{SD,REV}}$            | Reverse V <sub>SD</sub> Threshold, V <sub>IN</sub> < V <sub>OUT</sub>              | V <sub>IN</sub> – V <sub>OUT</sub>                                                                          | -17 | -10.2 | -2  | mV   |

| $\Delta V_{\text{SD,REV}}$     | Reverse V <sub>SD</sub> Hysteresis                                                 |                                                                                                             |     | -     |     | mV   |

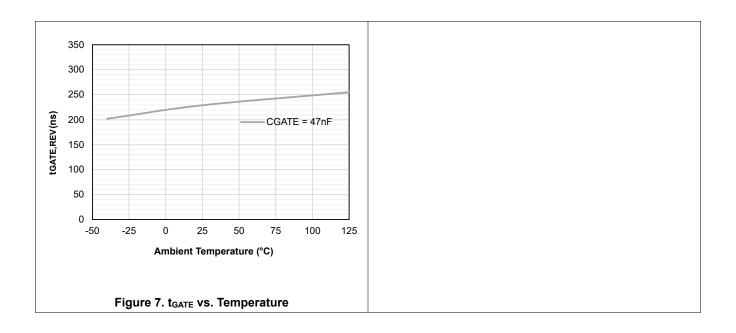

|                                | Gate Capacitance Discharge                                                         | C <sub>GATE</sub> = 0                                                                                       |     | 25    | 100 | ns   |

| t <sub>GATE,REV</sub> (2)      | Time at Forward to Reverse                                                         | C <sub>GATE</sub> = 10 nF                                                                                   |     | 80    |     | ns   |

| (4)                            | Transition                                                                         | C <sub>GATE</sub> = 47 nF                                                                                   |     | 260   | 425 | ns   |

| t <sub>GATE,OFF</sub> (2)      | Gate Capacitance Discharge Time at OFF Pin Low to High Transition                  | C <sub>GATE</sub> = 47 nF                                                                                   |     | 450   |     | ns   |

www.3peak.com 6 / 18 DA20250901A0

|                      | Parameter                                                                         | Conditions                                                                            | Min | Тур   | Max  | Unit |

|----------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----|-------|------|------|

| OFF Pin              |                                                                                   |                                                                                       |     |       |      |      |

| V <sub>OFF,IH</sub>  | OFF Input High-Level Voltage                                                      | V <sub>OUT</sub> = V <sub>IN</sub> - 500 mV, V <sub>OFF</sub><br>Rising               |     | 1.55  | 1.75 | V    |

| Voff,iL              | OFF Input Low-Level Voltage                                                       | V <sub>OUT</sub> = V <sub>IN</sub> - 500 mV, V <sub>OFF</sub><br>Falling              | 1.1 | 1.4   |      | V    |

| $\Delta V_{OFF}$     | OFF Threshold Voltage<br>Hysteresis                                               | V <sub>OFF,IH</sub> - V <sub>OFF,IL</sub>                                             |     | 160   |      | mV   |

| l <sub>OFF</sub>     | OFF Pin Internal Pulldown<br>Current                                              | V <sub>OFF</sub> = 5 V                                                                |     | 5     | 8    | μA   |

| nFGD Pin             |                                                                                   |                                                                                       |     |       |      |      |

| V <sub>SD,TEST</sub> | FET Source-to-Drain Test<br>Threshold Voltage, V <sub>IN</sub> < V <sub>OUT</sub> | V <sub>OFF</sub> = 5 V, V <sub>OUT</sub> = 12 V, V <sub>IN</sub><br>Falling from 12 V |     | 332   | 450  | mV   |

| $\Delta V_{SD,TEST}$ | FET Source-to-Drain Test Threshold Voltage Hysteresis                             |                                                                                       |     | 85    |      | mV   |

| $V_{OL,nFGD}$        | nFGD Output Low Voltage, nFGD<br>Output = On                                      | V <sub>OFF</sub> = 5 V, I <sub>nFGD</sub> = 1 mA Sinking                              |     | 5     | 400  | mV   |

| I <sub>OL,nFGD</sub> | nFGD Output Leakage Current,<br>nFGD Output = Off                                 | V <sub>OFF</sub> = 0 V, V <sub>nFGD</sub> = 5.5 V                                     |     | 0.001 | 1    | μA   |

<sup>(1)</sup> Measurement of VGS voltage (i.e., VGATE – VIN) includes 1 M $\Omega$  in parallel with CGATE.

www.3peak.com 7 / 18 DA20250901A0

<sup>(2)</sup> Not subject to production test, specified by design.

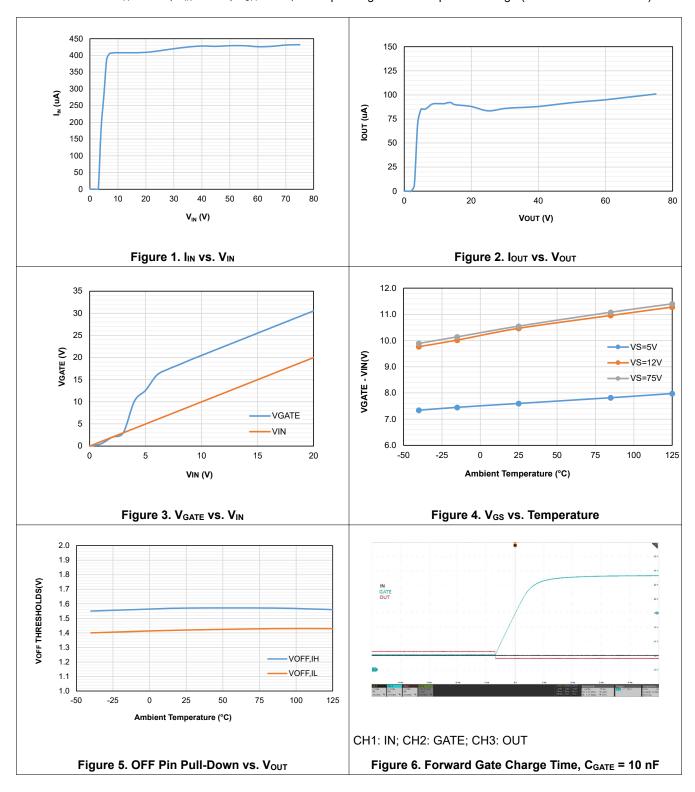

## **Typical Performance Characteristics**

All test conditions: T<sub>A</sub> = 25°C, V<sub>IN</sub> = 12 V, V<sub>OFF</sub> = 0 V, over operating free-air temperature range (unless otherwise noted).

www.3peak.com 8 / 18 DA20250901A0

### **Detailed Description**

#### Overview

The TPS75R01B is an ideal diode controller that operates with an external N-channel MOSFET for reverse protection applications or redundant power supply applications. The forward voltage drop is controlled as low as 13 mV, which can significantly reduce power loss to replace an ordinary Schottky Diode in power distribution networks.

The TPS75R01B supports a wide operating voltage range from 5 V to 75 V, with an absolute maximum rating of 100 V. The support for a transient 100-V input voltage is particularly suitable to meet the severe requirement in 48-V power supply systems.

The TPS75R01B integrates a charge pump to drive the external N-channel MOSFET. The device provides precise gate control to regulate the voltage drop between the source and drain at 13 mV. When it detects a reverse voltage of −10 mV from IN to OUT, the TPS75R01B will turn off the external MOSFET within 450 ns maximum to ensure no reverse current flows. The TPS75R01B also features a MOSFET test mode. It allows the MCU controller to test the shorted MOSFET.

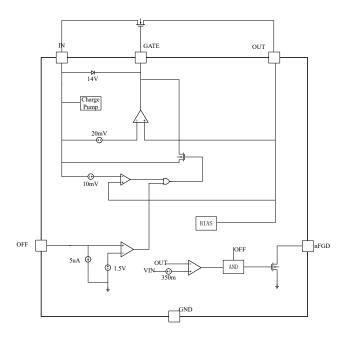

### **Functional Block Diagram**

Figure 8. Functional Block Diagram

www.3peak.com 10 / 18 DA20250901A0

### **Feature Description**

#### Input Power Supply Voltage (IN)

The TPS75R01B uses the IN pin to power up the internal circuitry with a supply voltage ranging from 5 V to 75 V. The maximum voltage range from IN to GND is 100 V.

#### In, Gate, and Out Pins

When power is first applied, the load current flows from source to drain through the MOSFET's body diode. The voltage across this diode is detected by the TPS75R01B's IN and OUT pins, and then the TPS75R01B starts charging the MOSFET gate via a 95  $\mu$ A (typical) charge pump current source. In normal operation, the MOSFET gate is charged until it's typically 10.5V above the IN pin. When the IN pin voltage is less than about 10V, the gate is charged to typically twice the IN pin voltage.

The TPS75R01B is designed to regulate the MOSFET gate-to-source voltage if the voltage across the MOSFET source and drain pins drops below the typical 13 mV  $V_{SD(REG)}$  voltage.

When the MOSFET current drops to the extent that the voltage across the MOSFET is below the typical 13 mV  $V_{SD(REG)}$  voltage regulation point, the GATE pin voltage is reduced until the voltage across the MOSFET is regulated at 13 mV. In case the drain-to-source voltage is higher than the VSD(REG) voltage, the gate-to-source voltage rises and eventually reaches the 10.5-V zener clamp level between the GATE and IN pins.

If the MOSFET current reverses, perhaps due to a failure of the input supply, and the voltage across the TPS75R01B IN and OUT pins becomes more negative than the typical -10 mV  $V_{SD(REV)}$  voltage, the TPS75R01B promptly discharges the MOSFET gate by means of a powerful GATE to IN pin discharge transistor.

When the input supply fails suddenly, like when it's directly shorted to the ground, a reverse current flows through the MOSFET temporarily until the gate is fully discharged. This reverse current comes from the output load capacitance and the parallel-connected supplies. The TPS75R01B typically responds to a voltage reversal condition within 25 ns. The actual time needed to turn off the MOSFET depends on the charge held by the gate capacitance of the MOSFET in use. For a MOSFET with an effective gate capacitance of 47 nF, it can typically be turned off in 260 ns. This fast turn-off time minimizes voltage disturbances at the output and reduces current transients from the redundant supplies.

#### Off Pin and nFGD Pin

The OFF pin serves as a logic level input pin, which is utilized for controlling the gate drive of the external MOSFET when in the FET Test Mode. Its maximum operating voltage is capped at 5.5V. The nFGD pin, on the other hand, is an open-drain output pin that can support a logic level voltage, and its maximum operating voltage is also 5.5 V.

When the OFF pin is at a high level, the MOSFET gets turned off regardless of the sensed IN and OUT voltages, and simultaneously, the FET Test Mode gets activated. In this mode, the load current flows through the body diode of the MOSFET. If the MOSFET is functioning normally via the body diode, the voltage difference between the IN pin and the OUT pin is around 700 mV. The FET test comparator of the TPS75R01B keeps an eye on the voltage difference between the IN and OUT pins, with a typical V<sub>SD(TST)</sub> threshold of 332 mV. If the voltage difference between the IN pin and the OUT pin is larger than this threshold, the nFGD pin shifts to a low impedance state and its voltage becomes a logic low.

In the event that the MOSFET is shorted, the voltage difference between the IN pin and the OUT pin is less than the  $V_{SD(TST)}$  threshold. Then, the nFGD pin stays in a high impedance state, and its pin voltage can be pulled high by an external pull-up resistor.

During normal operation, the OFF pin has to be pulled low or can be left open. In this situation, the GATE pin voltage relies on the forward or reverse voltage across the MOSFET from source to drain, as has been described before.

Typically, the OFF pin has an internal pull-down current of 5  $\mu$ A. If the OFF function isn't needed, this pin can either be left open or connected to the ground.

When the OFF pin is at a low level, the nFGD pin always remains in a high impedance open state.

www.3peak.com 11 / 18 DA20250901A0

There are several factors that can make the nFGD pin unable to show that the external MOSFET is operating normally. For example, when the TPS75R01B is employed to connect parallel and redundant power supplies, one of the connected supplies might keep the OUT pin voltage close enough to the IN pin voltage of the TPS75R01B so that the V<sub>SD(TST)</sub> threshold isn't exceeded. Moreover, when operating with a high output capacitance value and a low load current, it might take a considerable amount of time before the output capacitance is discharged to the point where the V<sub>SD(TST)</sub> threshold is surpassed and the nFGD pin switches to a low state.

#### **Short Circuit Failure of an Input Supply**

When there is an abrupt zero-ohm short circuit across the input supply, the highest possible reverse current flows as the internal control circuitry of the TPS75R01B discharges the gate of the MOSFET. During this period, the reverse current is restricted only by the on-resistance  $R_{DS(ON)}$  of the MOSFET along with the parasitic resistances and inductances of the wiring. The worst-case instantaneous reverse current is limited in accordance with the following formula:

$$I_{D(REV)} = (V_{OUT} - V_{IN}) / R_{DS(ON)}$$

(1)

The internal Reverse Comparator responds and initiates the process of discharging the Gate when the reverse current reaches the level determined by this formula:

$$I_{D(REV)} = V_{SD(REV)} / R_{DS(ON)}$$

(2)

Once the MOSFET is finally turned off, the energy stored in the parasitic wiring inductances is transferred to the rest of the circuit. Consequently, the TPS75R01B IN pin experiences a negative voltage spike while the OUT pin has a positive voltage spike. To protect the IN pin, it can be diode-clamped to the ground in the negative direction. For the OUT pin, it can be safeguarded by using a transient voltage suppression (TVS) protection diode, a local bypass capacitor, or both. In low-voltage applications, the drain-to-source breakdown voltage rating of the MOSFET might be sufficient to protect the OUT pin. However, since most MOSFET datasheets don't specify the maximum breakdown rating clearly, this method should be employed with caution.

**Table 2. FET Test Status Table**

| OFF Pin      | Mode                | FET Gate Drive | VIN - VOUT             | FET Status | nFGD Pin<br>Status | nFGD Pin<br>Voltage |

|--------------|---------------------|----------------|------------------------|------------|--------------------|---------------------|

| Low or Open  | Normal<br>Operation | Active         | -                      | -          | High Z             | High                |

| High FET Te: | FET Test Off        | 0#             | > V <sub>SD(TST)</sub> | OK         | Low Z              | Low                 |

|              |                     | Oil            | < V <sub>SD(TST)</sub> | Not OK     | High Z             | High                |

www.3peak.com 12 / 18 DA20250901A0

## **Application and Implementation**

#### Note

Information in the following application sections is not part of the 3PEAK's component specification and 3PEAK does not warrant its accuracy or completeness. 3PEAK's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### **Application Information**

The TPS75R01B is an ideal diode controller operating with an external N-channel MOSFET for reverse protection and redundant power supplies applications. The following Typical Application section shows a typical usage of the TPS75R01B.

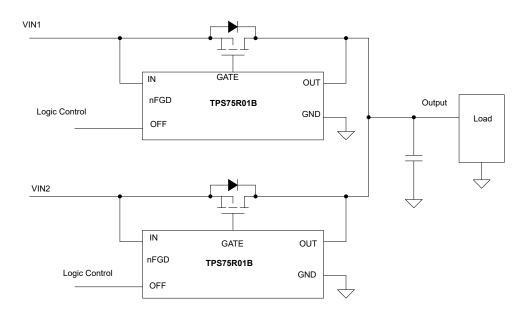

### **Typical Application**

Figure 9. Typical Application

www.3peak.com 13 / 18 DA20250901A0

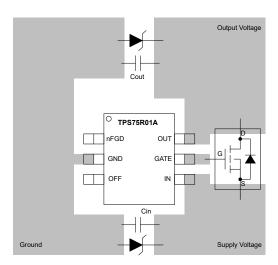

## Layout

### **Layout Guideline**

- Connect the IN, GATE, and OUT pins of TPS75R01B close to the source, gate, and drain pins of the external N-channel MOSFET.

- Connect the GATE pin of TPS75R01B to the gate pin of the external N-channel MOSFET with short and wide traces to avoid turn-off delay due to the trace resistance.

- For the high current path through the external N-channel MOSFET, it is recommended to use wide trace lengths or thick copper weight to minimize I×R drop and heat dissipation.

### **Layout Example**

Figure 10. Layout Example

www.3peak.com 14 / 18 DA20250901A0

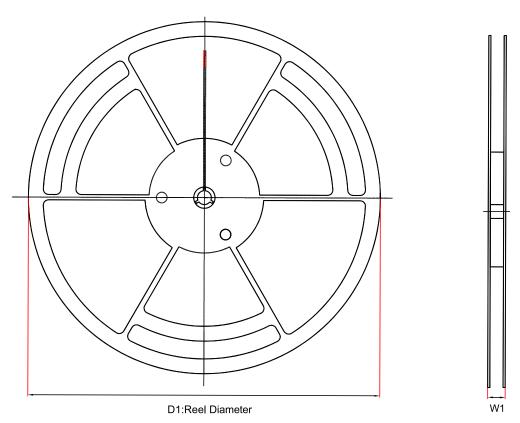

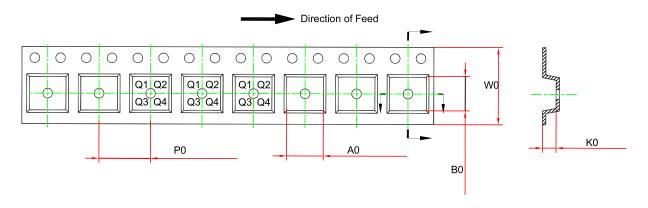

## **Tape and Reel Information**

| Order Number     | Package | D1<br>(mm) | W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | W0<br>(mm) | Pin1<br>Quadrant |

|------------------|---------|------------|------------|------------|------------|------------|------------|------------|------------------|

| TPS75R01B-S6TR-S | SOT23-6 | 180        | 12         | 3.3        | 3.2        | 1.4        | 4          | 8          | Q3               |

www.3peak.com 15 / 18 DA20250901A0

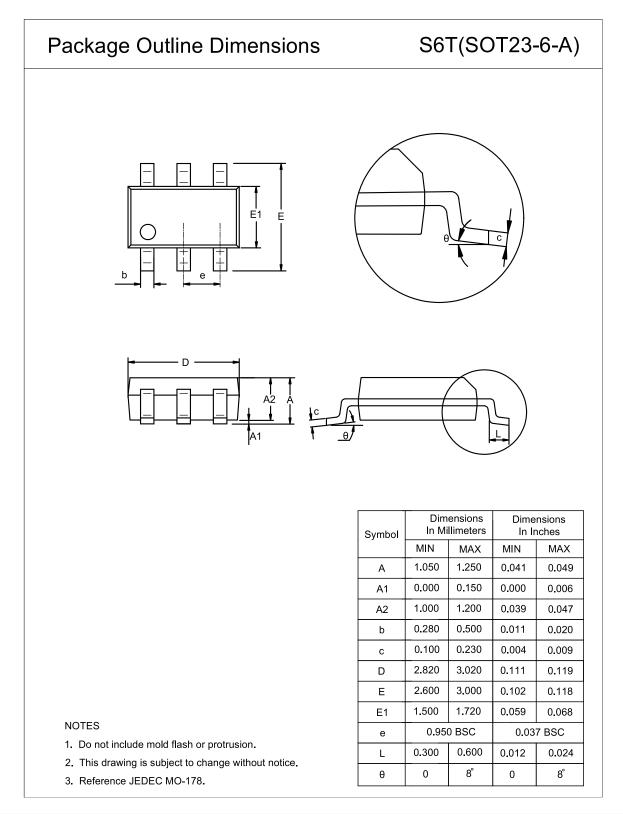

## **Package Outline Dimensions**

### SOT23-6

www.3peak.com 16 / 18 DA20250901A0

### **Order Information**

| Order Number     | Operating Temperature Range | Package | Marking Information | MSL  | Transport Media, Quantity | Eco Plan |

|------------------|-----------------------------|---------|---------------------|------|---------------------------|----------|

| TPS75R01B-S6TR-S | -40 to 125°C                | SOT23-6 | S7B                 | MSL2 | Tape and Reel,3000        | Green    |

**Green**: 3PEAK defines "Green" to mean RoHS compatible and free of halogen substances.

www.3peak.com 17 / 18 DA20250901A0

### IMPORTANT NOTICE AND DISCLAIMER

Copyright<sup>©</sup> 3PEAK 2012-2025. All rights reserved.

**Trademarks.** Any of the 思瑞浦 or 3PEAK trade names, trademarks, graphic marks, and domain names contained in this document /material are the property of 3PEAK. You may NOT reproduce, modify, publish, transmit or distribute any Trademark without the prior written consent of 3PEAK.

**Performance Information.** Performance tests or performance range contained in this document/material are either results of design simulation or actual tests conducted under designated testing environment. Any variation in testing environment or simulation environment, including but not limited to testing method, testing process or testing temperature, may affect actual performance of the product.

**Disclaimer.** 3PEAK provides technical and reliability data (including data sheets), design resources (including reference designs), application or other design recommendations, networking tools, security information and other resources "As Is". 3PEAK makes no warranty as to the absence of defects, and makes no warranties of any kind, express or implied, including without limitation, implied warranties as to merchantability, fitness for a particular purpose or non-infringement of any third-party's intellectual property rights. Unless otherwise specified in writing, products supplied by 3PEAK are not designed to be used in any life-threatening scenarios, including critical medical applications, automotive safety-critical systems, aviation, aerospace, or any situations where failure could result in bodily harm, loss of life, or significant property damage. 3PEAK disclaims all liability for any such unauthorized use.

www.3peak.com 18 / 18 DA20250901A0