#### **Features**

- Qualified for Automotive Applications

- AEC-Q100 Grade 1, T<sub>A</sub>: -40°C to +125°C

- Wide Input Voltage Range

- 6 V to 52 V, with 65 V Maximum Rating

- High-Side Gate Driver to Control External N-Channel MOSFET

- 2-Stage Charge Pump Integrated

- · Low Standby Current

- ADCs for Current and Voltage Conversion

- Accurate Output Current Sense

- Output Voltage and V<sub>DS</sub> Sense

- External MOSFET Temperature Sense with NTC Resistor

- External MOSFET Protection:

- MOSFET Desaturation Shutdown Configurable via SPI

- Hard Short Circuit Latch-off Configurable via SPI

- Current-vs-Time Latch-off Configurable via SPI

- MOSFET Over-Temperature Protection

- SPI Communication Interface

- 32-bit Compatible with 3.3-V and 5-V CMOS Level

- SPI slave interface for host control

- Register Lock-Out by a Dedicated Pin

- Over-Temperature Protection

- Package Option:

- QFN5X5-32

#### **Applications**

- Automotive Power Distribution Applications

- Automotive Zone Control Unit

- Automotive BMS, Automotive EIC system

#### **Description**

The TPS60C01Q is an eFuse controller with fault detection and protection for implementing of an intelligent high-side power switch for different automotive applications.

The TPS60C01Q supports operating voltage from 6 V to 52 V. This device provides high-side gate drive to control an external n-channel MOSFET with an integrated 2-stage charge pump. Also, this device can deliver 400-mA bypass current through the internal power path.

The TPS60C01Q integrates four ADCs to monitor the current and voltage, including output current through an external MOSFET, output voltage, and VDS voltage of the MOSFET, and external NTC resistor voltage of the MOSFET temperature.

The TPS60C01Q implements an external MOSFET protection function. Including MOSFET desaturation shutdown, hard short circuit latch-off, current-vs-time latch-off, and MOSFET over-temperature protection.

The TPS60C01Q uses a 32-bit SPI interface for register read/write operation, which is compatible with 3.3-V and 5-V CMOS levels.

The TPS60C01Q provides a thermal-enhanced QFN5X5-32 package and is guaranteed to operate within the ambient temperature range from – 40°C to +125°C.

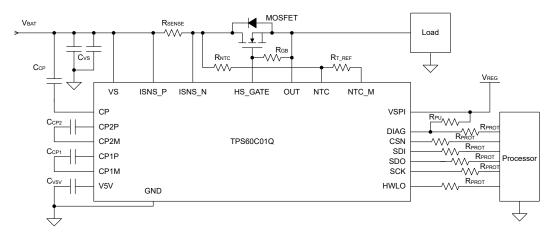

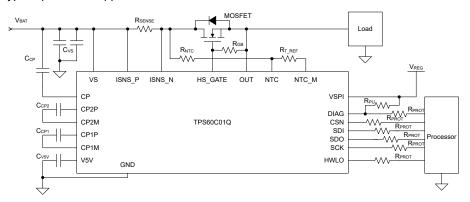

### **Typical Application Circuit**

### **Table of Contents**

| Features                                | 1  |

|-----------------------------------------|----|

| Applications                            | 1  |

| Description                             | 1  |

| Typical Application Circuit             | 1  |

| Product Family Table                    | 3  |

| Revision History                        | 3  |

| Pin Configuration and Functions         | 4  |

| Specifications                          | 6  |

| Absolute Maximum Ratings (1) (2) (3)    | 6  |

| ESD, Electrostatic Discharge Protection | 6  |

| Recommended Operating Conditions        | 7  |

| Thermal Information                     | 7  |

| Electrical Characteristics              | 8  |

| Typical Performance Characteristics     | 15 |

| Register Map                            | 16 |

| Detailed Description                    | 22 |

| Overview                                | 22 |

| Functional Block Diagram                | 22 |

| Feature Description                     | 22 |

| Application and Implementation          | 24 |

| Application Information                 | 24 |

| Typical Application                     | 24 |

| Layout                                  | 25 |

| Layout Guideline                        | 25 |

| Layout Example                          | 25 |

| Tape and Reel Information               | 26 |

| Package Outline Dimensions              | 27 |

| QFN5X5-32-WET                           | 27 |

| Order Information                       | 28 |

| IMPORTANT NOTICE AND DISCLAIMER         | 29 |

# **Product Family Table**

| Order Number     | er Operating Voltage Range (V) Package |           |

|------------------|----------------------------------------|-----------|

| TPS60C01Q-QFZR-S | 6 to 52                                | QFN5X5-32 |

### **Revision History**

| Date       | Revision  | Notes                               |

|------------|-----------|-------------------------------------|

| 2023-12-31 | Rev.Pre.0 | Preliminary datasheet.              |

| 2025-04-03 | Rev.Pre.1 | Updated electrical characteristics. |

| 2025-09-06 | Rev.A.0   | Initial released.                   |

www.3peak.com 3 / 30 DA20241203A0

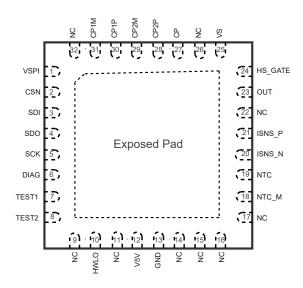

### **Pin Configuration and Functions**

TPS60C01Q QFN5X5-32 Package Top View

Table 1. Pin Functions: TPS60C01Q

| Pin No. | Pin Name | I/O | Description                                                                                                                            |

|---------|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------|

| 27      | СР       | 0   | Charge pump output.                                                                                                                    |

| 31      | CP1M     | 0   | Charge pump–Negative terminal of the flying capacitor CP1.                                                                             |

| 30      | CP1P     | 0   | Charge pump–Positive terminal of the flying capacitor CP1.                                                                             |

| 29      | CP2M     | 0   | Charge pump–Negative terminal of the flying capacitor CP2.                                                                             |

| 28      | CP2P     | 0   | Charge pump–Positive terminal of the flying capacitor CP2.                                                                             |

| 2       | CSN      | I   | Chip select not (active low) for SPI communication. It is the selection pin of the device. CMOS-compatible input.                      |

| 6       | DIAG     | 0   | Open drain logic output. Diagnostic feedback. DIAG = '0' if (SR1.WAKEUPM = '1') or (GSB.DIAGS = '1') or (GSB.DE = '1') else '1'        |

| 13      | GND      | -   | Ground connection.                                                                                                                     |

| 24      | HS_GATE  | 0   | Output of the gate driver for the external FET.                                                                                        |

| 10      | HWLO     | I   | Active high input pin compatible with 3.3 V and 5 V CMOS; it causes transitions to states where the registers are locked from writing. |

| 20      | ISNS_N   | I   | Current sense amplifier negative input.                                                                                                |

| 21      | ISNS_P   | I   | Current sense amplifier positive input.                                                                                                |

www.3peak.com 4 / 30 DA20241203A0

| Pin No.                                 | Pin Name | I/O | Description                                                                                                                    |

|-----------------------------------------|----------|-----|--------------------------------------------------------------------------------------------------------------------------------|

| 9, 11, 14, 15,<br>16, 17, 22, 26,<br>32 | NC       | I   | No internal connection.                                                                                                        |

| 19                                      | NTC      | I   | Positive input pin for external NTC resistor.                                                                                  |

| 18                                      | NTC_M    | I   | Negative input pin for external NTC resistor.                                                                                  |

| 23                                      | OUT      | 0   | External FET source connection.                                                                                                |

| 5                                       | SCK      | 1   | Serial clock for SPI communication. It is a CMOS-compatible input.                                                             |

| 3                                       | SDI      | I   | Serial data input for SPI communication. Data is transferred serially into the device on the SCK rising edge.                  |

| 4                                       | SDO      | 0   | Serial data output for SPI communication. Data is transferred serially out of the device on the SCK falling edge.              |

| 7                                       | TEST1    | -   | Test mode pin 1- must be connected to ground.                                                                                  |

| 8                                       | TEST2    | -   | Test mode pin 2- must be connected to ground.                                                                                  |

| 12                                      | V5V      | 0   | Output of the 5 V internal LDO voltage regulator (logic and I/O supply). Connect a low ESR capacitor (1 µF) close to this pin. |

| 25                                      | VS       | I   | Input supply pin. Connect to the 12 V, 24 V, and 48 V battery voltage.                                                         |

| 1                                       | VSPI     | I   | DC supply input for the SPI interface. 3.3 V and 5 V compatible.                                                               |

<sup>(1)</sup> Thermal Pad MUST be connected to PCB ground plane directly.

www.3peak.com 5 / 30 DA20241203A0

### **Specifications**

#### Absolute Maximum Ratings (1) (2) (3)

|                      | Parameter                           | Min  | Max | Unit |

|----------------------|-------------------------------------|------|-----|------|

| V <sub>VS</sub>      |                                     | -0.3 | 70  | V    |

| V <sub>OUT</sub>     |                                     | -0.3 | 70  | V    |

| V <sub>HS_GATE</sub> |                                     | -0.3 | 90  | V    |

| V <sub>CP</sub>      |                                     | -0.3 | 90  | V    |

| V <sub>CP1P</sub>    |                                     | -0.3 | 90  | V    |

| V <sub>CP2P</sub>    |                                     | -0.3 | 90  | V    |

| V <sub>CP1N</sub>    |                                     | -0.3 | 70  | V    |

| V <sub>CP2N</sub>    |                                     | -0.3 | 70  | V    |

| V <sub>ISNS_P</sub>  |                                     | -0.3 | 70  | V    |

| V <sub>ISNS_N</sub>  |                                     | -0.3 | 70  | V    |

| V <sub>NTC</sub>     |                                     | -0.3 | 70  | V    |

| V <sub>NTC_M</sub>   |                                     | -0.3 | 70  | V    |

| V <sub>VSPI</sub>    |                                     | -0.3 | 6   | V    |

| V <sub>CSN</sub>     |                                     | -0.3 | 6   | V    |

| V <sub>SCK</sub>     |                                     | -0.3 | 6   | V    |

| V <sub>SDI</sub>     |                                     | -0.3 | 6   | V    |

| V <sub>SDO</sub>     |                                     | -0.3 | 6   | V    |

| V <sub>V5V</sub>     |                                     | -0.3 | 6   | V    |

| V <sub>HWLO</sub>    |                                     | -0.3 | 6   | V    |

| V <sub>DIAG</sub>    |                                     | -0.3 | 6   | V    |

| TJ                   | Junction Temperature Range          | -40  | 150 | °C   |

| T <sub>STG</sub>     | Storage Temperature Range           | -65  | 150 | °C   |

| TL                   | Lead Temperature (Soldering 10 sec) |      | 260 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

#### **ESD, Electrostatic Discharge Protection**

| Parameter |                          | Condition              | Minimum Level | Unit |

|-----------|--------------------------|------------------------|---------------|------|

| НВМ       | Human Body Model ESD     | AEC Q100-002           | ±2            | kV   |

| CDM       | Charged Device Model ESD | AEC Q100-011, all pins | ±1            | kV   |

www.3peak.com 6 / 30 DA20241203A0

<sup>(2)</sup> All voltage values are with respect to GND.

<sup>(3)</sup> Not subject to production test, specified by design.

### **Recommended Operating Conditions**

|                   | Parameter                  | Min | Тур | Max | Unit |

|-------------------|----------------------------|-----|-----|-----|------|

| V <sub>VS</sub>   |                            | 6   | 14  | 52  | V    |

| V <sub>VSPI</sub> |                            | 3   |     | 5.5 | V    |

| V <sub>CSN</sub>  |                            | 3   |     | 5.5 | V    |

| V <sub>SCK</sub>  |                            | 3   |     | 5.5 | V    |

| V <sub>SDI</sub>  |                            | 3   |     | 5.5 | V    |

| V <sub>SDO</sub>  |                            | 3   |     | 5.5 | V    |

| V <sub>HWLO</sub> |                            | 0   |     | 5.5 | V    |

| V <sub>DIAG</sub> |                            | 0   |     | 5.5 | V    |

| T <sub>A</sub>    | Ambient Temperature Range  | -40 |     | 125 | °C   |

| TJ                | Junction Temperature Range | -40 |     | 150 | °C   |

#### **Thermal Information**

| Package Type | θ <sub>JA</sub> | θ <sub>ЈВ</sub> | <b>Ө</b> ЈС,ТОР | Unit |

|--------------|-----------------|-----------------|-----------------|------|

| QFN5X5-32    | 25.9            | 4.07            | 15.2            | °C/W |

www.3peak.com 7 / 30 DA20241203A0

#### **Electrical Characteristics**

All test conditions:  $V_S = 6 \text{ V}$  to 52 V,  $T_A = -40 ^{\circ}\text{C}$  to +125  $^{\circ}\text{C}$ . All typical values refer to  $V_S = 14 \text{ V}$ ,  $T_J = 25 ^{\circ}\text{C}$ , unless otherwise noted.

|                       | Parameter                                         | Conditions                                                              | Min | Тур | Max | Unit |

|-----------------------|---------------------------------------------------|-------------------------------------------------------------------------|-----|-----|-----|------|

| Supply Vo             | Itage and Current                                 |                                                                         |     |     |     |      |

| VS                    | Operating Supply Voltage                          |                                                                         | 6   | 14  | 52  | V    |

| VS_UV                 | VS Under-Voltage Lockout                          | VS falling                                                              | 4.5 |     |     | V    |

| VS_UV_H<br>YS         | VS Under-Voltage Lockout<br>Hysteresis            | hysteresis                                                              |     | 100 |     | mV   |

| t <sub>VS_UV</sub>    | VS under-Voltage Lockout<br>Deglitch Time         |                                                                         |     | 33  |     | μs   |

|                       |                                                   | VS = 52 V, OUT = VS                                                     |     |     | 80  | μA   |

|                       | VS Quiescent Current with Logic                   | VS = 52 V, OUT = GND                                                    |     |     | 80  | μA   |

| Ivs_Q                 | Operating                                         | VS = 14 V, OUT = VS                                                     |     |     | 70  | μA   |

|                       |                                                   | VS = 14 V, OUT = GND                                                    |     |     | 70  | μA   |

| ls_ON                 | Supply Current with Logic Operating               | f <sub>PWM</sub> = 1 Hz, Q <sub>G</sub> = 250 nC, VS=<br>48 V, OUT = VS |     | 17  |     | mA   |

|                       | Output Current                                    | VS = 48 V, Stand-by mode, OUT = GND, Bypass switch OFF                  |     |     | 1   | μA   |

|                       |                                                   | VS = 14 V, Stand-by mode, OUT = GND, Bypass switch OFF                  |     |     | 1   | μA   |

| Іоит                  |                                                   | VS = 48 V, Unlocked mode,<br>OUT=GND, Bypass switch OFF                 |     |     | 1   | mA   |

|                       |                                                   | VS = 13 V, Unlocked mode,<br>OUT=GND, Bypass switch OFF                 |     |     | 1   | mA   |

| VS_POR_<br>ON         | Power-On Reset Threshold.                         | Device leaves the Reset mode.                                           |     | 2.5 |     | V    |

| VS_POR_<br>OFF        | Power-on Shutdown Threshold.                      | Device enters Reset mode.                                               |     | 2.3 |     | V    |

| VS_POR_<br>HYS        | Power-on Reset Hysteresis                         |                                                                         |     | 0.2 |     | V    |

| t <sub>PWON</sub>     | Time from Power-on to stand-by                    | VS>VS_POR_ON, V1V8 external capacitor 1 µF                              |     |     | 450 | μs   |

| SPI Power             | Supply (SPI)                                      |                                                                         |     |     |     |      |

| V <sub>SPI</sub>      | SPI Interface Supply Voltage                      |                                                                         | 3   |     | 5.5 | V    |

| I <sub>SPI</sub>      | SPI Interface Supply Current during Communication |                                                                         |     |     | 3   | mA   |

| I <sub>SPI_STBY</sub> | SPI Interface Supply Current in Standby State     | T <sub>A</sub> = 25°C                                                   |     |     | 5   | μA   |

| SPI Logic             | Input (CSN, SCK and SDI)                          |                                                                         |     |     |     |      |

www.3peak.com 8 / 30 DA20241203A0

|               | Parameter                                                                 | Conditions                 | Min  | Тур        | Max  | Unit  |

|---------------|---------------------------------------------------------------------------|----------------------------|------|------------|------|-------|

| VIH           | High-Level Logic Input Voltage                                            |                            | 0.7  |            |      | ×VSPI |

| VIL           | Low-Level Logic Input Voltage                                             |                            |      |            | 0.3  | ×VSPI |

| VI_HYS        | Input Hysteresis Voltage                                                  |                            |      | 0.4        |      | V     |

| VI_CLM        | Input Clamp Voltage (SCK and SDI)                                         |                            |      | VSPI + 0.6 |      | V     |

| ш             | High-Level Logic Input Current (SCK and SDI)                              | VIH = 0.7×VSPI             | 0.5  |            | 5    | μA    |

| IIH           | High-Level Logic Input Current (CSN)                                      | VIH = 0.7×VSPI             | -5   |            | -0.5 | μA    |

| IIL           | Low-Level Logic Input Current (SCK and SDI)                               | VIL = 0.3×VSPI             | 0.5  |            | 5    | μA    |

| IIL           | Low-Level Logic Input Current (CSN)                                       | VIL = 0.3×VSPI             | -5   |            | -0.5 | μA    |

| SPI Logic     | Output (SDO)                                                              |                            |      |            |      |       |

| VOH           | High-Level Logic Output Voltage                                           |                            | 0.8  |            |      | ×VSPI |

| VOL           | Low-Level Logic Output Voltage                                            |                            |      |            | 0.2  | ×VSPI |

| IOL           | Low-Level Logic Output Current                                            |                            | -10  |            | 10   | μA    |

| SPI Timing    | I                                                                         |                            |      |            |      |       |

| fSPI          | SPI Clock Frequency                                                       |                            |      |            | 8    | MHz   |

| tCSN          | CSN Low Timeout                                                           | VSPI = 3.3 V, RPROT < 1 kΩ | 30   |            | 70   | ms    |

|               |                                                                           | WD_TIME Configuration: 00  | -10% | 50         | 10%  | ms    |

| #\A\DTD       | Matabasa Tagala Dit Timasut                                               | WD_TIME Configuration: 01  | -10% | 100        | 10%  | ms    |

| tWDTB         | Watchdog Toggle Bit Timeout.                                              | WD_TIME Configuration: 10  | -10% | 150        | 10%  | ms    |

|               |                                                                           | WD_TIME Configuration: 11  | -10% | 200        | 10%  | ms    |

| tSTBY_O<br>UT | Minimum time during which CSN must be toggled low to go out of STDBY mode |                            | 20   |            | 100  | μs    |

| HWLO Log      | gic Input(HWLO)                                                           |                            |      |            |      |       |

| VIH           | High-Level Logic Input Voltage                                            |                            | 2.1  |            |      | V     |

| VIL           | Low-Level Logic Input Voltage                                             |                            |      |            | 0.9  | V     |

| VI_HYS        | Input Hysteresis Voltage                                                  |                            |      | 0.4        |      | V     |

| IIH           | High-Level Logic Input Current                                            |                            | 0.5  |            | 2.5  | μA    |

| IIL           | Low-Level Logic Input Current                                             |                            | 0.5  |            | 2.5  | μΑ    |

| tHWLO         | HWLO Deglitch Time                                                        |                            |      | 33         |      | μs    |

| DIAG Logi     | c Output (DIAG)                                                           |                            |      |            |      |       |

| VDIAG_P<br>D  | DIAG Pin Low-Level Output<br>Voltage                                      |                            |      |            | 0.2  | V     |

| IDIAG_P<br>D  | DIAG Pin Low-Level Sink Current                                           | VDIAG = VDIAG_PD           |      |            | 1    | mA    |

www.3peak.com 9 / 30 DA20241203A0

|               | Parameter                                                      | Conditions                                                                                                       | Min          | Тур          | Max          | Unit |

|---------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|------|

| IDIAG_LK<br>G | DIAG Pin Leakage Current                                       | VDIAG = VSPI = 5.5 V                                                                                             | 0            |              | 1            | μΑ   |

| Charge Pu     | mp                                                             |                                                                                                                  | 1            | ı            |              |      |

|               |                                                                | VS = 6 V                                                                                                         | VS + 7       | VS + 11      |              | V    |

| VCP           | Charge Pump Output Voltage                                     | VS ≥ 10 V                                                                                                        | VS +<br>13.5 | VS +<br>14.5 | VS +<br>15.5 | V    |

| VCP_H         | Charge Pump Output Under-<br>Voltage High<br>Threshold         | Ramp up on VCP                                                                                                   | VS + 5.6     | VS + 6       | VS + 6.7     | V    |

| VCP_L         | Charge Pump Output Under-<br>Voltage Low<br>Threshold          | Ramp down on VCP                                                                                                 | VS + 5.3     | VS + 5.6     | VS + 6.4     | V    |

| VCP_HY<br>S   | Charge Pump Output Under-<br>Voltage<br>Hysteresis             |                                                                                                                  |              | 0.4          |              | V    |

| fCP           | Charge Pump Frequency                                          |                                                                                                                  | -5%          | 450          | 5%           | kHz  |

| tCP_RISE      | Charge Pump Low (CP_LOW diagnostic) Rising Edge Deglitch Time  |                                                                                                                  | -5%          | 60           | 5%           | μs   |

| tCP_FALL      | Charge Pump Low (CP_LOW diagnostic) Falling Edge Deglitch Time |                                                                                                                  | -10%         | 2.3          | 10%          | μs   |

| External M    | OSFET Gate Driver (HS_GATE)                                    |                                                                                                                  |              |              |              |      |

| VGSON         | Cata ON Valtaga                                                | VS = 6 V, IG = 50 μA                                                                                             | 6            |              |              | V    |

| VGSON         | Gate-ON Voltage                                                | VS ≥ 10 V, IG = 50 μA                                                                                            | 12           |              | 15           | V    |

| VGSOFF        | Gate-OFF Voltage                                               |                                                                                                                  |              |              | 0.5          | V    |

| VGSMAX        | Maximum Gate Voltage (Internal Limited)                        |                                                                                                                  |              |              | 20           | V    |

| tON           | Gate Turn ON Time                                              | VGS = 0.5 V to VGS = 10 V,<br>CGATE = 80 nF                                                                      |              |              | 4            | μs   |

| tOFF          | Gate Turn OFF Time                                             | Full VGS to VGS < 0.5, CGATE = 80 nF                                                                             |              |              | 2.6          | μs   |

| VGS_UVL       | 0.1.11.1.11.1                                                  | VS = 6 V                                                                                                         | 9            |              |              | V    |

| 0             | Gate Under-Voltage Lockout                                     | VS ≥ 10 V                                                                                                        | 9.2          |              |              | V    |

| tGS_UVL<br>O  | Gate Under-Voltage Lockout<br>Blanking Time                    | Enable at Charge Pump startup if Ext FET turn-on is required, and applied after CP_LOW expiration (falling edge) | -6%          | 100          | 6%           | μs   |

|               | Gate Under-Voltage Lockout<br>Deglitch Time                    |                                                                                                                  | -15%         | 8            | 15%          | μs   |

| QG_MAX        | Maximum Gate Charge                                            | VGS = 10 V                                                                                                       |              |              | 800          | nC   |

www.3peak.com 10 / 30 DA20241203A0

|                   | Parameter                                                       | Conditions                                                   | Min  | Тур  | Max  | Unit           |

|-------------------|-----------------------------------------------------------------|--------------------------------------------------------------|------|------|------|----------------|

| External N        | IOSFET VDS Monitor                                              |                                                              |      |      |      |                |

| VDC TII           | VDS Monitor Threshold Range                                     | 31 steps adjustable through SPI                              | 300  |      | 1800 | mV             |

| VDS_TH            | VDS Monitor Threshold Step                                      |                                                              |      | 50   |      | mV             |

| VDS_TH_<br>0      |                                                                 |                                                              |      | 300  |      | mV             |

| VDS_TH_<br>15     |                                                                 |                                                              |      | 1050 |      | mV             |

| VDS_TH_<br>30     |                                                                 |                                                              |      | 1800 |      | mV             |

| VDS_AD<br>C_FS    | Full Scale Range Resolution of VDS Monitor ADC                  | VDS_ADC_FS[9:0] =<br>MIN((VSENSE_N - VOUT)/2 *<br>1024, 957) | 0    |      | 957  |                |

| VDS_AD<br>C_SR    | Sample Rate of VDS Monitor<br>ADC                               |                                                              |      | 0.9  |      | Msampl<br>e/s  |

| VDS_TH_<br>ACC    | VDS Monitor Threshold Accuracy                                  |                                                              | -5%  |      | 5%   |                |

| tDS_DEG           | VDS Monitor Shut-Off Deglitch<br>Time                           |                                                              | -25% | 5    | 25%  | μs             |

| tDS_DLY           | VDS Monitor Shut-Off Delay Time                                 |                                                              |      |      | 5    | μs             |

| tDS_BLK           | VDS Monitor Shut-Off Blanking<br>Time                           | At High Side External FET startup                            | -10% | 960  | 10%  | μs             |

| Current Se        | ense Amplifier with Integrated AD                               | C (ISNS_P and ISNS_N)                                        |      |      |      |                |

| VISNS_C<br>M      | Current Sense Common-Mode<br>Input Voltage<br>Range             |                                                              | 0    |      | 70   | V              |

| VISNS_F<br>S      | Full Scale Range of Current<br>Sense Differential Input Voltage |                                                              | 0    |      | 160  | mV             |

| IISNS_P           | ISNS_P Pin Input Current                                        |                                                              |      | 40   |      | μA             |

| IISNS_N           | ISNS_N Pin Input Current                                        |                                                              |      | 270  |      | μA             |

| VISNS_A<br>DC_RES | Full Scale Range Resolution of Current Sense ADC                | VISNS_ADC_FS[12:0] =<br>MIN((VSENSE/160×8192), 8191)         | 0    |      | 8191 |                |

| VISNS_A<br>DC_SR  | Sample Rate of Current Sense<br>ADC                             |                                                              |      | 2.4  |      | kSample<br>s/s |

|                   |                                                                 | 1.8 mV < ΔVISNS < 6 mV                                       | -17% |      | 17%  |                |

| VISNS_A           | Current Sense Accuracy                                          | 6 mV < ΔVISNS < 10 mV                                        | -10% |      | 10%  |                |

| CC                | Odifford Accuracy                                               | ΔVISNS = 10 mV                                               | -5%  |      | 5%   |                |

|                   |                                                                 | ΔVISNS > 20 mV                                               | -3%  |      | 3%   |                |

| Output Sh         | ort Circuit Protection                                          |                                                              |      |      | I    |                |

| VSC_TH            | Output Short Circuit Protection Threshold Range                 | 16 steps adjustable through SPI                              | 20   |      | 160  | mV             |

www.3peak.com 11 / 30 DA20241203A0

|                | Parameter                                           | Conditions                                        | Min               | Тур             | Max                  | Unit          |

|----------------|-----------------------------------------------------|---------------------------------------------------|-------------------|-----------------|----------------------|---------------|

| VSC_TH_<br>0   |                                                     |                                                   |                   | 20              |                      | mV            |

| VSC_TH_<br>8   |                                                     |                                                   |                   | 60.6            |                      | mV            |

| VSC_TH_<br>16  |                                                     |                                                   |                   | 160             |                      | mV            |

| VSC_AD<br>C_FS | Full Scale Range of Short Circuit<br>Protection ADC | VSC_ADC_FS[9:0] =<br>MIN((VSENSE/160*1024), 1023) | 0                 |                 | 1023                 |               |

| VSC_AD<br>C_SR | Sample Rate of Short Circuit<br>Protection ADC      |                                                   |                   | 0.9             |                      | Msampl<br>e/s |

| VSC_AC<br>C    | Output Short Circuit Protection Threshold Accuracy  |                                                   | -5%               |                 | 5%                   |               |

| tSC_DLY        | Output Short Circuit Protection Delay Time          |                                                   |                   |                 | 5                    | μs            |

| Output Ov      | er Current Protection                               |                                                   |                   |                 |                      |               |

| VOC_TH         | Output Over Current Protection Threshold Range      | 32 steps adjustable through SPI                   | 6                 |                 | 90                   | mV            |

| VOC_TH_<br>0   |                                                     |                                                   | -12%              | 6               | 12%                  | mV            |

| VOC_TH_<br>2   |                                                     |                                                   | -12%              | 8.7             | 12%                  | mV            |

| VOC_TH_<br>3   |                                                     |                                                   | -7%               | 10.4            | 7%                   | mV            |

| VOC_TH_<br>12  |                                                     |                                                   | -7%               | 20.4            | 7%                   | mV            |

| VOC_TH_<br>13  |                                                     |                                                   | -5%               | 21.8            | 5%                   | mV            |

| VOC_TH_<br>31  |                                                     |                                                   | -5%               | 89.3            | 5%                   | mV            |

| tl-t           | I-t tolerance on time step (y axis)                 |                                                   | (t - 10%)<br>- 32 |                 | (t +<br>10%) +<br>32 | μs            |

| tSAMPLI<br>NG  | Shunt Current Sampling Time                         |                                                   | -10%              | 61              | 10%                  | μs            |

| External M     | OSFET Thermal Protection via N                      | TC Input (NTC and NTC_M)                          |                   |                 |                      |               |

| VNTC           | NTC Input Voltage Range                             |                                                   | VISNS_<br>N-1.2   |                 | VISNS_               | V             |

| VNTC_M         | NTC_M Output Voltage                                |                                                   |                   | VISNS_<br>N-1.2 |                      | V             |

www.3peak.com 12 / 30 DA20241203A0

|                 | Parameter                                                            | Conditions                                                         | Min | Тур    | Max  | Unit           |

|-----------------|----------------------------------------------------------------------|--------------------------------------------------------------------|-----|--------|------|----------------|

| VNTC_A          | NTC Input Voltage Threshold                                          |                                                                    | -3  |        | 3    | mV             |

| CC              | Accuracy                                                             |                                                                    |     |        |      | 1117           |

| VNTC_TH         |                                                                      |                                                                    |     | 110.92 |      | mV             |

| _0              |                                                                      |                                                                    |     |        |      |                |

| VNTC_TH         |                                                                      |                                                                    |     | 98.76  |      | mV             |

| _1              |                                                                      |                                                                    |     |        |      |                |

| VNTC_TH<br>_2   |                                                                      |                                                                    |     | 88.07  |      | mV             |

| VNTC_TH         |                                                                      |                                                                    |     |        |      |                |

| _3              |                                                                      |                                                                    |     | 78.66  |      | mV             |

| VNTC_TH         |                                                                      |                                                                    |     | 70.38  |      | mV             |

| _4              |                                                                      |                                                                    |     | 70.30  |      | IIIV           |

| VNTC_TH         |                                                                      |                                                                    |     | 63.08  |      | mV             |

| _5              |                                                                      |                                                                    |     |        |      |                |

| VNTC_TH<br>_6   |                                                                      |                                                                    |     | 56.64  |      | mV             |

| VNTC_TH         |                                                                      |                                                                    |     |        |      |                |

| _7              | External FET Thermal Protection                                      |                                                                    |     | 50.95  |      | mV             |

|                 | NTC Input Voltage Threshold                                          |                                                                    |     | 45.00  |      | .,,            |

| _8              |                                                                      |                                                                    |     | 45.92  |      | mV             |

| VNTC_TH         |                                                                      |                                                                    |     | 41.46  |      | mV             |

| _9              |                                                                      |                                                                    |     | 11.10  |      | 1114           |

| VNTC_TH         |                                                                      |                                                                    |     | 37.5   |      | mV             |

| _10             |                                                                      |                                                                    |     |        |      |                |

| VNTC_TH<br>_11  |                                                                      |                                                                    |     | 37.5   |      | mV             |

| VNTC_TH         |                                                                      |                                                                    |     | 27.5   |      |                |

| _12             |                                                                      |                                                                    |     | 37.5   |      | mV             |

| VNTC_TH         |                                                                      |                                                                    |     |        | 37.5 |                |

| _13             |                                                                      |                                                                    |     |        | 07.0 |                |

| VNTC_TH<br>_14  |                                                                      |                                                                    |     | 37.5   |      | mV             |

| VNTC_TH         |                                                                      |                                                                    |     | 0= -   |      |                |

| _15             |                                                                      |                                                                    |     | 37.5   |      | mV             |

| VNTC_A<br>DC_FS | Full Scale Range of External<br>MOSFET Thermal Protection<br>NTC ADC | VNTC_ADC_FS[9:0] =<br>MIN(((VSENSE_N - VNTC)/1.2 *<br>1024), 1023) | 0   |        | 1023 |                |

| VNTC_A<br>DC_SR | Sample Rate of External MOSFET Thermal Protection NTC ADC            |                                                                    |     | 4.9    |      | kSample<br>s/s |

| VNTC_D<br>EG    | External MOSFET Thermal Protection Deglitch Time                     |                                                                    | 10  |        | 500  | μs             |

www.3peak.com 13 / 30 DA20241203A0

|                 | Parameter                                                     | Conditions                                          | Min | Тур | Max                              | Unit           |

|-----------------|---------------------------------------------------------------|-----------------------------------------------------|-----|-----|----------------------------------|----------------|

| Internal By     | pass Switch                                                   |                                                     |     |     |                                  |                |

| VBP_SAT         | Internal Bypass Switch VDS<br>Saturation Protection Threshold |                                                     | 1   |     | 2.5                              | <b>\</b>       |

| IBP_SAT         | Internal Bypass Switch Saturation Current                     | VS - VOUT =<br>VDS_BYPASS_SAT                       | 300 |     |                                  | mA             |

| RBP_ON          | Internal Bypass Switch Turn-ON<br>Resistance                  |                                                     | 1   | 3   | 5.2                              | Ω              |

| tBP_ON          | Internal Bypass Switch Turn-ON<br>Time                        |                                                     |     |     | 100(VS><br>8V)<br>125(VS=<br>6V) | μs             |

| tBP_SAT_<br>DEG | Internal Bypass Switch Saturation Diagnostic Deglitch Time    |                                                     | 2.9 |     | 5.5                              | μs             |

| VOUT Mor        | nitor                                                         |                                                     |     |     | _                                |                |

| VOUT_A<br>DC_FS | Full-Scale Range of Output<br>Voltage Monitor ADC             | VOUT_ADC_FS[9:0] =<br>MIN(VOUT/(51*1.2)*1024, 1023) | 0   |     | 1023                             |                |

| VOUT_A<br>DC_SR | VOUT ADC Sample Rate                                          |                                                     |     | 4.9 |                                  | kSample<br>s/s |

| Internal Th     | nermal Protection                                             |                                                     |     |     |                                  |                |

| T0D             | Internal Thermal Shutdown Threshold                           |                                                     | 160 | 175 |                                  | ů              |

| TSD             | Internal Thermal Shutdown<br>Hysteresis                       |                                                     |     | 15  |                                  | °C             |

| TINT_AD<br>C_FS | Full Scale Range of Internal<br>Junction Temperature ADC      | TINT_ADC_FS[9:0] = (TJ + 72) *<br>3                 | 0   |     | 1023                             |                |

| TINT_AD<br>C_SR | Sample Rate of Internal Junction<br>Temperature ADC           |                                                     |     | 10  |                                  | kSample<br>s/s |

<sup>(1)</sup> Not subject to production test, specified by design.

www.3peak.com 14 / 30 DA20241203A0

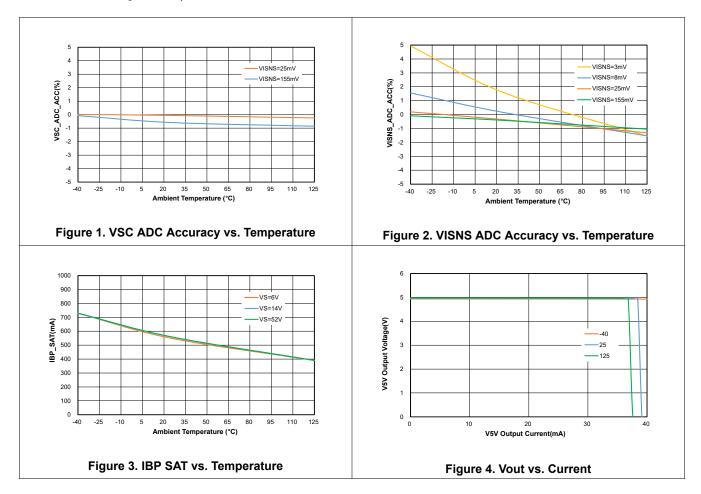

#### **Typical Performance Characteristics**

All test conditions:  $V_S = 13.5 \text{ V}$ , unless otherwise noted.

www.3peak.com 15 / 30 DA20241203A0

### **Register Map**

| Address | Reg Name | Reg<br>Description | Width | Field   | Field Name | Access Right | Field Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------|----------|--------------------|-------|---------|------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01h     | CR1      |                    | 32    | [31:13] | (reserved) | RO           | reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         |          |                    |       | [12]    | PWM_ON     | RW_E         | enable PWM for capacitive charge mode, active high                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         |          | Control Register   |       | [11]    | GOSTBY     | RW_E         | GOSTBY can be set to 1 only if UNLOCK = 1; trying to set this bit to 1 when UNLOCK = 0 will have no effects and it will maintain its previous value.  GOSTBY can be reset to 0 also when UNLOCK = 0.  To send a GOToStandby sequence it is necessary to send two consecutive SPI frames, as follows:  1st SPI write operation to set UNLOCK bit to 1  2nd SPI write operation to set GOSTBY bit to 1 and EN bit to 0.  A transition to Standby state causes GOSTBY to be reset to 0. |

|         |          |                    |       | [10]    | EN         | RW_E         | EN can be set to 1 only if UNLOCK = 1; trying to set this bit to 1 when UNLOCK = 0 will have no effects and it will maintain its previous value.  EN can be reset to 0 also when UNLOCK = 0.  To send a GOToUnlocked sequence it is necessary to send two consecutive SPI frames as follows:  1st SPI write operation to set UNLOCK bit to 1  2nd SPI write operation to set GOSTBY bit to 0 and EN bit to 1.                                                                        |

www.3peak.com 16 / 30 DA20241203A0

| Address | Reg Name | Reg<br>Description | Width | Field | Field Name | Access Right | Field Description                                                                                                                                                                                                                                                                           |

|---------|----------|--------------------|-------|-------|------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |          |                    |       |       |            |              | A transition to Unlocked state causes EN to be set to 1. A transition to Locked state causes EN to be reset to 0.                                                                                                                                                                           |

|         |          |                    |       | [9]   | S_T_START  | RW_E         | When it is set to 1, starts selected self-test.  If current state is Unlocked and S_T_CFG is not 000, then setting this bit causes a transition to Self-Test state.  This bit is automatically reset.                                                                                       |

|         |          |                    |       | [8]   | S_T_STOP   | RW_E         | When it is set to 1, stops execution of selected self-test. This bit is automatically reset.                                                                                                                                                                                                |

|         |          |                    |       | [7:5] | S_T_CFG    | RW_E         | Self Test selection: 000: No selection 001: Current sense 010: VDS detection 100: Power switch stuck-on 011: Current sense + VDS detection 101: Current sense + Power switch stuck-on 110: VDS detection + Power switch stuck-on 111: Current sense + VDS detection + Power switch stuck-on |

|         |          |                    |       | [4]   | OUTCTL     | RW_E         | Enables High Side through SPI  1: HS Gate driver commanded on  0: HS Gate driver commanded off                                                                                                                                                                                              |

|         |          |                    |       | [3]   | BYPASSCTL  | RW_E         | Enables Low Current Bypass through SPI                                                                                                                                                                                                                                                      |

www.3peak.com 17 / 30 DA20241203A0

| Address | Reg Name | Reg<br>Description | Width | Field   | Field Name | Access Right | Field Description                                                                                                                                                                                                                                                                                                                 |

|---------|----------|--------------------|-------|---------|------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |          |                    |       |         |            |              | 1: LCB commanded on 0: LCB commanded off                                                                                                                                                                                                                                                                                          |

|         |          |                    |       | [2]     | (reserved) | RO           | reserved                                                                                                                                                                                                                                                                                                                          |

|         |          |                    |       | [1]     | WD_TRIG    | RW_E         | Mirror of WD_TRIG bit                                                                                                                                                                                                                                                                                                             |

|         |          |                    |       | [0]     | (reserved) | RO           | reserved                                                                                                                                                                                                                                                                                                                          |

| 02h     | CR2      |                    | 32    | [31:24] | (reserved) | RO           | reserved                                                                                                                                                                                                                                                                                                                          |

|         |          | Control Register   |       | [23:16] | T_NOM      | RW_E         | Configures the value of Nominal Time, required for the fuse emulation: tNOM (s) = b{T_NOM(7:0), 1} T_NOMmin = 000000000 → tNOM (s) = b000000001 = 1s T_NOMmax = 111111111 → tNOM (s) = b111111111 = 511s Nominal Time corresponds to the trip time obtained when current is equal to the Nominal Overcurrent Threshold (OVC_THR). |

|         |          |                    |       | [15:11] | OVC_THR    | RW_E         | Configures the value of Nominal Overcurrent Threshold. The threshold can be set in the range 6 mV to 90 mV See Table 16                                                                                                                                                                                                           |

|         |          |                    |       | [10:7]  | HSHT_THR   | RW_E         | Configures a threshold for Hard Short Circuit Latchoff. The threshold can be set in the range from 20 mV to 160 mV. See Table 15                                                                                                                                                                                                  |

www.3peak.com 18 / 30 DA20241203A0

| Address | Reg Name | Reg<br>Description | Width | Field   | Field Name            | Access Right | Field Description                                                                                                                                                                                    |

|---------|----------|--------------------|-------|---------|-----------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |          |                    |       | [6:2]   | VDS_THR               | RW_E         | Configures a threshold for External MOSFET desaturation shut-down. The threshold can be set in the range from 0.3 V to 1.80 V in steps of 50 mV (default = 300 mV).  Configuration 0x1F is reserved. |

|         |          |                    |       | [1]     | WD_TRIG               | RW_E         | Mirror of WD_TRIG bit                                                                                                                                                                                |

|         |          |                    |       | [0]     | (reserved)            | RO           | reserved                                                                                                                                                                                             |

| 03h     | CR3      |                    | 32    | [31:21] | (reserved)            | RO           | reserved                                                                                                                                                                                             |

|         |          |                    |       | [20]    | ntc_warning_en        | RW_E         | 0: when ntc > ntc_thr, protection active 1; when ntc > ntc_thr, only warning by DIAG and sr register, not trig protection                                                                            |

|         |          |                    |       | [19]    | pwm_auto_stop_<br>en  | RW_E         | enable pwm auto stop                                                                                                                                                                                 |

|         |          | Control Register   |       | [18:13] | pwm_auto_stop_<br>thr | RW_E         | when VOUT[9:4]>pwm_auto_stop_thr[5:0], pwm finish, hgate keep on. Threshold: 51*1.2*{pwm_auto_stop_thr[5:0], 4'b0}/ 1024                                                                             |

|         |          |                    |       | [12:10] | hsht_blk              | RW_E         | hard short blanking:<br>0: 0 μs<br>1: 50 μs<br>2: 100 μs<br>3: 200 μs<br>4: 500 μs<br>5: 1 ms<br>6: 1.5 ms                                                                                           |

www.3peak.com 19 / 30 DA20241203A0

| Address | Reg Name | Reg<br>Description | Width | Field   | Field Name       | Access Right | Field Description                                                                                                                                                                                                   |

|---------|----------|--------------------|-------|---------|------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |          |                    |       |         |                  |              | 7: 2 ms                                                                                                                                                                                                             |

|         |          |                    |       | [9]     | UNLOCK           | RW_E         | 0: bits GOSTBY, EN cannot be set to 1 but can be reset; 1: bits GOSTBY, EN can be set to 1, but only with the next valid SPI frame.  When UNLOCK = 1, it will be automatically reset with the next valid SPI frame. |

|         |          |                    |       | [8:5]   | NTC_THR          | RW_E         | Configures a threshold for External MOSFET over-<br>temperature shutdown via NTC. The<br>threshold can be set in the range 37.50 to 110.92.<br>See Table 17                                                         |

|         |          |                    |       | [4:3]   | WD_TIME          | RW_E         | Watchdog time selection: 00: tWD = 50ms 01: tWD = 100ms 10: tWD = 150ms 11: tWD = 200ms                                                                                                                             |

|         |          |                    |       | [2]     | DIS_OUT_MOD<br>E | RW_E         | Outputs status in Locked state: 0: leave output and bypass as they are (default) 1: shut off output and bypass                                                                                                      |

|         |          |                    |       | [1]     | WD_TRIG          | RW_E         | In order to keep device in Unlocked Mode, this bit must be cyclically toggled within a period equal to tWD to refresh the watchdog.                                                                                 |

|         |          |                    |       | [0]     | (reserved)       | RO           | reserved                                                                                                                                                                                                            |

| 04h     | CR4      | Control Register 4 | 32    | [31:20] | (reserved)       | RO           | reserved                                                                                                                                                                                                            |

www.3peak.com 20 / 30 DA20241203A0

| Address | Reg Name | Reg<br>Description | Width | Field   | Field Name  | Access Right | Field Description                                                                                                                           |

|---------|----------|--------------------|-------|---------|-------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------|

|         |          |                    |       | [19:18] | PWM_HSHT_BL | RW_E         | 00: vds no pwm blanking 01: vds pwm stage 1 blanking 1x: vds pwm stage 1 and 2 blanking (default)                                           |

|         |          |                    |       | [17:10] | PWM_C2_TON  | RW_E         | PWM charge stage 2 Ton setting: range: 0us~255us, one step 1us 0x0 configuration: high side driver controlled by protection only            |

|         |          |                    |       | [9:2]   | PWM_C1_TON  | RW_E         | PWM charge stage 1 Ton setting:<br>range: 0 μs~255 μs, one step 1us<br>0x0 configuration: high side driver controlled by<br>protection only |

|         |          |                    |       | [1]     | WD_TRIG     | RW_E         | In order to keep device in Unlocked Mode, this bit must be cyclically toggled within a period equal to tWD to refresh the watchdog.         |

www.3peak.com 21 / 30 DA20241203A0

#### **Detailed Description**

#### Overview

The TPS60C01Q is an eFuse controller with fault detection and protection for the implementation of an intelligent high-side power switch for different automotive applications.

The TPS60C01Q supports operating voltage from 6 V to 52 V. This device provides high-side gate drive to control an external n-channel MOSFET with an integrated 2-stage charge pump. Also, this device can deliver 400-mA bypass current through the internal power path.

The TPS60C01Q integrates four ADCs to monitor the current and voltage, including output current through external MOSFET, output voltage and VDS voltage of the MOSFET, and external NTC resistor voltage of the MOSFET temperature.

The TPS60C01Q implements an external MOSFET protection function. Including MOSFET desaturation shutdown, hard short circuit latch-off, current-vs-time latch-off, and MOSFET over-temperature protection.

The TPS60C01Q uses a 32-bit SPI interface for register read/write operation, which is compatible with 3.3-V and 5-V CMOS levels.

The TPS60C01Q provides a thermal-enhanced QFN5X5-32 package and is guaranteed to operate within the ambient temperature range from  $-40^{\circ}$ C to  $+125^{\circ}$ C.

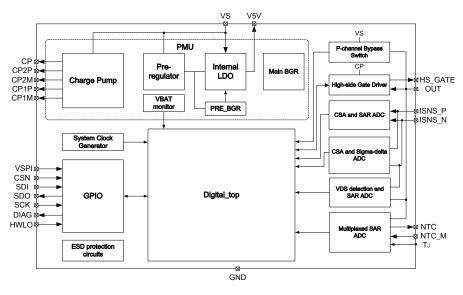

#### **Functional Block Diagram**

Figure 5. Functional Block Diagram

#### **Feature Description**

#### TPS60C01Q overview

Protection of wire harnesses and PCBs can be achieved by defining an ideal time-to-fuse curve based on the maximum power dissipation over time in the wires or copper PCB traces. This approach ensures that the insulation of wires and PCB substrates remains within a limited temperature and time budget, staying below reliability-specified thresholds. Exceeding these limits may lead to carbonization of organic insulation materials, forming conductive paths that can create local hot spots, sparking, and potentially fire ignition.

www.3peak.com 22 / 30 DA20241203A0

The VNF1048F incorporates ST's proprietary eFuse functionality, which provides a robust and flexible overcurrent protection mechanism. This intelligent circuit-breaking feature is designed to protect PCB traces, connectors, and wire harnesses from overheating, without affecting load transients such as inrush currents and capacitor charging.

The eFuse function is configured using two parameters: INOM and tNOM. INOM represents the maximum continuous current allowed, while tNOM determines the current versus time-to-fuse curve when the load current exceeds INOM. The relationship between current and time-to-fuse is approximated by an optimized stepwise function, adjustable within a range bounded by the wire I²t limit on one end and load transient characteristics on the other. The tNOM value corresponds to the first step-up point of this curve. This current-time curve operates in conjunction with a very fast overcurrent protection mechanism, which triggers immediately when the current reaches a predefined threshold under hard short-circuit conditions.

When the load current is pulse-width modulated (PWM), the eFuse function calculates the root mean square (RMS) value of the current. RMS current measurement also occurs during power switching under normal operation, or after a shutdown due to short-circuit or overload conditions. For example, if the circuit is interrupted due to an overload and subsequently reactivated, the eFuse retains memory of the previous condition and continues to ensure that the maximum IRMS does not exceed INOM.

www.3peak.com 23 / 30 DA20241203A0

### **Application and Implementation**

#### Note

Information in the following application sections is not part of the 3PEAK's component specification and 3PEAK does not warrant its accuracy or completeness. 3PEAK's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### **Application Information**

The TPS60C01Q is an eFuse controller with fault detection and protection for the implementation of an intelligent high-side power switch for different automotive applications.

#### **Typical Application**

Figure 6 shows the typical protection application schematic of the TPS60C01Q.

Figure 6. Typical Application Circuit

www.3peak.com 24 / 30 DA20241203A0

#### Layout

#### **Layout Guideline**

To get good thermal performance and prevent over-temperature protection, the PCB layout is important. A well-designed PCB layout can effectively optimize heat dissipation, which is crucial for ensuring the long-term reliability of the device.

- It is recommended to maximize the coverage of copper on the PCB to enhance the thermal conductivity of the board.

Since the primary heat flow path from the package to the surrounding environment passes through the copper on the PCB, having maximum copper coverage is particularly important when there is no heat sink attached to the opposite side of the board.

- It is recommended to place as many thermal vias as possible underneath the package ground pad to optimize the thermal conductivity of the board.

- It is suggested that all thermal vias be either plated shut or plugged and capped on both sides of the board to prevent solder voids to maintain reliability and performance.

- It is recommended to use wide traces or thick copper weight in the input/output current paths to minimize I×R voltage drop.

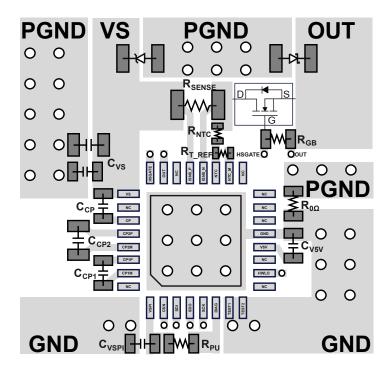

#### **Layout Example**

Figure 7. Layout Example

www.3peak.com 25 / 30 DA20241203A0

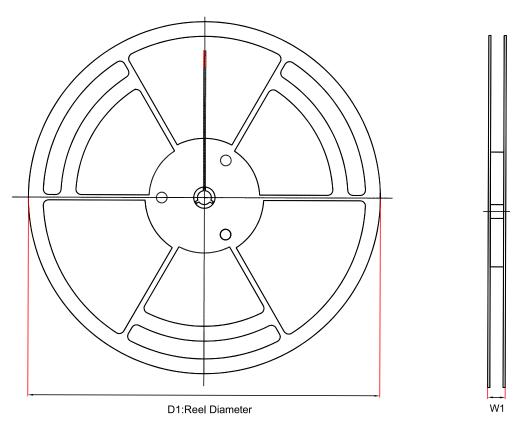

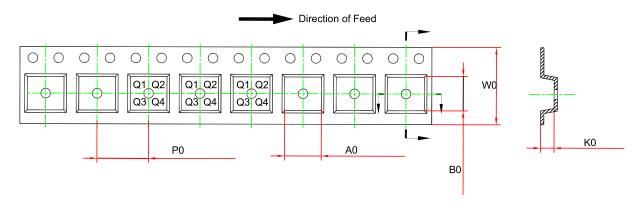

### **Tape and Reel Information**

| Order Number     | Package   | D1<br>(mm) | W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | W0<br>(mm) | Pin1<br>Quadran<br>t |

|------------------|-----------|------------|------------|------------|------------|------------|------------|------------|----------------------|

| TPS60C01Q-QFZR-S | QFN5X5-32 | 330        | 17.6       | 5.3        | 5.3        | 1.1        | 8          | 12         | Q2                   |

www.3peak.com 26 / 30 DA20241203A0

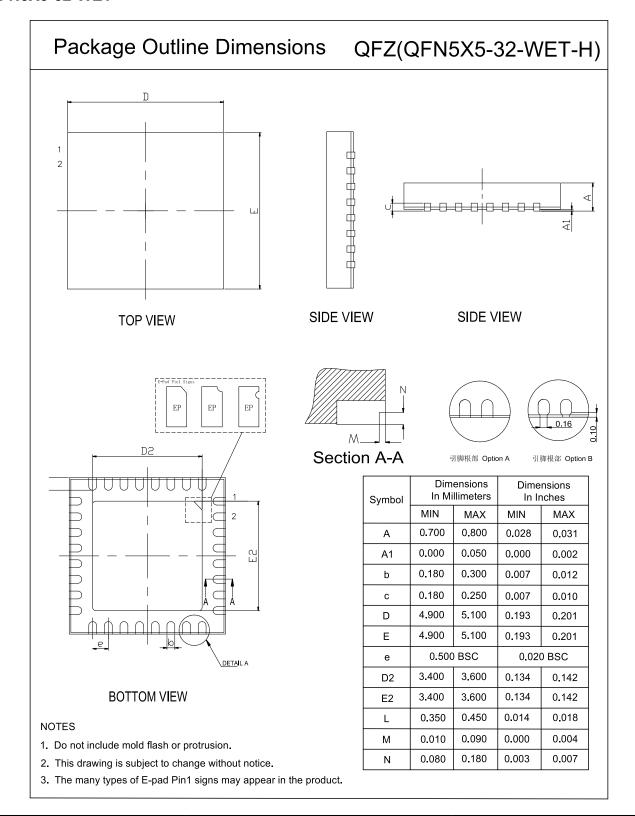

### **Package Outline Dimensions**

#### QFN5X5-32-WET

#### **Order Information**

| Order Number     | Operating Temperature Range | Package   | Marking Information | MSL  | Transport Media, Quantity | Eco Plan |

|------------------|-----------------------------|-----------|---------------------|------|---------------------------|----------|

| TPS60C01Q-QFZR-S | −40 to 125°C                | QFN5X5-32 | 60C01               | MSL3 | 3,000                     | Green    |

**Green**: 3PEAK defines "Green" to mean RoHS compatible and free of halogen substances.

www.3peak.com 28 / 30 DA20241203A0

#### IMPORTANT NOTICE AND DISCLAIMER

Copyright<sup>©</sup> 3PEAK 2012-2025. All rights reserved.

**Trademarks.** Any of the 思瑞浦 or 3PEAK trade names, trademarks, graphic marks, and domain names contained in this document /material are the property of 3PEAK. You may NOT reproduce, modify, publish, transmit or distribute any Trademark without the prior written consent of 3PEAK.

**Performance Information.** Performance tests or performance range contained in this document/material are either results of design simulation or actual tests conducted under designated testing environment. Any variation in testing environment or simulation environment, including but not limited to testing method, testing process or testing temperature, may affect actual performance of the product.

**Disclaimer.** 3PEAK provides technical and reliability data (including data sheets), design resources (including reference designs), application or other design recommendations, networking tools, security information and other resources "As Is". 3PEAK makes no warranty as to the absence of defects, and makes no warranties of any kind, express or implied, including without limitation, implied warranties as to merchantability, fitness for a particular purpose or non-infringement of any third-party's intellectual property rights. Unless otherwise specified in writing, products supplied by 3PEAK are not designed to be used in any life-threatening scenarios, including critical medical applications, automotive safety-critical systems, aviation, aerospace, or any situations where failure could result in bodily harm, loss of life, or significant property damage. 3PEAK disclaims all liability for any such unauthorized use.

www.3peak.com 29 / 30 DA20241203A0

This page intentionally left blank

www.3peak.com 30 / 30 DA20241203A0