### **Features**

- 3-V to 16-V Input Voltage Range with Internal VCC Bias

- 2.7-V to 16-V Input Voltage Range with External VCC Bias from 3 V to 5 V

- · Adjustable and Accurate Current Limit Level

- Adjustable Switching Frequency with Fixed Frequency Function: 600 kHz, 800 kHz, 1 MHz

- · Stable with Zero ESR Output Capacitor

- Selectable Power-Save Mode or Forced-PWM Mode

- Adjustable Soft Start from 1 ms and Smoothly Pre-bias Power up

- 0.6-V ±0.5% Reference Voltage Accuracy from 0°C to +85°C

- 0.6-V ±1% Reference Voltage Accuracy from −40°C to +125°C

- Integrated Output Track and Discharge Function

- Non-latch for OCP, UVP, UVLO, OTP, Latch-off for OVP

- Available in the QFN3X4-21 Package

### **Applications**

- Server

- Telecom and Communication Equipment

- · Switch and Access Point

- Industrial PC

### **Description**

The TPP21206 is a high-efficiency, easy-to-use, fully integrated synchronous step-down regulator with 2.7-V to 16-V wide input voltage range and 12-A continuous output current capability. One internal LDO is integrated for a compact single-input power supply. A wide range of external VCC bias from 3 V to 5 V can replace the internal LDO to further enhance the efficiency of the system.

The TPP21206 adopts fast transient response, constant-on-time control with fixed frequency function over different duty cycle and load current range. Differential remote sense feedback with 1% accuracy reference voltage over the full operating temperature range ensures excellent output accuracy and regulation. The high-integrated compensation provides a stable control loop with zero ESR output capacitors, supporting flexible component selection and easy-control stability.

The device features adjustable and accurate current limits for both high-side, low-side positive, and low-side negative current limit to ensure safety. The open-drain PWRGD with active clamped output can enhance the supply reliability during system malfunction. The device has built-in protection and diagnostic features such as cycle-by-cycle current limit, under-voltage protection, over-voltage protection, UVLO, and over-temperature protection.

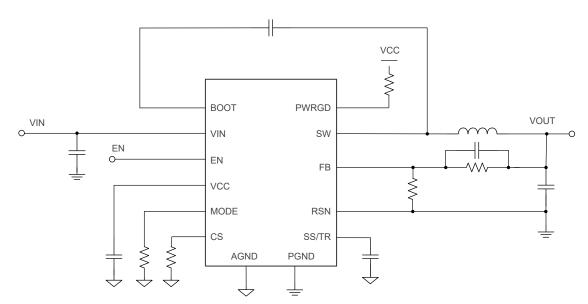

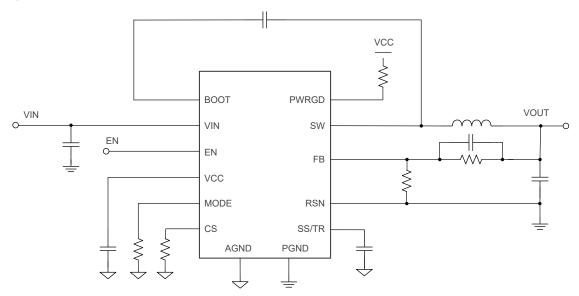

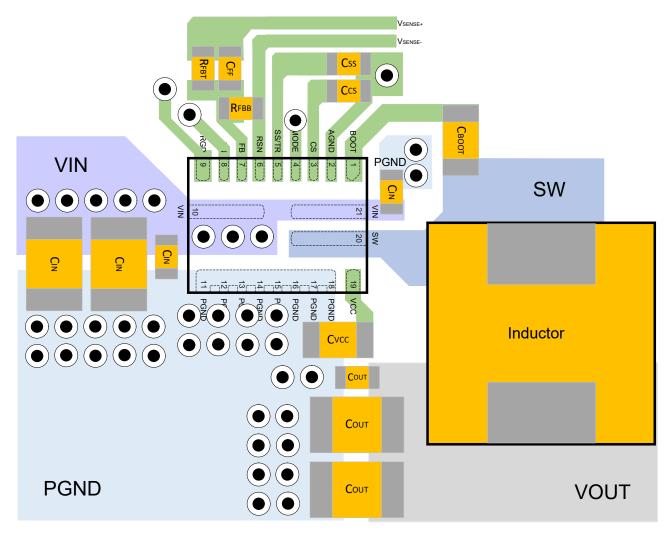

### **Typical Application Circuit**

### **Table of Contents**

| Features                                |    |

|-----------------------------------------|----|

| Applications                            |    |

| Description                             |    |

| Typical Application Circuit             | 1  |

| Product Family Table                    | 3  |

| Revision History                        | 3  |

| Pin Configuration and Functions         | 4  |

| Specifications                          | 6  |

| Absolute Maximum Ratings <sup>(1)</sup> | 6  |

| ESD, Electrostatic Discharge Protection | 6  |

| Recommended Operating Conditions        | 6  |

| Thermal Information                     | 7  |

| Electrical Characteristics              |    |

| Typical Performance Characteristics     | 11 |

| Detailed Description                    | 13 |

| Overview                                | 13 |

| Functional Block Diagram                | 13 |

| Feature Description                     | 14 |

| Protection                              | 17 |

| Application and Implementation          | 20 |

| Application Information                 | 20 |

| Application Waveforms                   | 23 |

| Layout                                  | 29 |

| Layout Guideline                        | 29 |

| Layout Recommendations                  |    |

| Tape and Reel Information               |    |

| Package Outline Dimensions              |    |

| QFN3X4-21                               |    |

| Order Information                       |    |

| IMPORTANT NOTICE AND DISCLAIMER         | 34 |

### **Product Family Table**

| Order Number   | Package   |

|----------------|-----------|

| TPP212060-FC5R | QFN3X4-21 |

### **Revision History**

| Date       | Revision | Notes            |

|------------|----------|------------------|

| 2025-06-15 | Rev.A.0  | Initial release. |

www.3peak.com 3 / 34 EA20250502A0

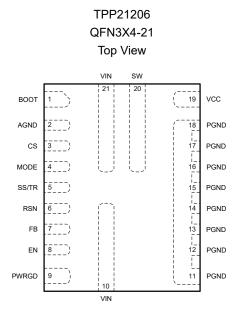

### **Pin Configuration and Functions**

Table 1. Pin Functions: TPP21206

| Pin No. | Name  | I/O | Description                                                                                                                                                                                                                                                                                 |

|---------|-------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | воот  | 0   | High-side MOSFET gate supply pin. Recommend connecting a 0.1-µF ceramic capacitor between BOOT and SW pins.                                                                                                                                                                                 |

| 2       | AGND  | G   | Analog ground pin. The reference point for control circuits. Connect to the analog ground plane at the point of the ground of the VCC capacitor.                                                                                                                                            |

| 3       | CS    | I/O | Current limit setting pin. Connect a resistor to the AGND pin to set the valley current limit value.                                                                                                                                                                                        |

| 4       | MODE  | I   | Operation mode setting pin. Connect a resistor between the MODE pin and the AGND pin to select FPWM/PSM operation and switching frequency.                                                                                                                                                  |

| 5       | SS/TR | I/O | Soft start and tracking input pin. When using the soft start function, connect an external capacitor to this pin to set the output start-up time; When using the tracking function, the external DC voltage on this pin overrides the internal voltage reference to set the output voltage. |

| 6       | RSN   | I   | Differential remote-sensing ground pin. Connect this pin directly to the negative side of the remote voltage sense point. Short to AGND if the remote sense is not used.                                                                                                                    |

| 7       | FB    | I   | Voltage feedback pin. Connect the output voltage and the RSN pin with a feedback resistor divider to set the output value.                                                                                                                                                                  |

| 8       | EN    | I   | Enable the input pin. An input signal to turn the regulator on or off. Connect this pin to the VIN pin with a pull-up resistor or a resistor divider. Do not leave the EN pin floating.                                                                                                     |

www.3peak.com 4 / 34 EA20250502A0

| Pin No. | Name  | I/O | Description                                                                                                                                                                                                                                |

|---------|-------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9       | PWRGD | 0   | Power-good indicator pin. An open-drain output which is actively clamped low if the output voltage is outside the normal regulation range. Connect a pull-up resistor to one system voltage rail.                                          |

| 10, 21  | VIN   | Р   | Input voltage supply pin. Input capacitors should be placed as close to this pin and the PGND pin as possible.                                                                                                                             |

| 11-18   | PGND  | G   | Power ground pin. The reference ground of the internal power stage. Use the connection with wide PCB traces.                                                                                                                               |

| 19      | VCC   | I/O | Internal LDO pin. The power supply for the driver and control circuits. Connect a ceramic bypass capacitor from this pin to the AGND pin. An external VCC supply can be connected to overdrive the internal LDO to enhance the efficiency. |

| 20      | SW    | 0   | Switching output pin. Connect this pin to the external inductor.                                                                                                                                                                           |

www.3peak.com 5 / 34 EA20250502A0

### **Specifications**

### Absolute Maximum Ratings (1)

|      | Parameter                                          | Min  | Max | Unit |

|------|----------------------------------------------------|------|-----|------|

| VIN  | Supply Voltage                                     | -0.3 | 18  | V    |

| CVA  | Switching Node Voltage                             | -0.3 | 18  | V    |

| SW   | Switching Node Voltage (less than 25 ns transient) | -5   | 25  | V    |

| воот | Bootstrap to SW Voltage                            | -0.3 | 6   | V    |

| VCC  | Internal Supply Voltage                            | -0.3 | 6   | V    |

|      | All Other Pins                                     | -0.3 | 6   | V    |

| RSN  | Remote Sense Voltage                               | -0.3 | 0.3 | V    |

| TJ   | Junction Temperature Range                         | -40  | 150 | °C   |

| Ts   | Storage Temperature Range                          | -55  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

### **ESD, Electrostatic Discharge Protection**

| Parameter |                          | Condition                  | Minimum Level | Unit |

|-----------|--------------------------|----------------------------|---------------|------|

| НВМ       | Human Body Model ESD     | ANSI/ESDA/JEDEC JS-001 (1) | ±2000         | V    |

| CDM       | Charged Device Model ESD | ANSI/ESDA/JEDEC JS-002 (2) | ±500          | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### **Recommended Operating Conditions**

|      | Parameter                                                       | Min   | Max       | Unit |

|------|-----------------------------------------------------------------|-------|-----------|------|

| VIN  | Input Voltage Range When VCC Pin is Powered by External Bias    | 2.7   | 16        | V    |

| VIN  | Input Voltage Range When VCC Pin is Powered by Internal VCC LDO | 3.0   | 16        | V    |

|      | Switching Node Voltage                                          | - 0.3 | VIN + 0.3 | V    |

| SW   | Switching Node Voltage (less than 25 ns transient)              | - 5   | VIN + 0.3 | V    |

| VOUT | Output Voltage Range                                            | 0.6   | 5.5       | V    |

| VCC  | External VCC Bias                                               | 3.12  | 5         | V    |

| IOUT | Maximum Output Current                                          |       | 12        | Α    |

| TJ   | Junction Temperature Range                                      | - 40  | 125       | °C   |

www.3peak.com 6 / 34 EA20250502A0

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **Thermal Information**

| Package Type | θυΑ   | <b>Ө</b> ЈВ | <b>Ө</b> лс | Unit |

|--------------|-------|-------------|-------------|------|

| QFN3X4-21    | 56.37 | 18.42       | 25.41       | °C/W |

www.3peak.com 7 / 34 EA20250502A0

### **Electrical Characteristics**

Unless otherwise noted, the min and max limits apply over the recommended operating ambient temperature range ( $T_A$ ) of -40°C to 125°C. Typical values are measured under  $T_A$  = 25°C and represent the most likely parameters normally for reference. The default test conditions:  $V_{IN}$  = 12 V, internal VCC LDO.

|                       | Parameter                                 | Conditions                                                                       | Min  | Тур  | Max  | Unit |

|-----------------------|-------------------------------------------|----------------------------------------------------------------------------------|------|------|------|------|

| Input Sup             | oly                                       |                                                                                  |      |      |      |      |

| $I_{Q\_VIN}$          | VIN Quiescent Current                     | $V_{IN}$ = 12 V, $V_{EN}$ = 2 V, non-<br>switching, no external bias on<br>VCC   |      | 730  |      | μA   |

| I <sub>SD_VIN</sub>   | VIN Shut Down Current                     | V <sub>IN</sub> = 12 V, V <sub>EN</sub> = 0 V, no<br>external bias on VCC        |      | 1    | 15   | μA   |

| I <sub>Q_VCC</sub>    | VCC Quiescent Current                     | $V_{IN}$ = 12 V, $V_{EN}$ = 2 V, non-<br>switching, external bias 3.3V on<br>VCC |      | 660  |      | μА   |

| I <sub>SD_VCC</sub>   | VCC Shut Down Current                     | V <sub>IN</sub> = 12 V, V <sub>EN</sub> = 0 V, external bias 3.3 V on VCC        |      | 40   | 60   | μА   |

| VIN <sub>UVLO_R</sub> | VIN UVLO Rising Threshold                 | VIN Rising, external bias 3.3 V on VCC                                           | 2.1  | 2.55 | 2.7  | V    |

| VIN <sub>UVLO_F</sub> | VIN UVLO Falling Threshold                | VIN Falling, external bias 3.3V on VCC                                           | 1.55 | 1.9  | 2.15 | V    |

| Enable                |                                           |                                                                                  |      |      |      |      |

| V <sub>EN_R</sub>     | Enable Voltage Rising Threshold           | Enable rising                                                                    | 1.15 | 1.20 | 1.25 | V    |

| V <sub>EN_F</sub>     | Enable Voltage Falling Threshold          | Enable falling                                                                   | 0.95 | 1.00 | 1.05 | V    |

| I <sub>EN</sub>       | Enable Input Leakage Current              | V <sub>EN</sub> = 2 V                                                            |      | 0    |      | μA   |

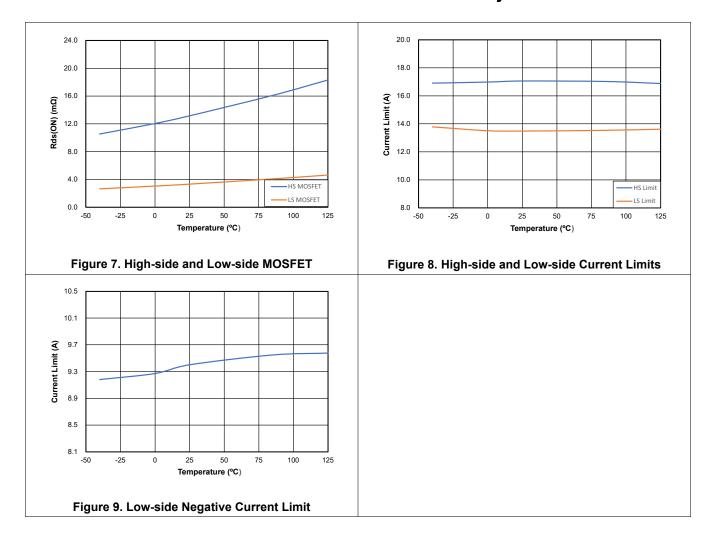

| MOSFET                |                                           |                                                                                  |      |      |      |      |

| R <sub>DSON_HS</sub>  | High-side MOSFET on-resistance            | V <sub>EN</sub> = 2 V, T <sub>A</sub> = 25°C                                     |      | 14   |      | mΩ   |

| R <sub>DSON_LS</sub>  | Low-side MOSFET on-resistance             | V <sub>EN</sub> = 2 V, T <sub>A</sub> = 25°C                                     |      | 4    |      | mΩ   |

| Current Li            | mit                                       |                                                                                  |      |      |      |      |

| $V_{LIMIT}$           | Current Limit Reference                   |                                                                                  |      | 0.3  |      | V    |

| G <sub>OCP_LS</sub>   | I <sub>CS</sub> to I <sub>OUT</sub> Ratio | I <sub>OUT</sub> > 2 A                                                           |      | 5    |      | μA/A |

| I <sub>LIMIT_LS</sub> | Low-side Current Limit                    |                                                                                  | 12   | 14   | 16   | Α    |

| I <sub>LIMIT_HS</sub> | High-side Current Limit                   |                                                                                  | 14.5 | 16.5 | 18.5 | Α    |

| I <sub>NG</sub>       | Low-side Negative Current Limit           |                                                                                  |      | -9.5 |      | Α    |

| I <sub>ZC</sub>       | Zero-cross Detection Current<br>Threshold | V <sub>IN</sub> = 12 V with internal LDO                                         |      | 200  |      | mA   |

| BOOT Sup              | pply                                      |                                                                                  |      |      |      |      |

| VBOOT <sub>UV</sub>   | Bootstrap UVLO Falling<br>Threshold       | $T_A = 25$ °C, $V_{IN} = 12$ V, $V_{BOOT-SW}$ falling                            |      | 2.1  |      | V    |

| VCC Regu              | lator                                     |                                                                                  |      |      |      |      |

www.3peak.com 8 / 34 EA20250502A0

|                       | Parameter                              | Conditions                                                                 | Min  | Тур  | Max  | Unit |

|-----------------------|----------------------------------------|----------------------------------------------------------------------------|------|------|------|------|

| VCC                   | Internal LDO Output                    | V <sub>IN</sub> = 12 V, I <sub>LOAD_VCC</sub> = 2 mA                       |      | 3.1  |      | V    |

| VCC <sub>UVLO</sub> _ | Internal VCC UVLO Rising Threshold     | VCC rising                                                                 | 2.8  | 2.87 | 2.94 | V    |

| VCC <sub>UVLO</sub> _ | Internal VCC UVLO Falling Threshold    | VCC falling                                                                | 2.62 | 2.7  | 2.77 | V    |

| I <sub>VCC_LIM</sub>  | VCC LDO Short Circuit Current<br>Limit |                                                                            |      | 90   |      | mA   |

| Voltage Re            | eference                               |                                                                            |      |      |      |      |

| V                     | Internal Valtage Deference Dange       | T <sub>A</sub> = 0°C to 85°C                                               | 597  | 600  | 603  | mV   |

| V <sub>REF</sub>      | Internal Voltage Reference Range       | $T_A = -40^{\circ}C$ to 125°C                                              | 594  | 600  | 606  | mV   |

| I <sub>FB</sub>       | Feedback Input Leakage Current         | V <sub>FB</sub> = V <sub>REF</sub>                                         |      | 1    |      | nA   |

| Vos_ea                | EA Amplifier Offset                    |                                                                            |      | 0    |      | mV   |

| Switching             | Frequency                              |                                                                            |      |      |      |      |

|                       |                                        |                                                                            | 540  | 600  | 700  | kHz  |

| fsw                   | Switching Frequency, FPWM Operation    |                                                                            | 720  | 800  | 880  | kHz  |

|                       | Орегация                               |                                                                            | 850  | 1000 | 1100 | kHz  |

| T <sub>ON_MIN</sub>   | Minimum on-time                        |                                                                            |      | 60   |      | ns   |

| T <sub>OFF_MIN</sub>  | Minimum off-time                       |                                                                            |      | 180  |      | ns   |

| Soft Start            | and Tracking (SS/TR)                   |                                                                            |      |      |      |      |

| T <sub>SS</sub>       | Internal Fixed Soft Start Time         | Output rising from 0 V to 95% of final setpoint, C <sub>SS/TR</sub> = 1 nF |      | 1    | 1.5  | ms   |

| Isource               | SS/TR Sourcing Current                 | V <sub>SS/TR</sub> = 0 V                                                   |      | 42   |      | μA   |

| I <sub>SINK</sub>     | SS/TR Sinking Current                  | V <sub>SS/TR</sub> = 1 V                                                   |      | 12   |      | μA   |

| Voltage Pr            | otection                               |                                                                            |      |      |      |      |

| Vovp                  | Over-Voltage Protection Threshold      |                                                                            | 113% | 116% | 119% |      |

| V <sub>UVP</sub>      | Under-Voltage Protection Threshold     |                                                                            | 77%  | 80%  | 83%  |      |

| Power Go              | od                                     |                                                                            |      |      |      |      |

|                       |                                        | FB rising, PWRGD Low to High                                               | 89%  | 92%  | 95%  |      |

| V <sub>PG_TH</sub>    | PWRGD Threshold                        | FB rising, PWRGD High to Low                                               | 113% | 116% | 119% |      |

|                       |                                        | FB falling, PWRGD High to Low                                              | 77%  | 80%  | 83%  |      |

| V <sub>PG_OLP</sub>   | Output Limitation Protection Threshold | FB rising, PWRGD Stays High                                                | 103% | 106% | 109% |      |

| V <sub>PG_LOW</sub>   | PWRGD Low-level Output<br>Voltage      | I <sub>PWRGD</sub> = 10 mA, V <sub>IN</sub> = 12 V, internal VCC           |      |      | 150  | mV   |

| T <sub>PG_DLYR</sub>  | Delay for PWRGD from Low to<br>High    |                                                                            |      | 1    |      | ms   |

www.3peak.com 9 / 34 EA20250502A0

|                        | Parameter                                                 | Conditions                                                                                                        | Min | Тур | Max  | Unit |

|------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| T <sub>PG_DLYF</sub>   | Delay for PWRGD from High to Low                          |                                                                                                                   |     | 0.5 |      | μs   |

| I <sub>PG_LKG</sub>    | PWRGD Leakage Current                                     | T <sub>A</sub> = 25°C, V <sub>PWRGD</sub> = 3.3 V                                                                 |     |     | 5    | μΑ   |

|                        | PWRGD Clamp Low Output<br>Voltage @ V <sub>IN</sub> =12 V | VCC = 0 V, $V_{EN}$ = 0 V, PWRGD pulled up to 3.3 V through one 100 k $\Omega$ resistor                           |     | 0   | 5    | mV   |

| V <sub>PG_CLAMP_</sub> | PWRGD Clamp Low Output<br>Voltage @ V <sub>IN</sub> =0 V  | VCC = 0 V, $V_{EN}$ = 0 V, PWRGD pulled up to 3.3 V through one 100 k $\Omega$ resistor                           |     | 710 | 850  | mV   |

|                        |                                                           | VCC = 0 V, $V_{EN}$ = 0 V, PWRGD pulled up to 3.3 V through one 10 kΩ resistor                                    |     | 850 | 1000 | mV   |

| VCC <sub>MIN_PG</sub>  | Minimum VCC for Valid PWRGD Output                        | $V_{IN}$ = 0 V, $V_{EN}$ = 0 V, PWRGD<br>pulled up to 3.3 V through One<br>100 kΩ resistor, $V_{PWRGD} \le 0.4$ V |     |     | 1.3  | V    |

| Output Dis             | charge                                                    |                                                                                                                   |     |     |      |      |

| R <sub>ON_DIS</sub>    | Output Discharge Resistance                               |                                                                                                                   |     | 95  |      | Ω    |

| Thermal S              | hutdown                                                   |                                                                                                                   |     |     |      |      |

| T <sub>SD</sub>        | Thermal Shutdown Threshold                                | Rising temperature                                                                                                | ·   | 160 |      | °C   |

| T <sub>HYS</sub>       | Thermal Shutdown Hysteresis                               |                                                                                                                   |     | 30  |      | °C   |

www.3peak.com 10 / 34 EA20250502A0

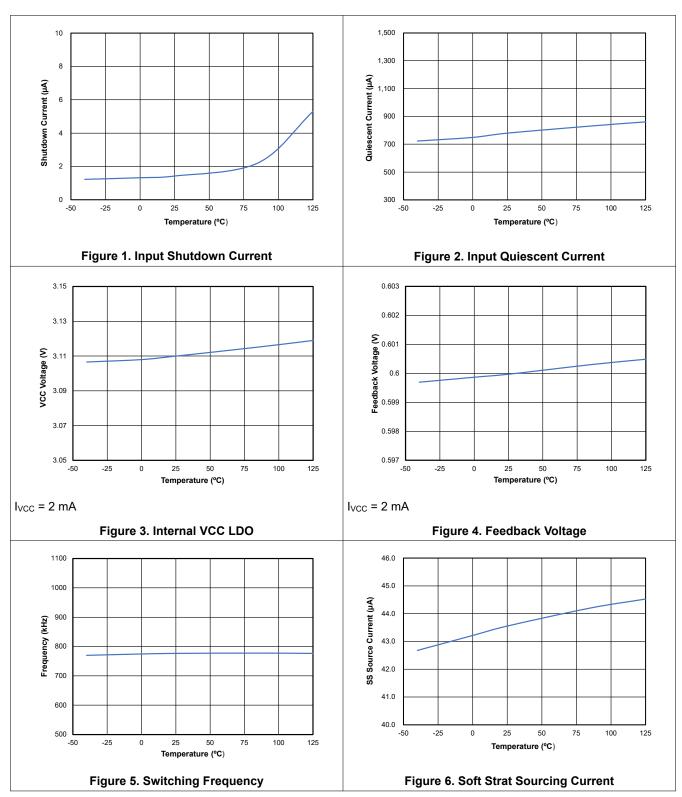

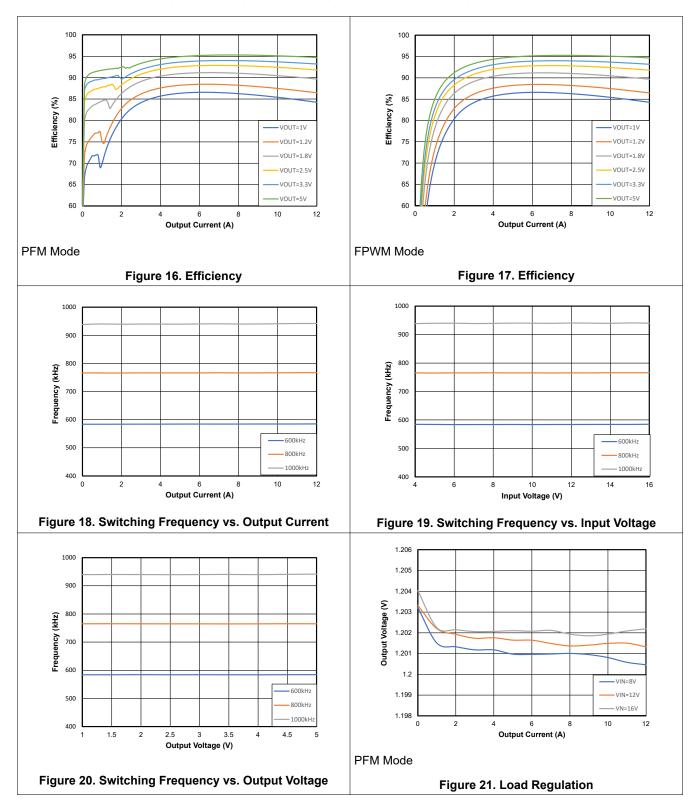

### **Typical Performance Characteristics**

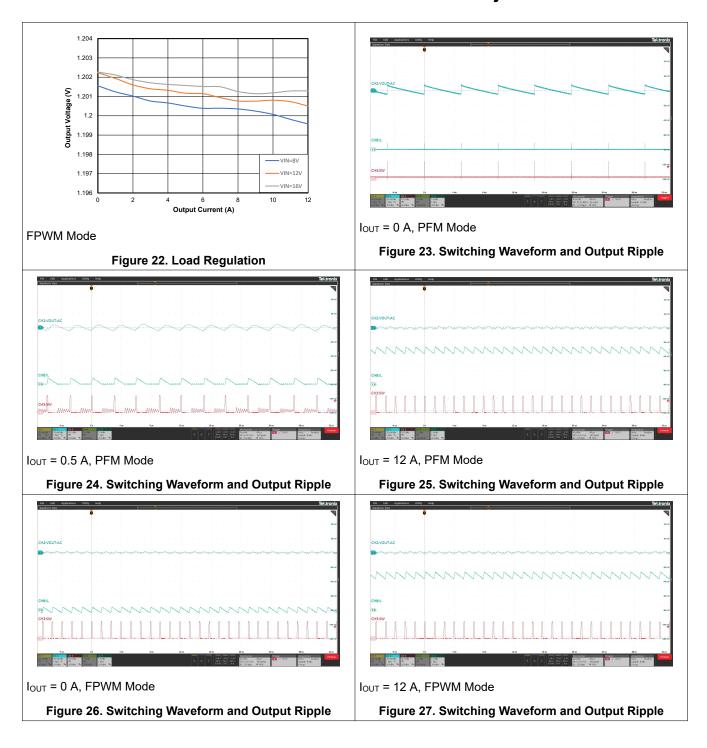

All test conditions: V<sub>IN</sub> = 12 V, V<sub>OUT</sub> = 1.2 V, F<sub>SW</sub> = 800 kHz, FPWM Mode, T<sub>A</sub> = 25 °C, unless otherwise noted.

www.3peak.com 11 / 34 EA20250502A0

www.3peak.com 12 / 34 EA20250502A0

### **Detailed Description**

#### Overview

The TPP21206 is a high-efficiency, easy-to-use, fully integrated synchronous step-down regulator with 2.7-V to 16-V wide input voltage range and 12-A continuous output current capability. One internal LDO is integrated for a compact single-input power supply. A wide range of external VCC bias from 3 V to 5 V can replace the internal LDO to further enhance the efficiency of the system.

The TPP21206 adopts fast transient response, constant-on-time control with fixed frequency function over different duty cycles and load current ranges. Differential remote sense feedback with 1% accuracy reference voltage over the full operating temperature range ensures excellent output accuracy and regulation. The high-integrated compensation provides a stable control loop with zero ESR output capacitors, supporting flexible component selection and easy-control stability.

The device features adjustable and accurate current limits for both high-side, low-side positive, and low-side negative current limit to ensure safety. The open-drain PWRGD with active clamped output can enhance the supply reliability during system malfunction. The device has built-in protection and diagnostic features such as cycle-by-cycle current limit, under-voltage protection, over-voltage protection, UVLO, and over-temperature protection.

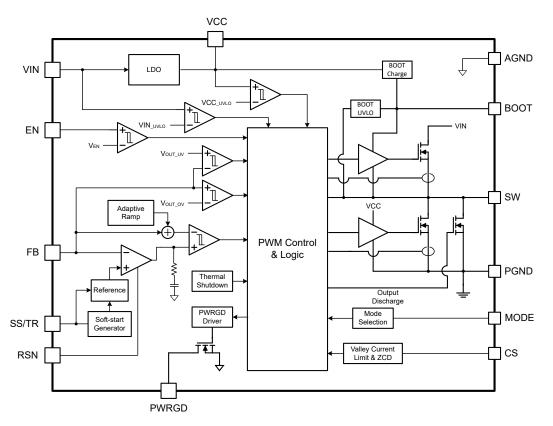

#### **Functional Block Diagram**

Figure 10. Functional Block Diagram

www.3peak.com 13 / 34 EA20250502A0

#### **Feature Description**

#### **Constant-on-time Control with Fixed Frequency Loop**

The TPP21206 adopts constant-on-time control to achieve the fast load transient performance and the easy use of external components. An error amplifier is integrated to provide the accurate output voltage and excellent load regulation over the whole load range. The feedback voltage is sensed from the resistor divider through the FB pin to compare with the internal voltage reference. The device also integrates an internal ripple compensation to support low-ESR output capacitors such as MLCC. The adaptive internal ramp is optimized to ensure the device is stable in the whole operating voltage range with proper design of the external components.

The output of the error amplifier is superimposed onto the internal ripple compensation and directly compared with the feedback voltage. When the feedback voltage drops below the superimposed signal, the high-side MOSFET turns on for a fixed on-time determined by the one-shot generator. The fixed on-time is mainly determined by the input voltage, output voltage, and selected switching frequency. When the fixed high-side on-time elapses, the low-side MOSFET turns on after the dead time until the feedback voltage drops below the superimposed signal again. The device regulates the output voltage stable by operating in this way.

For constant-on-time control, the on-time generated by the one-shot generator typically has deviation from the accurate on-time value, especially in different duty cycle and load current conditions. In the small duty cycle conditions, the actual switching frequency deviates from the setting frequency largely. When the load current is large, the efficiency loss also leads to the switching frequency deviation. One fixed frequency loop is integrated in the constant-on-time architecture of the TPP21206 to maintain the switching frequency fairly constant under different application conditions.

#### **Mode Selection**

The TPP21206 provides FPWM mode to optimize the output ripple and PSM mode to improve the light load efficiency. In FPWM mode, the device operates in continuous conduction mode (CCM) during light-load conditions. During CCM operation, the switching frequency is almost constant over the entire load range. In PSM mode, the inductor current also decreases when the load decreases until the inductor current reaches zero. The low-side MOSFET turns off when the zero-inductor current is detected. As the load current decreases further, the device runs into discontinuous conduction mode (DCM). During DCM operation, the on-time is maintained similar to that during CCM operation.

The TPP21206 also has three options for switching frequency selection: 600 kHz, 800 kHz, and 1000 kHz. The operation mode and switching frequency are selected by connecting a resistor from the MODE pin to the AGND pin. One ±1% tolerance resistor is recommended, and the resistor values are listed in the table below.

| Mode                   | Light Load Operation | Switching Frequency |  |  |

|------------------------|----------------------|---------------------|--|--|

| VCC                    | PSM                  | 600 kHz             |  |  |

| 243 kΩ (±10%) to AGND  | PSM                  | 800 kHz             |  |  |

| 121 kΩ (±10%) to AGND  | PSM                  | 1000 kHz            |  |  |

| AGND                   | FPWM                 | 600 kHz             |  |  |

| 30.1 kΩ (±10%) to AGND | FPWM                 | 800 kHz             |  |  |

| 60.4 kΩ (±10%) to AGND | FPWM                 | 1000 kHz            |  |  |

#### VCC LDO and External Bias Function

The TPP21206 integrates an internal VCC LDO powering input from VIN and output to VCC. The VCC LDO provides the power supply for the driver and control circuits. An external bias which is above the output of the internal VCC LDO can override the internal LDO. This function can enhance the efficiency of the system because the internal driver and control circuits are now powered from the external bias instead of the internal VCC LDO.

www.3peak.com 14 / 34 EA20250502A0

The VCC pin needs to be decoupled with a minimum 1-µF ceramic capacitor as close to VCC as possible. The VCC UVLO circuit monitors the VCC voltage and disables the internal circuits when the VCC voltage falls below the VCC UVLO threshold. Maintaining a stable and clean VCC voltage to provide a smooth operation of the device.

#### **Enable Control and Power-on Sequence**

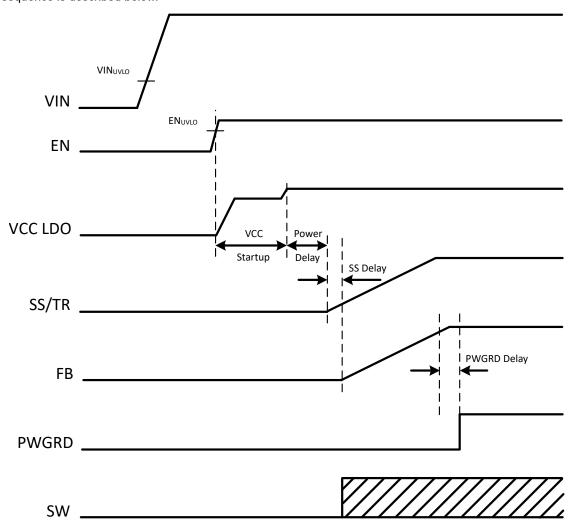

When the enable voltage rises above the enable threshold and the input voltage rises above the UVLO rising threshold, the TPP21206 enters its internal power-on sequence. When using the applications of such default internal VCC LDO, the internal power-on sequence is described below.

Figure 11. Power-on Sequence with Internal VCC LDO

- 1. The input supply rises above the UVLO threshold and the enable control rises above the enable threshold.

- 2. The internal VCC voltage is charged up on the bypass capacitor. If the input supply ramps up very slowly, the VCC voltage is limited by the input voltage level, and the VCC start-up time can be extended longer.

- 3. When the VCC voltage rises above the VCC UVLO threshold, the soft start ramp starts, and the device begins to switch after the power-on delay.

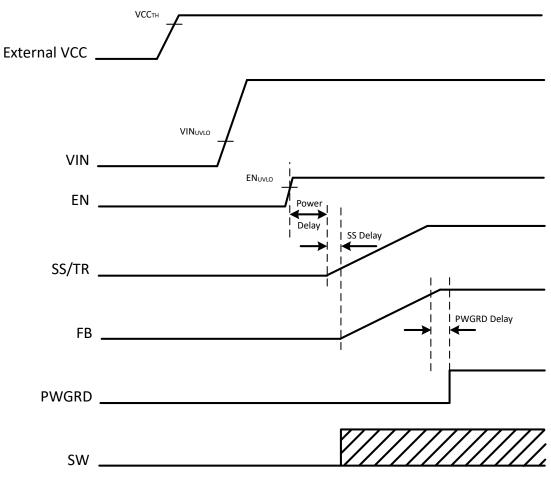

When using the applications of the external bias on the VCC pin, the internal power-on sequence is described below.

www.3peak.com 15 / 34 EA20250502A0

Figure 12. Power-on Sequence with External Bias

- 1. The external VCC voltage is built up already and rises above the VCC UVLO threshold.

- 2. The input supply rises above the UVLO threshold, and the enable control rises above the enable threshold.

- 3. The soft start ramp starts and the device begins to switch after the power-on delay.

#### **Soft Start**

The TPP21206 integrates a soft start function to control the inrush current during start-up. The device supports both internal fixed soft start and external adjustable soft start. The internal soft start time is typically 1 ms which is also the minimum soft start time. It can be increased by adding a capacitor C<sub>SS</sub> between the SS/TR pin and ground.

The soft start time T<sub>SS</sub> is determined by the following equation.

$$T_{SS}(ms) = \frac{C_{SS}(nF) \times 0.6 \text{ (V)}}{I_{SOURCE}(\mu A)}$$

(1)

#### **Differential Output Remote Sense**

The TPP21206 supports differential output remote sense function through the FB and RSN pins. The RSN pin helps sense the remote ground voltage, cooperating with the remote output sense. This function compensates for the potential voltage drop on the PCB traces and maintains the output voltage accuracy under steady state and load transient operation. The connection of the remote sense trace should be kept in low impedance and implement Kelvin sensing to achieve the best performance. To maintain a stable output voltage and minimize the output ripple, the pair of remote sensing traces should

www.3peak.com 16 / 34 EA20250502A0

stay away from any noise sources such as inductor, and SW nodes, or high-frequency clock traces. It is recommended to shield the pair of remote sensing traces with ground planes.

#### Pre-bias Start up

The TPP21206 also supports a monotonic start-up with pre-biased loads. If the output voltage is pre-biased to a certain value during start-up, the device disables switching for both high-side and low-side power switches until the soft-start reference voltage exceeds the feedback voltage.

#### **Output Discharge**

When the device is disabled through EN or triggers the protections, such as UVLO or thermal shutdown, it enables the output discharge function. This function forces both high-side and low-side MOSFETs to latch off but turns on the discharge MOSFET. The MOSFET is connected between the SW and ground to directly discharge the output voltage.

#### **Power Good**

The device employs an open-drain output PWRGD signal to check whether the output voltage is operating within the normal range. The external pull-up voltage resource is recommended to be less than 5.5 V (such as VCC) with a 1-kΩ resistor. After the feedback voltage reaches 92% of the reference voltage, PWRGD is pulled high after a short time. Once the feedback voltage is lower than 80% or greater than 116% of the internal reference voltage, the PWRGD is pulled low. The TPP21206 still has the ability to pull the PWRGD pin low when the input supply is provided while the enable voltage is low.

#### **Protection**

#### **Undervoltage Lockout (UVLO)**

The device monitors the voltage on both the VIN and the VCC pins. Both VIN and VCC UVLO protections are non-latching protections. When the VCC pin voltage drops below the UVLO falling threshold, the device shuts down. When the VCC pin voltage increases above the UVLO rising threshold, the device turns on.

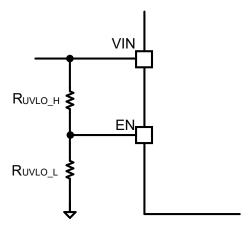

When the VIN pin voltage drops below the UVLO falling threshold but the VCC pin voltage remains higher than the UVLO rising threshold, the device stops switching and shuts down. Once the VIN pin voltage increases above the UVLO rising threshold, the device turns back on and switches again. It can be adjusted by using the EN pin with an external resistor divider

Vuvlo R is the desired system-level undervoltage protection rising threshold voltage, and Vuvlo F is the desired system-level undervoltage protection falling threshold voltage. VEN R and VEN F are rising and falling enable thresholds. RUVLO H and Ruvlo L can be calculated below.

$$V_{UVLO_R} = \left(1 + \frac{R_{UVLO_H}}{R_{UVLO_L}}\right) \times V_{EN_R}$$

$$V_{UVLO_F} = \left(1 + \frac{R_{UVLO_H}}{R_{UVLO_L}}\right) \times V_{EN_F}$$

(2)

$$V_{UVLO\_F} = \left(1 + \frac{R_{UVLO\_H}}{R_{UVLO\_L}}\right) \times V_{EN\_F}$$

(3)

EA20250502A0 www.3peak.com 17 / 34

Figure 13. UVLO Adjustment

#### **Valley Current Limit**

The TPP21206 employs a cycle-by-cycle valley current limit to prevent the positive inductor current from running away. The inductor current is monitored when the low-side MOSFET turns on. If the monitored current of the low-side MOSFET exceeds the valley current limit, the low-side MOSFET remains on until the current returns to the safe level.

The valley current limit protection limits the inductor current without a latch-off behavior. During an overcurrent condition, the load current exceeds the valley current limit; thus, the output voltage tends to decrease. It ends up with triggering the under-voltage protection (UVP) threshold. Refer to the UVP section for details.

The valley current limit can be programmable through an external resistor from the CS pin to the ground. One ±1% tolerance resistor is recommended to ensure an accurate current limit threshold. The valley current limit threshold setting from the resistor can be calculated by below equation.

$$I_{LIMIT\_LS} = \frac{V_{LIMIT}}{R_{LIMIT}(\Omega) \times G_{OCP\ LS}}$$

(4)

where  $V_{\text{LIMIT}}$  is the Current limit reference, and  $R_{\text{LIMIT}}$  is the current limit resistor value.

#### **Peak Current Limit**

The TPP21206 also employs a fixed, cycle-by-cycle peak current limit. The current is monitored when the high-side MOSFET turns on. If the monitored current of the high-side MOSFET exceeds the peak current limit, the high-side MOSFET turns off to avoid the inductor current from further increasing. Delay needs to be taken into account which may cause the sensed current to be slightly different from open-loop current limits.

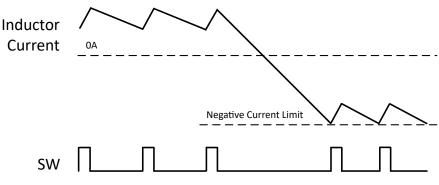

#### **Negative Current Limit**

The TPP21206 also employs a fixed, cycle-by-cycle negative current limit. Similar to the valley current limit, the current is monitored when the low-side MOSFET turns on. If the monitored current of the low-side MOSFET exceeds the negative current limit, the low-side MOSFET turns off, and then the high-side MOSFET turns on for a proper time. After the high-side MOSFET on-time expires, the low-side MOSFET turns on again.

www.3peak.com 18 / 34 EA20250502A0

Figure 14. Negative Current Limit Operation

#### **Under Voltage Protection (UVP)**

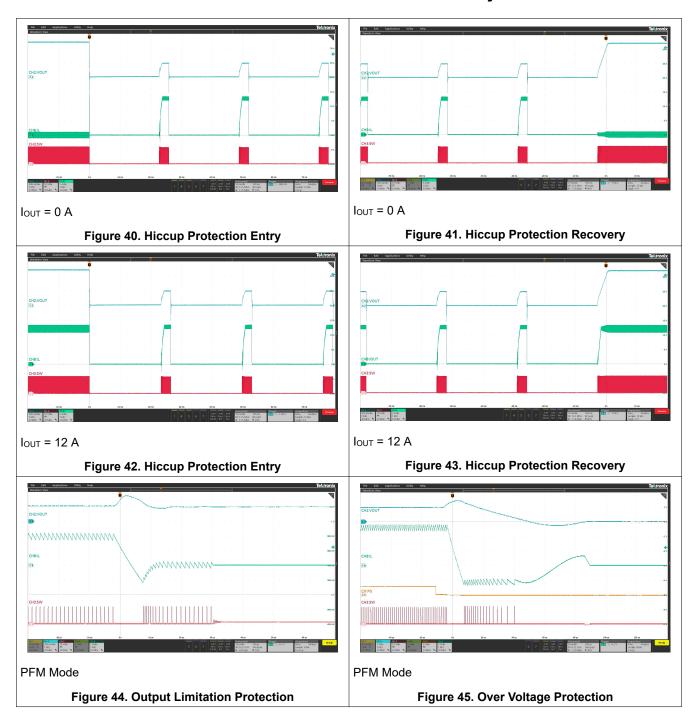

If the output voltage drops lower than 80% of the regulation voltage level, the UVP comparator detects and an internal delay counter is triggered. After this UVP delay time, the device enters the hiccup mode. The UVP function is enabled after the soft-start period is complete.

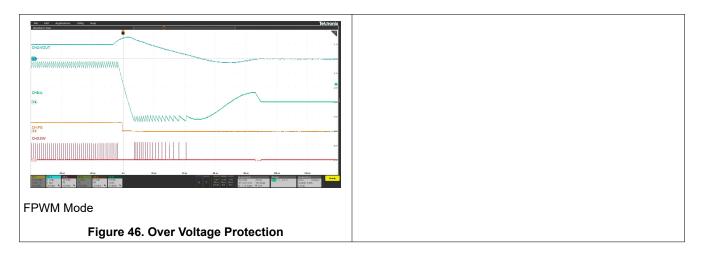

#### **Over Voltage Protection (OVP)**

If the output voltage rises higher than 116% of the regulation voltage level, the OVP comparator detects and the device latches off the high-side MOSFET and turns on the low-side MOSFET until the device reaches the negative current limit. Upon reaching the negative current limit, the low-side MOSFET turns off and the high-side MOSFET turns on again. The device operates in this operation until the output voltage is pulled below the UVP threshold voltage for approximately 60 µs. After the UVP delay time, both the high-side MOSFET and the low-side MOSFET are latched off. The fault is cleared with a reset of VIN or by re-toggling the EN pin.

#### **Output Limitation Protection**

The TPP21206 employs the output limitation protection to regulate the output voltage to the targeted value. It protects the output voltage at a much lower overvoltage threshold of 5% above the regulation voltage level. The output limitation protection does not trigger the over-voltage fault, so this protection is non-latching. During the protection, the device operates in forced-PWM mode. The low-side MOSFET turns on beyond the zero inductor current, which quickly discharges the output capacitors to help regulate the output voltage to the set value. During the protection, the cycle-by-cycle negative current limit is also activated to ensure the safe operation of the internal power switches.

#### **Short Circuit Protection**

To further ensure the protection during prolonged overload or short circuits, the device features hiccup overload protection. When the inductor current is clamped at the set current limit and the feedback voltage drops below the UVP threshold, the device enters the hiccup mode. Entering the hiccup sleep period for approximately 20 ms, the device stops switching and restarts a normal soft start operation after the recovery time. If the overload still exists, the device keeps switching with the current limit and turns off the power switches again. The device can automatically recover to normal operation when the overload condition is removed. The hiccup function is disabled at the normal soft start period to avoid being mistakenly triggered.

#### **Thermal Shutdown**

Once the temperature of the device rises above the internal over-temperature shutdown threshold, the internal temperature sensor shuts down the device. The device recovers operating when the temperature falls below the threshold with hysteresis.

www.3peak.com 19 / 34 EA20250502A0

### **Application and Implementation**

#### Note

Information in the following application sections is not part of the 3PEAK's component specification and 3PEAK does not warrant its accuracy or completeness. 3PEAK's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### **Application Information**

The TPP21206 is a high-efficiency, easy-to-use, fully integrated synchronous step-down regulator with 2.7-V to 16-V wide input voltage range and 12-A continuous output current capability. The TPP21206 adopts constant-on-time control to achieve the fast load transient performance and the easy use of external components. The device provides FPWM mode to optimize the output ripple and PSM mode to improve the light load efficiency. The device also has three options for switching frequency selection: 600 kHz, 800 kHz, and 1000 kHz. The operation mode and switching frequency are selected by connecting a resistor from the MODE pin to the AGND pin.

Figure 15. Typical Application Circuit

#### **Choosing Switching Frequency**

Switching frequency of the DCDC regulator is a compromise between system efficiency and total solution size. The lower switching frequency can help reduce power losses and usually results in higher system efficiency, while the higher switching frequency allows the selection of smaller external components, such as inductors and output capacitors, and increases the system power density.

#### **Setting Output Voltage**

The external resistor divider network connected to the FB pin sets the output voltage. The resistance of the divider is a compromise between noise suppression and output current consumption. The smaller value resistor reduces noise sensitivity but also increases the quiescent current of the system and reduces light load efficiency. It is typically recommended to select a  $10-k\Omega$  resistor for the bottom feedback resistor. If low quiescent current and high light load efficiency are required, a larger

www.3peak.com 20 / 34 EA20250502A0

top feedback resistor can be selected, and one feedback capacitor can be used to improve the phase margin. Once the bottom feedback resistor is selected, the value of the top feedback resistor can be calculated with the equation below.

$$R_{FBB} = \frac{V_{FB} * R_{FBT}}{V_{OUT} - V_{FB}}$$

(5)

where  $V_{FB}$  is the internal reference voltage, which is typically 0.6 V for TPP21206. For a 1.2-V output, if  $R_{FBB}$  = 10 k $\Omega$ ,  $R_{FBT}$  = 15.2 k $\Omega$  is chosen.

#### **Inductor Selection**

The selection of the inductor affects steady-state operation as well as transient behavior and loop stability. These factors make it the most important component in power regulator design. There are three important inductor specifications: inductor value, DC resistance, and saturation current. The inductor value is designed based on the desired peak-to-peak ripple current and is typically chosen to be in the range of 20% to 40% of the maximum output current. Once the desired inductor ripple current is selected, the inductor value can be calculated with the equation below.

$$L = \frac{V_{OUT}}{f_{SW} * \Delta I_L} * \left( 1 - \frac{V_{OUT}}{V_{IN}} \right)$$

(6)

where  $f_{SW}$  is the switching frequency and  $\Delta I_L$  is the inductor ripple current.

When the inductor current approaches its saturation level, the effective inductance can fall to a fraction of the zero current value. Although one high-side valley current limit is integrated to avoid the current runaway, the inductor current can rise to a high value very rapidly if the inductor is saturated. The inductor saturation current must leave a safe margin from the high-side peak current limit in the worst-case conditions. The RMS current and peak current of the inductor can be calculated with the equation below.

$$I_{L\_PEAK} = I_{OUT} + \frac{\Delta I_L}{2}$$

(7)

$$I_{L\_PEAK} = I_{OUT} + \frac{\Delta I_{L}}{2}$$

$$I_{L\_RMS} = \sqrt{I_{OUT}^2 + \frac{\Delta I_{L}^2}{12}}$$

(8)

#### **Input Capacitor Selection**

The input capacitor of the step-down regulator is used to supply the AC input current and maintain a stable DC input voltage. At least a 10-µF capacitance of ceramic input capacitor is recommended. Additional input capacitance may be required to meet ripple and transient requirements. A high-quality ceramic capacitor, X5R or X7R, is recommended because of low equivalent series resistance (ESR) characteristics and small capacitance variations over a temperature range. In addition, one small value and small case size, ceramic capacitor (such as 100 nF, 0603 package) is recommended to be used at the input and be placed as close as possible to the VIN and GND pins. This can provide a high-frequency bypass for the internal control circuits. The input capacitor can be calculated with the equation below when the input voltage ripple is determined.

$$\Delta V_{IN} = \frac{I_{OUT}}{f_{SW} * C_{IN}} * \frac{V_{OUT}}{V_{IN}} * \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

(9)

where C<sub>IN</sub> is the input capacitance value.

The input capacitor ripple current rating should be greater than the maximum input current ripple. The RMS current of the input capacitor can be calculated with the equation below.

$$I_{\text{CIN\_RMS}} = I_{\text{OUT}} * \sqrt{\frac{V_{\text{OUT}}}{V_{\text{IN}}}} * \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}\right)$$

(10)

The worst case for the input voltage ripple and RMS current occurs when the duty cycle is 50%.

www.3peak.com 21 / 34 EA20250502A0

#### **Output Capacitor Selection**

The output capacitance is mainly selected to meet the requirement of the output ripple and voltage change during a load transient. Then the control loop is compensated for the output capacitor selected. The output voltage ripple is related to the capacitance and ESR of the output capacitor. Assuming the capacitor has a small ESR, the minimum output capacitance needed for a given output ripple voltage can be calculated with the equation below.

$$C_{OUT} > \frac{\Delta I_L}{8 * f_{SW} * \Delta V_{OUT}}$$

(11)

where  $\Delta I_L$  is the inductor ripple current and  $\Delta V_{OUT}$  is the output voltage ripple.

If a large ESR capacitor is used, it contributes additional output ripple. ESR ripples can be neglected for ceramic capacitors but must be considered if electrolytic capacitors are used. The maximum ESR for a given ripple can be calculated with the equation below.

$$R_{ESR} < \frac{\Delta V_{OUT}}{\Delta I_L} - \frac{1}{8 * f_{SW} * C_{OUT}}$$

(12)

The effective value of the ceramic capacitor decrease should be considered when the output DC bias voltage is added across the capacitors. The RMS current of the output capacitor can be calculated with the equation below.

$$I_{COUT\_RMS} = \frac{V_{OUT} * (V_{IN\_MAX} - V_{OUT})}{\sqrt{12} * V_{IN\_MAX} * L * f_{SW}}$$

(13)

where V<sub>IN MAX</sub> is the maximum input voltage, and L is the selected inductor value.

#### **Bootstrap Capacitor Selection**

A typical 0.1-µF bootstrap capacitor is connected between the BOOT pin and the SW pin. It is recommended to use a ceramic capacitor with X5R or superior grade dielectric and a voltage rating of 10 V or higher.

www.3peak.com 22 / 34 EA20250502A0

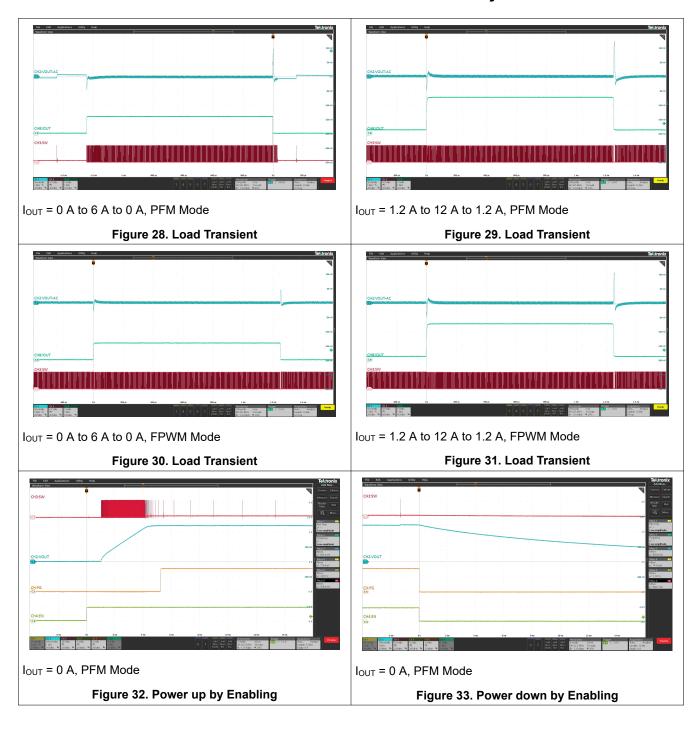

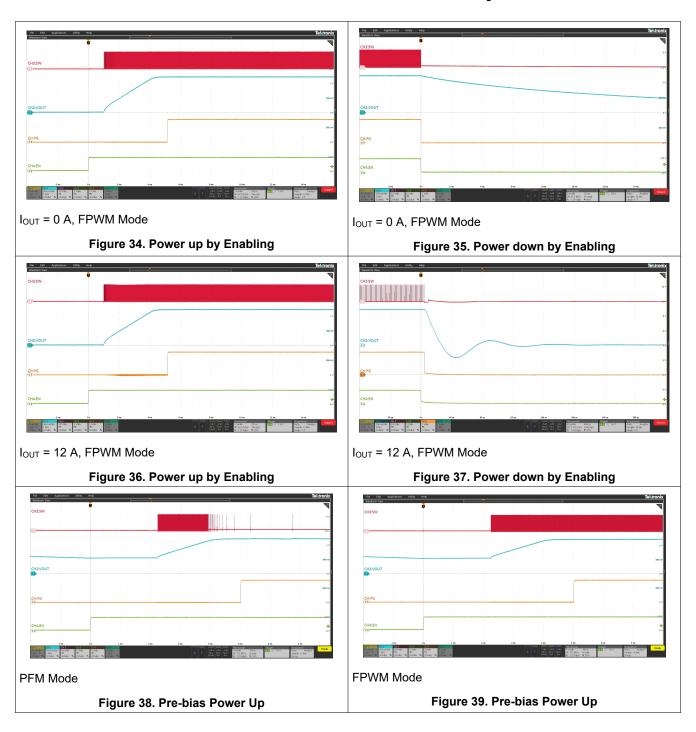

### **Application Waveforms**

All test conditions: V<sub>IN</sub> = 12 V, V<sub>OUT</sub> = 1.2 V, F<sub>SW</sub> = 800 kHz, FPWM Mode, T<sub>A</sub> = 25 °C, unless otherwise noted.

www.3peak.com 23 / 34 EA20250502A0

www.3peak.com 24 / 34 EA20250502A0

www.3peak.com 27 / 34 EA20250502A0

www.3peak.com 28 / 34 EA20250502A0

### Layout

### **Layout Guideline**

The performance of switching regulators heavily depends on the quality of the PCB layout, especially for thermal design and EMI design. Even if the schematic design is good, an inappropriate PCB layout can disrupt the operation of the regulator.

- 1. The input MLCC capacitors should be placed as close to the VIN and PGND pins as possible.

- 2. The major MLCC capacitors should be placed on the same layer as the TPP21206.

- 3. Maximize the VIN and PGND copper plane to minimize the parasitic impedance.

- 4. Place as many PGND vias as possible close to the PGND pins to minimize both parasitic impedance and thermal resistance.

- 5. Place the VCC decoupling capacitor as close as possible to the device.

- 6. Connect AGND and PGND at the point of the ground connection of the VCC capacitor.

- 7. Place the BOOT capacitor as close as possible to the BOOT and SW pins with wider traces to route the path.

- 8. Place the SS/TR capacitor close to the SS/TR pin to RGND.

- 9. The feedback terminal is sensitive to noise, so the feedback resistor should be placed as close as possible to the device. Do not place vias on the feedback output and ground sense trace.

www.3peak.com 29 / 34 EA20250502A0

### **Layout Recommendations**

Figure 47. Layout Example

www.3peak.com 30 / 34 EA20250502A0

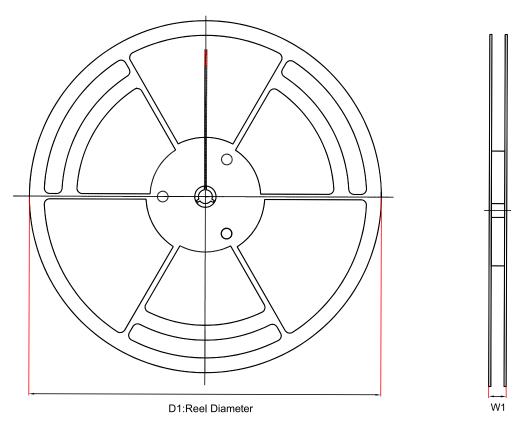

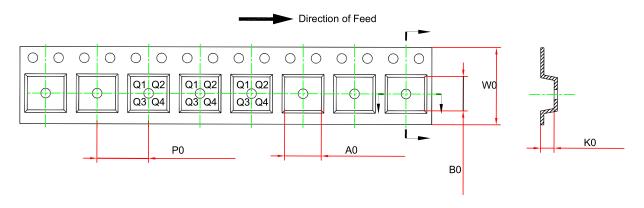

### **Tape and Reel Information**

| Order Number   | Package   | D1<br>(mm) | W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | W0<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------|------------|------------|------------|------------|------------|------------|------------|------------------|

| TPP212060-FC5R | QFN3X4-21 | 330        | 17.6       | 3.3        | 4.3        | 1.0        | 8.0        | 12.0       | Q1               |

www.3peak.com 31 / 34 EA20250502A0

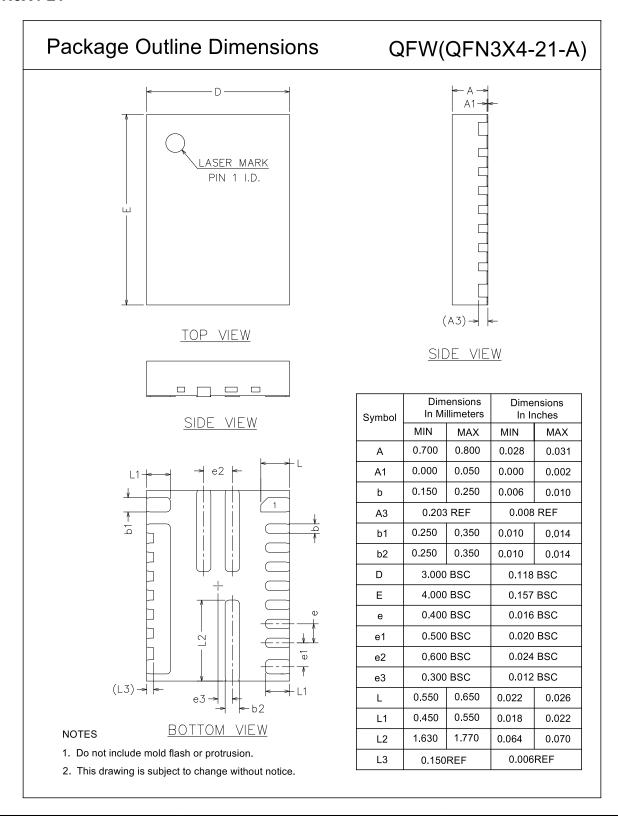

### **Package Outline Dimensions**

#### QFN3X4-21

www.3peak.com 32 / 34 EA20250502A0

### **Order Information**

| Order Number   | Operating Ambient Temperature Range | Package Marking Information |      | MSL     | Transport Media,<br>Quantity | Eco Plan |  |

|----------------|-------------------------------------|-----------------------------|------|---------|------------------------------|----------|--|

| TPP212060-FC5R | −40°C to 125°C                      | QFN3X4-21                   | 2120 | Level 3 | Tape & Reel, 3000            | Green    |  |

**Green**: 3PEAK defines "Green" to mean RoHS compatible and free of halogen substances.

www.3peak.com 33 / 34 EA20250502A0

#### IMPORTANT NOTICE AND DISCLAIMER

Copyright<sup>©</sup> 3PEAK 2012-2025. All rights reserved.

**Trademarks.** Any of the 思瑞浦 or 3PEAK trade names, trademarks, graphic marks, and domain names contained in this document /material are the property of 3PEAK. You may NOT reproduce, modify, publish, transmit or distribute any Trademark without the prior written consent of 3PEAK.

**Performance Information.** Performance tests or performance range contained in this document/material are either results of design simulation or actual tests conducted under designated testing environment. Any variation in testing environment or simulation environment, including but not limited to testing method, testing process or testing temperature, may affect actual performance of the product.

**Disclaimer.** 3PEAK provides technical and reliability data (including data sheets), design resources (including reference designs), application or other design recommendations, networking tools, security information and other resources "As Is". 3PEAK makes no warranty as to the absence of defects, and makes no warranties of any kind, express or implied, including without limitation, implied warranties as to merchantability, fitness for a particular purpose or non-infringement of any third-party's intellectual property rights. Unless otherwise specified in writing, products supplied by 3PEAK are not designed to be used in any life-threatening scenarios, including critical medical applications, automotive safety-critical systems, aviation, aerospace, or any situations where failure could result in bodily harm, loss of life, or significant property damage. 3PEAK disclaims all liability for any such unauthorized use.

www.3peak.com 34 / 34 EA20250502A0