### **Features**

- · High Efficiency at Light Loads with Pulse Skipping

- Ultra-low R<sub>DS(ON)</sub> 8-mΩ Highside and 8-mΩ Lowside MOSFETs

- Adjustable Switching Frequency

- Integrated PLL to Synchronize with External Clock

- Adjustable UVLO Voltage and Hysteresis

- Under-voltage and Over-voltage Power Good Output

- · Adjustable Soft-start and Sequencing

- · Low-dropout Operation at Light Loads

- Cycle-by-cycle Current Limit

- 0.6-V 1% Internal Voltage Reference

- 16-Pin QFN3X3-16 with Exposed Pad Package

- –40°C to 125°C Ambient Temperature Range

- · Communication and Networking Devices

- Personal Electronics, Personal Healthcare

### **Description**

The TPP05608 is a 6-V 6-A synchronous step-down converter with integrated power FETs.

The TPP05608 employs current-mode topology to support various applications. With a wide range of switching frequency support, the device can reduce the inductor size. The high precision reference provides output voltage with <1% accuracy over temperature, which is especially useful for low-voltage loads.

The TPP05608 has various diagnostics and protections such as undervoltage lock-out (UVLO), power good, current limit, and thermal shutdown.

## **Applications**

Point-of-load Regulators

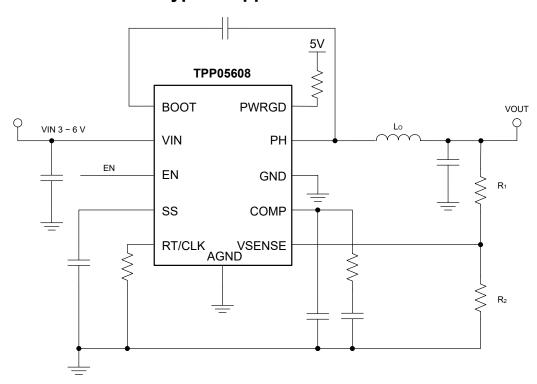

## **Typical Application Circuit**

## **Table of Contents**

| Features                                | 1  |

|-----------------------------------------|----|

| Applications                            | 1  |

| Description                             | 1  |

| Typical Application Circuit             | 1  |

| Product Family Table                    | 3  |

| Revision History                        | 3  |

| Pin Configuration and Functions         | 4  |

| Specifications                          | 5  |

| Absolute Maximum Ratings <sup>(1)</sup> | 5  |

| ESD, Electrostatic Discharge Protection | 5  |

| Recommended Operating Conditions        | 5  |

| Thermal Information                     | 5  |

| Electrical Characteristics              | 6  |

| Typical Performance Characteristics     | 9  |

| Detailed Description                    | 12 |

| Overview                                | 12 |

| Functional Block Diagram                | 12 |

| Feature Description                     | 13 |

| Application and Implementation          | 15 |

| Application Information                 | 15 |

| Typical Application                     | 15 |

| Layout                                  | 17 |

| Layout Guideline                        | 17 |

| Layout Example                          | 17 |

| Tape and Reel Information               | 20 |

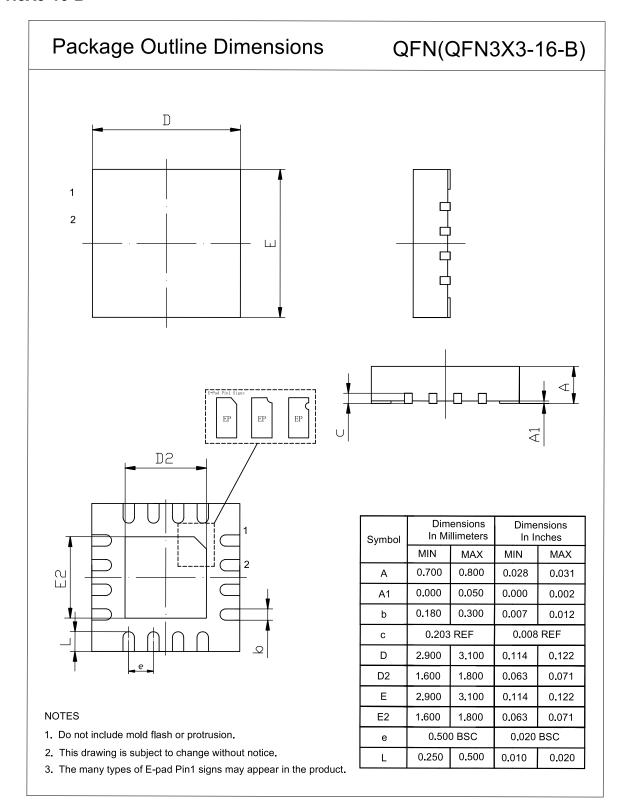

| Package Outline Dimensions              | 21 |

| QFN3X3-16-B                             | 21 |

| Order Information                       | 22 |

| IMPORTANT NOTICE AND DISCLAIMER         | 23 |

# **Product Family Table**

| Order Number   | Package   |

|----------------|-----------|

| TPP056080-QFMR | QFN3X3-16 |

## **Revision History**

| Date       | Revision  | Notes           |

|------------|-----------|-----------------|

| 2021-07-19 | Rev.Pre.0 | Initial version |

| 2022-08-15 | Rev.A.0   | Released        |

www.3peak.com 3 / 24 EA20221101A0

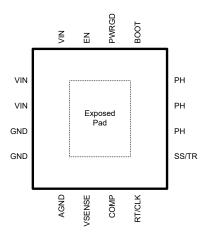

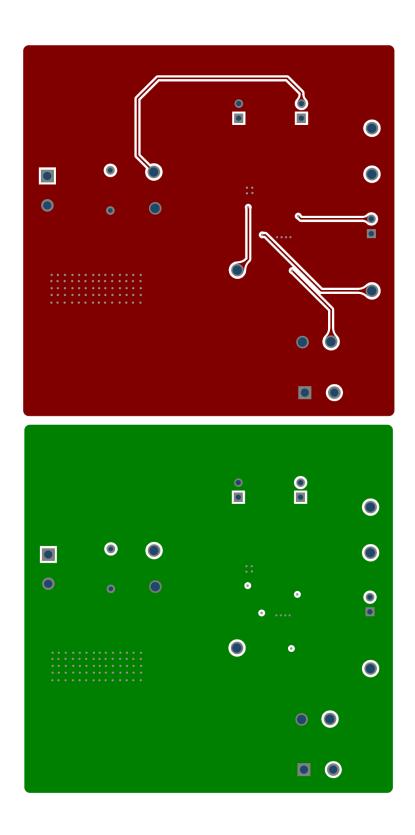

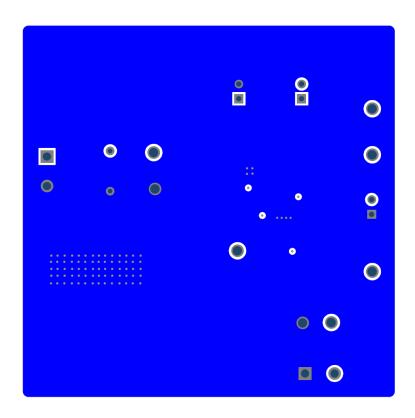

## **Pin Configuration and Functions**

TPP05608 QFN3X3-16 Package Top View

**Table 1. Pin Functions**

| Pin        |        | 1/0 | Donas distribution                                                                                                                                                                                                                                                  |

|------------|--------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.        | Name   | I/O | Description                                                                                                                                                                                                                                                         |

| 1, 2, 16   | VIN    | I   | Power supply voltage input pin. Connect VIN to GND with a 1-μF or greater capacitor.                                                                                                                                                                                |

| 3, 4       | GND    | _   | Ground                                                                                                                                                                                                                                                              |

| 5          | AGND   | _   | Analog ground                                                                                                                                                                                                                                                       |

| 6          | VSENSE | I   | Voltage feedback sense input, connected to internal negative node of error amplifier.                                                                                                                                                                               |

| 7          | COMP   | _   | Error amplifier output                                                                                                                                                                                                                                              |

| 8          | RT/CLK | I   | Frequency selection and external clock input. When using it as frequency setting mode, an external connected resistor sets switching frequency; When using it as clock synchronization input, the input is a high impedance clock input for internal PLL.           |

| 9          | SS/TR  | I   | Soft-start and tracking input. When using the soft-start mode, an external capacitor connected to this pin sets output ramping time; When using track/sequence mode, the voltage on this pin overrides the internal voltage reference thus sets the output voltage. |

| 10, 11, 12 | PH     | 0   | Switching node                                                                                                                                                                                                                                                      |

| 13         | воот   | I   | Bootstrap capacitor between BOOT and PH, recommend using a 0.1-μF ceramic capacitor with 10-V or higher voltage rating.                                                                                                                                             |

| 14         | PWRGD  | Р   | Open-drain power good output                                                                                                                                                                                                                                        |

| 15         | EN     | I   | Device enable pin with internal pull-up current source. Threshold can be increased via external resistors                                                                                                                                                           |

www.3peak.com 4 / 24 EA20221101A0

## **Specifications**

### Absolute Maximum Ratings (1)

|                                       | Parameter                           |      |     | Unit |

|---------------------------------------|-------------------------------------|------|-----|------|

| EN, VIN, RT/CLK, PWRGD                | In must walke me                    | -0.3 | 6.5 | ٧    |

| COMP, SS/TR, VSENSE                   | Input voltage                       | -0.3 | 3   | V    |

| BOOT-PH                               |                                     |      | 6.5 |      |

| PH                                    | Output valtage                      | -0.7 | 6.5 | V    |

| PH (20-ns transient)                  | Output voltage                      | -2   | 10  | V    |

| PH (5-ns transient)                   |                                     | -4   | 12  |      |

| I <sub>EN</sub> , I <sub>RT_CLK</sub> | Source current                      |      | 100 | μA   |

| I <sub>COMP</sub> , I <sub>SS</sub>   | Circle supposed                     |      | 100 | μA   |

| I <sub>PWRGD</sub>                    | Sink current                        |      | 10  | mA   |

| TJ                                    | Operating junction temperature      | -40  | 150 | °C   |

| T <sub>STG</sub>                      | Storage Temperature Range           | -65  | 150 | ů    |

| TL                                    | Lead Temperature (Soldering 10 sec) |      | 260 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

### **ESD, Electrostatic Discharge Protection**

| Symbol | Parameter                | Condition                  | Minimum Level | Unit |

|--------|--------------------------|----------------------------|---------------|------|

| НВМ    | Human Body Model ESD     | ANSI/ESDA/JEDEC JS-001 (1) | ±2            | kV   |

| CDM    | Charged Device Model ESD | ANSI/ESDA/JEDEC JS-002 (2) | ±1            | kV   |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### **Recommended Operating Conditions**

|                 | Parameter                      |     |  | Max | Unit |

|-----------------|--------------------------------|-----|--|-----|------|

| V <sub>IN</sub> | Input Voltage                  | 2.9 |  | 6   | V    |

| TJ              | Operating Junction Temperature | -40 |  | 150 | °C   |

### **Thermal Information**

| Package Type | θ <sub>ЈА</sub> | θυς | Unit |

|--------------|-----------------|-----|------|

| QFN3X3-16    | 45              | 50  | °C/W |

www.3peak.com 5 / 24 EA20221101A0

<sup>(2)</sup> This data was taken with the JEDEC low effective thermal conductivity test board.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **Electrical Characteristics**

All test condition is at  $T_A$  =  $-40~^{\circ}C$  to 125  $^{\circ}C$  .  $V_{IN}$  = 3 V to 6 V, unless otherwise noted.

| Symbol                    | Parameter                              | Conditions                                                    | Min  | Тур  | Max  | Unit |

|---------------------------|----------------------------------------|---------------------------------------------------------------|------|------|------|------|

| Supply Vo                 | Itage and Current                      |                                                               |      | -    |      |      |

| V <sub>UVLO_Risin</sub>   | UVLO Rising Threshold                  |                                                               | 2.54 | 2.61 | 2.68 | V    |

| VUVLO_Fallin              | UVLO Falling Threshold                 |                                                               | 2.4  | 2.48 | 2.68 | V    |

| I <sub>D</sub>            | Shutdown supply current                | EN = 0 V, 25°C, 2.9 V ≤ VIN ≤ 6<br>V                          |      | 1    |      | μA   |

| IQ                        | Operating non-switching supply current | VSENSE = 0.6 V, VIN = 5 V,<br>25°C, f <sub>SW</sub> = 500 kHz |      | 800  | 1300 | μA   |

| Enable an                 | d Under Voltage Lock Out               |                                                               |      |      |      |      |

| $V_{TH(EN\_Risi}$         | Rising Edge                            |                                                               | 1.21 | 1.27 | 1.32 | V    |

| V <sub>TH(EN_Falli</sub>  | Falling Edge                           |                                                               | 1.11 | 1.17 | 1.23 | V    |

| I <sub>EN_H</sub>         | EN = H                                 |                                                               | -2.8 | -3.6 | -4.4 | μΑ   |

| I <sub>EN_L</sub>         | EN = L                                 |                                                               | -0.5 | -0.7 | -1   | μΑ   |

| Voltage Re                | eference                               |                                                               |      | ı    |      |      |

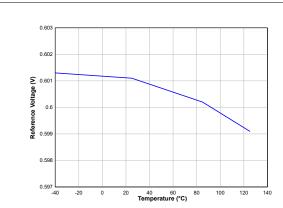

| V <sub>REF</sub>          | Voltage Reference                      | 2.9 V ≤ VIN ≤ 6 V, -40°C < T <sub>J</sub> < 150°C             | 594  | 600  | 606  | mV   |

| Output Sta                | age                                    |                                                               |      |      |      |      |

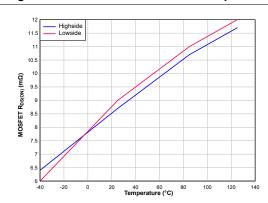

| В                         | Lligh aide quitab en registance        | BOOT-PH = 5 V                                                 |      | 8    |      |      |

| R <sub>DS(ON)_HS</sub>    | High-side switch on-resistance         | BOOT-PH = 2.95 V                                              |      | 10   |      | 0    |

| D                         | Low-side switch on-resistance          | VIN = 5 V                                                     |      | 8    |      | mΩ   |

| R <sub>DS(ON)_LS</sub>    | Low-side Switch on-resistance          | VIN = 2.95 V                                                  |      | 10   |      |      |

| <b>4</b>                  | Minimum ON-time                        | I <sub>OUT</sub> = 3 A                                        |      | 90   |      | no   |

| t <sub>ON(min)</sub>      | William ON-une                         | I <sub>OUT</sub> = 0 A                                        |      | 100  |      | ns   |

| t <sub>OFF(min)</sub> (1) | Minimum OFF-time                       | BOOT - PH = 3 V, I <sub>OUT</sub> = 3 A                       |      | 70   |      | ns   |

| Rchg                      | BOOT Charge Resistance                 | VIN = 6 V, BOOT-PH = 6 V                                      |      | 6    |      | Ω    |

| $V_{\text{BOOT\_UV}}$     | BOOT UVLO Threshold                    |                                                               |      | 2.2  |      | V    |

| Error Amp                 | lifier                                 |                                                               |      |      |      |      |

| I <sub>EA_IN</sub>        | EA input current                       |                                                               |      | 7    |      | nA   |

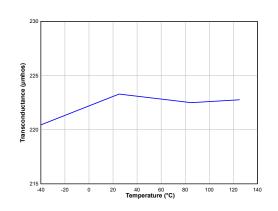

| g <sub>m</sub>            | Error amplifier transconductance       | -5 μA < I <sub>(COMP)</sub> < 5 μA                            | 200  | 220  | 240  | μS   |

| I <sub>EA_OUT_SR</sub>    | Error amplifier output source current  | V <sub>(COMP)</sub> = 1 V 100-mV overdrive                    | 22   | 30   | 40   | μΑ   |

| lea_out_sin               | Error amplifier output sink current    | V <sub>(COMP)</sub> = 1 V –100-mV overdrive                   | 22   | 30   | 40   | μА   |

www.3peak.com 6 / 24 EA20221101A0

| Symbol                 | Parameter                                        | Conditions                                                      | Min | Тур   | Max  | Unit   |

|------------------------|--------------------------------------------------|-----------------------------------------------------------------|-----|-------|------|--------|

| gsw                    | Transconductance from COMP to switching current  |                                                                 |     | 20    |      | μS     |

| Current Li             | mit                                              |                                                                 |     |       | 1    | 1      |

| ILIMIT_HS              | Fsw = 500 kHz                                    |                                                                 |     | 11    |      | А      |

| N <sub>DEGLITCH</sub>  | Over current deglitch cycle count                |                                                                 |     | 512   |      | Cycles |

| NHICCUP                | Hiccup cycles                                    |                                                                 |     | 16512 |      | Cycles |

| ILIMIT_LSSR<br>C       | Low-side sourcing current threshold              |                                                                 |     | 8     |      | А      |

| VLIMIT_LSNE<br>G       | Low-side FET negative current threshold          |                                                                 |     | 3.2   |      | А      |

| Thermal P              | rotection                                        |                                                                 |     |       |      |        |

| T <sub>SD</sub>        | Thermal shutdown threshold                       |                                                                 |     | 175   |      | °C     |

| V <sub>HYS</sub>       | Thermal shutdown hysteresis                      |                                                                 |     | 12    |      | °C     |

| Timing                 |                                                  |                                                                 |     |       |      |        |

|                        | Switching frequency range                        |                                                                 | 200 |       | 1600 | kHz    |

| f <sub>SW</sub>        | RT clock frequency                               | R <sub>T</sub> = 82.5 kΩ                                        | 450 | 500   | 550  | kHz    |

| t <sub>CLK(min)</sub>  | Minimum CLK pulse width                          |                                                                 |     | 75    |      | ns     |

| V <sub>RT</sub>        | RT/CLK Voltage                                   | R <sub>T</sub> = 82.5 kΩ                                        |     | 0.5   |      | V      |

| V <sub>CLK_H</sub>     | RT/CLK High Threshold                            |                                                                 |     | 1.5   | 1.8  | V      |

| V <sub>CLK_L</sub>     | RT/CLK Low Threshold                             |                                                                 | 0.7 | 0.95  |      | V      |

| trt_delay              | RT/CLK falling edge to PH rising edge delay      | f <sub>SW</sub> = 500 kHz                                       |     | 55    |      | ns     |

| t <sub>PLL_Lock</sub>  | PLL lock-in time                                 |                                                                 |     | 200   |      | μs     |

| Soft-start             | and Tracking                                     |                                                                 |     |       |      |        |

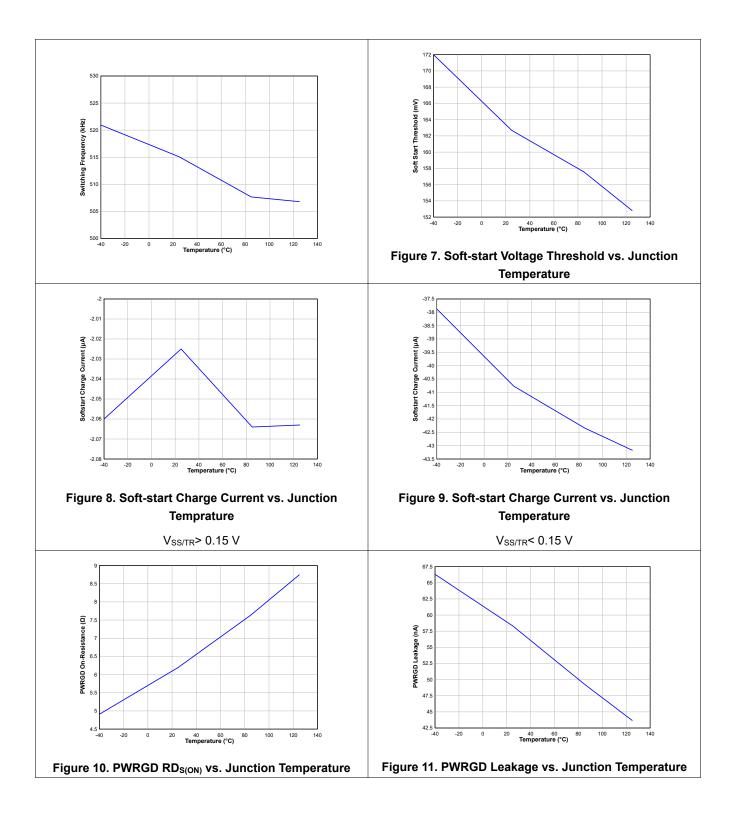

|                        | 0 % 4 4 4                                        | V <sub>(SS/TR)</sub> < 0.15 V                                   |     | 41.5  |      |        |

| Iss                    | Soft-start charge current                        | V <sub>(SS/TR)</sub> > 0.15 V                                   |     | 2.2   |      | μA     |

| Vss_matchi<br>ng       | SS/TR to VSENSE matching                         | V <sub>IN</sub> = 3.3 V                                         |     | 60    |      | mV     |

| Vss_cross<br>over      | SS/TR to reference crossover                     |                                                                 |     | 120   |      | mV     |

| Iss_dischg             | SS/TR discharge current                          | V <sub>SS</sub> = 0.4 V, VSENSE = 0 V, V <sub>IN</sub> = 2.8-6V |     | 1200  |      | μA     |

| Vss_dischg             | SS/TR discharge voltage, over load condition     | VSENSE = 0 V                                                    |     | 4.5   |      | mV     |

| POWERGO                | OOD                                              |                                                                 |     |       |      |        |

| V <sub>TH_OVP_RI</sub> | Over voltage protection VSENSE rising threshold  | Percentage of VREF                                              |     | 108   |      | %      |

| V <sub>TH_OVP_FA</sub> | Over voltage protection VSENSE falling threshold | Percentage of VREF                                              |     | 106   |      | %      |

www.3peak.com 7 / 24 EA20221101A0

| Symbol                 | Parameter                                            | Conditions                                                     | Min | Тур  | Max  | Unit |

|------------------------|------------------------------------------------------|----------------------------------------------------------------|-----|------|------|------|

| V <sub>TH_UVP_RI</sub> | Under voltage protection<br>VSENSE rising threshold  | Percentage of VREF                                             |     | 93   |      | %    |

| V <sub>TH_UVP_FA</sub> | Under voltage protection<br>VSENSE falling threshold | Percentage of VREF                                             |     | 91   |      | %    |

| ILKG_PWRGD             | Output high leakage                                  | VSENSE = V <sub>REF</sub> , V <sub>(PWRGD)</sub> = 5.5<br>V    |     | 5    |      | nA   |

| R <sub>PWRGD</sub>     | PWRGD on-resistance                                  | V <sub>IN</sub> = 5 V                                          |     | 5.5  | 10   | Ω    |

| V <sub>PWRGD_LO</sub>  | PWRGD low                                            | I <sub>(PWRGD)</sub> = 3 mA                                    |     |      | 0.1  | V    |

| VIN_PWRGD              | Minimum VIN for valid output                         | $V_{(PWRGD)} < 0.5 \text{ V}, I_{(PWRGD)} = 100$ $\mu\text{A}$ |     | 0.85 | 1.15 | V    |

<sup>1.</sup> Guranteed by design

www.3peak.com 8 / 24 EA20221101A0

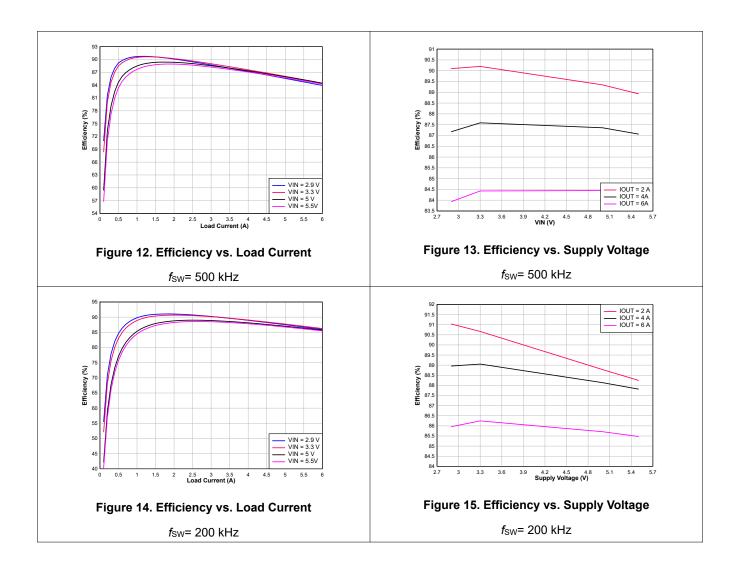

## **Typical Performance Characteristics**

All test condition:  $V_{IN}$  =5 V,  $V_A$  = 25°C, unless otherwise noted.

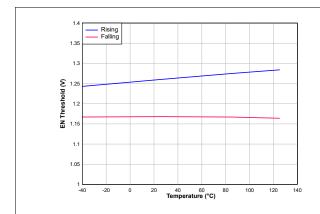

Figure 1. EN Threshold vs. Junction Temperature

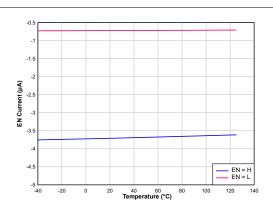

Figure 2. EN Current vs. Junction Temperature

Figure 3. Reference Voltage vs. Junction Temperature

Figure 4. MOSFET On-resistance vs. Junction Temperature

Figure 5. Transconductance vs. Junction Temperature

Figure 6. High-side Current Limit Threshold vs. Junction Temperature

www.3peak.com 9 / 24 EA20221101A0

www.3peak.com 10 / 24 EA20221101A0

www.3peak.com 11 / 24 EA20221101A0

### **Detailed Description**

#### Overview

The TPP05608 is a 6-V, 6-A, synchronous step-down converter with integrated N-channel MOSFETs as power stage. The device employs peak current mode control mechanism with constant frequency, supporting from 200kHz to 2000kHz switching frequency.

The TPP05608 has enable input EN with internal pull-up current source. The EN threshold can be adjusted by external resistors. The device also support external PWM input with integrated phase-locked-loop (PLL). The RT/CLK pin can be used to synchronize switching frequency with external clock source.

The device has high efficiency switching power stage with ultra-low on-resistance. The device also integrates boot recharge diode with bootstrap under-voltage lock out. The device supports high dutycycle close to 100% considering boot recharge cycles.

The TPP05608 has high-precision 0.6-V reference with 1% precision. The output voltage could be as low as 0.6V. The device also has output voltage monitor and open-drain power good output for output over voltage and under voltage monitoring.

SS/TR provides soft-start setting and input tracking feature to set reference voltage accordingly. The device also supports cycle-by-cycle current limit and hiccup protection for over current scenarios.

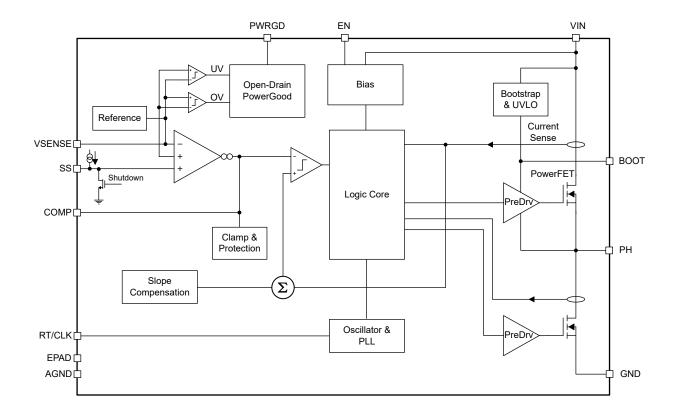

### **Functional Block Diagram**

Figure 16. Functional Block Diagram

www.3peak.com 12 / 24 EA20221101A0

### **Feature Description**

#### **Current Mode Control**

The TPP05608 employs peak current mode control with adjustable switching frequency. The feedback voltage is sensed through VSENSE pin to compare with internal voltage reference by an error amplifier. The output of the error amplifier is compared by PWM comparator with internal voltage ramp and controls power switch. Internal oscillator controls the frequency of switching high-side MOSFET.

The high-side switching current is sensed internally as part of the voltage ramp. Once the PWM comparator detects peak switching current reaches the threshold level set by COMP voltage, the high-side MOSFET is switched off and the low-side MOSFET is switched on. During light-load operation, the device will enter forced-PWM mode with the same switching frequency.

The transconductance error amplifier converts the error voltage between VSENSE pin voltage and internal voltage, whichever lower of the soft-start voltage or internal voltage reference  $V_{REF}$ , to current with transconductance gm of 1300  $\mu$ Mhos during normal operation conditions. It is recommended to connect compensation network between COMP and GND pin to ensure stability across all working ranges. The details are discussed in the application chapter.

#### **Setting Output Voltage**

The precision internal voltage reference produces a 0.6-V voltage reference with ±1% tolerance across operating temperature and voltage ranges. The resistor divider from output voltage to FB pin sets the output voltage.

$$R_{H} = R_{L} \times \left(\frac{V_{OUT} - V_{FB}}{V_{FB}}\right) \tag{1}$$

#### **Soft-Start with Pre-Biased Capability**

The device uses SS node to implement a programmable soft-start feature by controlling ramping up reference voltage. The reference voltage will be the lower of internal reference voltage and SS voltage. The timing of soft-start is programmable via external capacitor connected to SS node.

An internal constant-current source of 2.3  $\mu$ A charges up the external SS/TR capacitor to an internally clamped 2.7V. The timing can be calculated as below equation, measured from 10% to 90%. Reference voltage is 0.6V.

To ensure proper start-up, the device will discharge SS/TR voltage upon powering up if SS/TR voltage is above 54 mV. During any case the device stops switching, such as undervoltage lockout (UVLO), EN pulled low or over temperature protection, the device will discharge SS/TR below 54mV before switching. The device also supports using SS/TR input for tracking as well as power supply sequencing. Sequencing needs to be carefully designed to ensure the system is able to recover from any fault.

$$T_{SS} = \frac{V_{REF} \times C_{SS} \times (90\% - 10\%)}{I_{SS}}$$

(2)

#### RT/CLK

The device supports wide switching frequency from 100kHz to 2000kHz. The frequency is programmable via resistor connected between RT/CLK and GND. The switching frequency will affect solution size, efficiency, and minimal duty cycle. It is suggested that all factors taken care of when selecting switching frequency. The resistor can be calculated via equation.

$$f = \frac{k}{R_{PT}}$$

(3)

The device switching clock supports external clock sources for synchronization. Once a square wave is applied at the RT/CLK pin, the rising edge of SW synchronizes to the falling edge of RT/CLK. It is also suggested to connect a frequency set resistor to RT/CLK pin in case external clock source is not available.

www.3peak.com 13 / 24 EA20221101A0

The first rising edge of RT/CLK sets the device from free-running frequency mode to synchronization mode. The internal 0.5V voltage source is removed and the RT/CLK is set to high impedance mode. It takes 78µs to lock on external clock frequency; When external clock source stops, the device will switch back to free running frequency mode with frequency set by external resistor. During the transition, the device frequency will stay at 70kHz and then switch to the free-running frequency.

#### **Protection**

The device has undervoltage lockout feature with default rising threshold of 4V. It can be adjusted by using EN pin with external resistors. A weak current source of 1.2 µA pulls up the EN pin to internal voltage rail. Another 3.4-µA hysteresis current source provides hysteresis voltage between rising and falling threshold. The resistor values can be calculated via below equations.

Vsys UVLO His the desired system level undervoltage protection rising threshold voltage, Vsys UVLO Lis the desired system level undervoltage protection falling threshold voltage. RUVLOH and RUVLOL are depicted in Figure 16.

$$R_{H} = \frac{V_{START} \left( \frac{V_{EN\_FALLING}}{V_{EN\_RISING}} \right) - V_{STOP}}{I_{P} \left( 1 - \frac{V_{EN\_FALLING}}{V_{EN\_RISING}} \right) + I_{H}}$$

$$R_{L} = \frac{R_{H} \cdot V_{EN\_FALLING}}{V_{STOP} - V_{EN\_FALLING} + R_{H} \cdot (I_{P} + I_{H})}$$

(5)

$$R_{L} = \frac{R_{H} \cdot V_{EN\_FALLING}}{V_{STOP} - V_{EN\_FALLING} + R_{H} \cdot (I_{P} + I_{H})}$$

(5)

14 / 24 EA20221101A0 www.3peak.com

## **Application and Implementation**

#### Note

Information in the following application sections is not part of the 3PEAK's component specification and 3PEAK does not warrant its accuracy or completeness. 3PEAK's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### **Application Information**

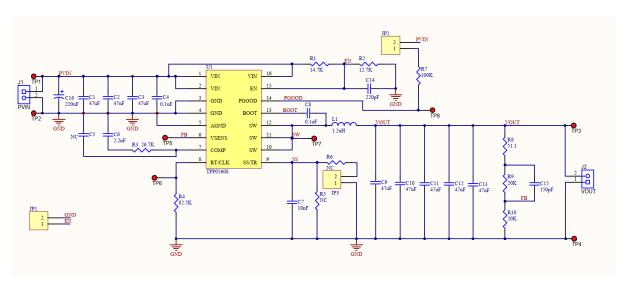

### **Typical Application**

Figure 17. Typical Application Circuit

| C4, C8 | 0.1 μF  | Capacitor,<br>ceramic, 50 V,<br>X5R, 10% | 0603 | Std | Std |

|--------|---------|------------------------------------------|------|-----|-----|

| C5     | Open    | Capacitor, ceramic                       | 0603 | Std | Std |

| C6     | 2200 pF | Capacitor,<br>ceramic, 50 V,<br>X7R, 10% | 0603 | Std | Std |

| C7     | 0.01 μF | Capacitor,<br>ceramic, 25 V,<br>X7R, 10% | 0603 | Std | Std |

| C14    | 220 pF  | Capacitor,<br>ceramic, 50 V,<br>C0G, 5%  | 0603 | Std | Std |

| C15    | 150 pF  | Capacitor,<br>ceramic, 50 V,<br>C0G, 5%  | 0603 | Std | Std |

www.3peak.com 15 / 24 EA20221101A0

| C1-3,C9-13 | 47 μF    | Capacitor,<br>ceramic, 10 V,                                                         | 1206 Std     |               | Std       |

|------------|----------|--------------------------------------------------------------------------------------|--------------|---------------|-----------|

| C16        | 220 μF   | X5R, ±20%  Capacitor,  Electrolytic, 25  VDC                                         | 8*8mm        | 860020474012  | Wurth     |

| L1         | 1.2 µH   | Inductor, SMD<br>Shielded Power,<br>11.8 A, 7.4 mΩ                                   | 5.3 × 5.5 mm | XAL5030-122ME | Coilcraft |

| R1         | 14.7 kΩ  | Resistor, chip, 1/10W, 1%                                                            | 0603         | 0603 Std      |           |

| R2         | 12.7 kΩ  | Resistor, chip, 1/10W, 1%                                                            | 0603         | Std           | Std       |

| R3         | 26.7 kΩ  | Resistor, chip, 1/10W, 1%                                                            | 0603         | Std           | Std       |

| R4         | 82.5 kΩ  | Resistor, chip, 1/10W, 1%                                                            | 0603         | Std           | Std       |

| R5-6       | Open     | Resistor, chip, 1/10W, 1%                                                            | 0603         | 0603 Std      |           |

| R7         | 100 kΩ   | Resistor, chip, 1/10W, 1%                                                            | 0603         | Std           | Std       |

| R8         | 51.1 Ω   | Resistor, chip, 1/10W, 1%                                                            | 0603 Std     |               | Std       |

| R9, R10    | 20.0 kΩ  | Resistor, chip, 1/10W, 1%                                                            | 0603 Std     |               | Std       |

| U1         | TPP05608 | IC, 3-V to 6-V Input, 6-AOutput, 2 MHz, Sync. Step-Down Switcher With Integrated FET | QFN          | TPP05608      | 3peak     |

www.3peak.com 16 / 24 EA20221101A0

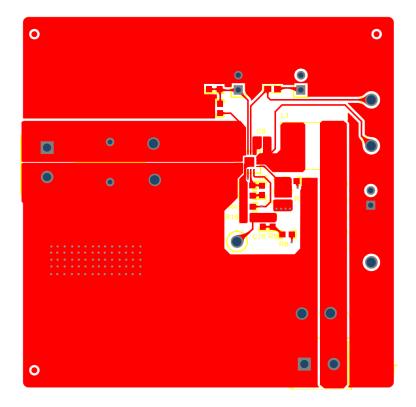

## Layout

## **Layout Guideline**

• Exposed pad must be connected to the PCB ground plane directly, the copper area must be as large as possible.

•

## **Layout Example**

www.3peak.com 17 / 24 EA20221101A0

www.3peak.com 19 / 24 EA20221101A0

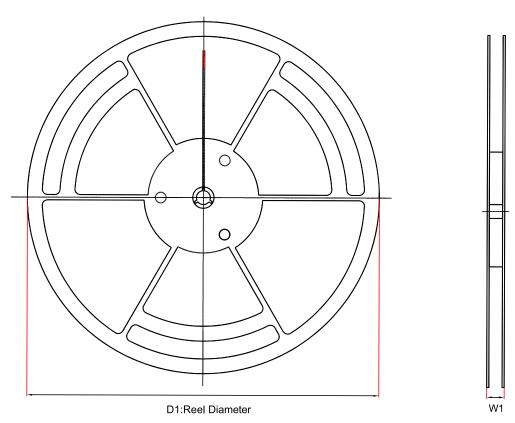

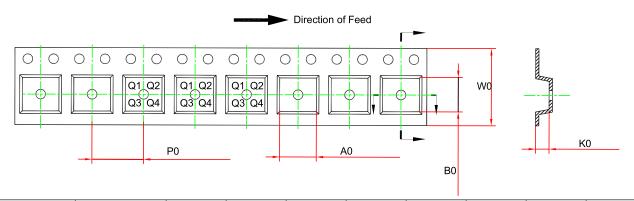

## **Tape and Reel Information**

| Order Number       | Package   | D1 (mm) | W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P0 (mm) | W0 (mm) | Pin1<br>Quadrant |

|--------------------|-----------|---------|---------|---------|---------|---------|---------|---------|------------------|

| TPP056080-<br>QFMR | QFN3X3-16 | 330     | 17.6    | 3.3     | 3.3     | 1       | 8       | 12      | Q2               |

www.3peak.com 20 / 24 EA20221101A0

## **Package Outline Dimensions**

### QFN3X3-16-B

www.3peak.com 21 / 24 EA20221101A0

### **Order Information**

| Order Number   | Operating Temperature<br>Range | Package   | Marking Information | MSL | Transport Media, Quantity | Eco Plan |

|----------------|--------------------------------|-----------|---------------------|-----|---------------------------|----------|

| TPP056080-QFMR | -40 to 125°C                   | QFN3X3-16 | 5680                | 3   | Tape and Reel, 4000       | Green    |

<sup>(1)</sup> For future products, contact the 3PEAK factory for more information and sample.

Green: 3PEAK defines "Green" to mean RoHS compatible and free of halogen substances.

www.3peak.com 22 / 24 EA20221101A0

### IMPORTANT NOTICE AND DISCLAIMER

Copyright<sup>©</sup> 3PEAK 2012-2023. All rights reserved.

**Trademarks.** Any of the 思瑞浦 or 3PEAK trade names, trademarks, graphic marks, and domain names contained in this document /material are the property of 3PEAK. You may NOT reproduce, modify, publish, transmit or distribute any Trademark without the prior written consent of 3PEAK.

**Performance Information.** Performance tests or performance range contained in this document/material are either results of design simulation or actual tests conducted under designated testing environment. Any variation in testing environment or simulation environment, including but not limited to testing method, testing process or testing temperature, may affect actual performance of the product.

**Disclaimer.** 3PEAK provides technical and reliability data (including data sheets), design resources (including reference designs), application or other design recommendations, networking tools, security information and other resources "As Is". 3PEAK makes no warranty as to the absence of defects, and makes no warranties of any kind, express or implied, including without limitation, implied warranties as to merchantability, fitness for a particular purpose or non-infringement of any third-party's intellectual property rights. Unless otherwise specified in writing, products supplied by 3PEAK are not designed to be used in any life-threatening scenarios, including critical medical applications, automotive safety-critical systems, aviation, aerospace, or any situations where failure could result in bodily harm, loss of life, or significant property damage. 3PEAK disclaims all liability for any such unauthorized use.

www.3peak.com 23 / 24 EA20221101A0

This page intentionally left blank

www.3peak.com 24 / 24 EA20221101A0