#### **Features**

- Single-Channel Isolated Gate Driver with CMOS/TTL-Compatible Input

- Automotive AEC-Q100 Grade 1 (TPM5350xQ)

- 5-A Source/5-A Sink Peak Output Current with Rail-to-Rail Output

- · Feature Options

- Split Outputs (TPM5350S, TPM5350SQ)

- Miller Clamp (TPM5350M, TPM5350MQ)

- Up to 40-V Output Driver Supply Voltage

- 8-V and 12-V V<sub>CC</sub> UVLO Options

- 3-V to 15-V Input Supply Voltage

- Negative 5-V Reverse Polarity Voltage Handling Capability on Input Stage

- · Ultra-Fast Output Driving

- 60-ns Propagation Delay

- 25-ns Delay Matching

- 35-ns Pulse Width Distortion

- 5-kV<sub>RMS</sub> Reinforced Isolation Rating

- ±100-kV/µs Common-Mode Transient Immunity (CMTI)

- Industrial Standard Wide-Body WSOP8 & SOP8 Packages

- Operating Ambient Temperature T<sub>A</sub>: −40°C to +125°C

- Safety-Related Certifications: (In progress)

- VDE Reinforced Insulation according to DIN VDE V 0884-11: 2017-01 (Planned)

- 5.7-kV<sub>RMS</sub> Isolation Rating per UL 1577 (Planned)

- CSA Certification per IEC 60950-1, IEC 62368-1, and IEC 60601-1 End Equipment Standards (Planned)

- TÜV Certification according to EN 60950-1 and EN 61010-1 (Planned)

- CQC Certification per GB4943.1-2011 (Planned)

### **Applications**

- Industrial Motor-Control Drives

- Industrial Power Supplies, UPS

- Solar Inverters

- Automotive On-board-charger, High Voltage DC/DC Converter

- Silicon Carbide (SiC) Driver

### **Description**

The TPM5350xQ driver is an automotive-grade single-channel isolated gate driver for IGBTs, MOSFETs, and SiC MOSFETs. Its input is CMOS/TTL compatible with the industrial standard wide-body WSOP8 and standard SOP8 packages. Its driving capability can support a 5-A source and 5-A sink current. The output stage can withstand high voltages up to 40 V and support the latest generation of IGBT and SiC-based applications.

The TPM5350xQ device provides high electromagnetic immunity and low emissions at low power consumption. Its isolation channel is separated by a double-capacitive silicon dioxide (SiO2) insulation barrier. 3PEAK proprietary galvanic isolation technology supports 150-kV/µs commonmode transient immunity (CMTI), which is critical especially for SiC applications. The TPM5350M device has integrated Miller Clamp to prevent false turn on by miller current. The TPM5350S has split outputs to adjust rising and falling slew rates without the needs of external diodes. Its enhanced reliability can support high-power industrial applications.

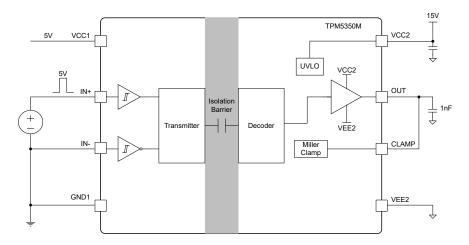

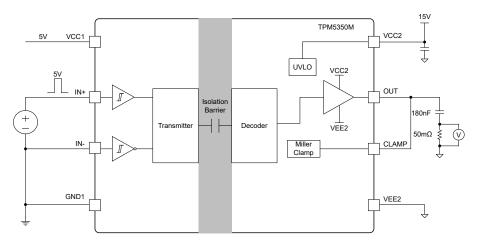

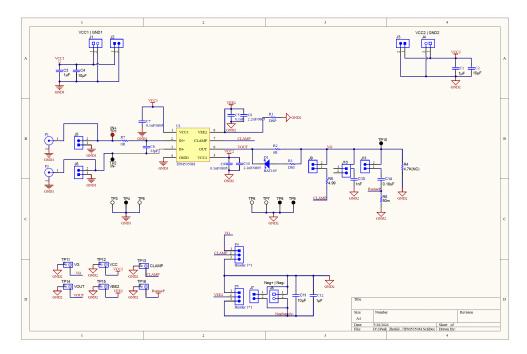

## **Typical Application Circuit**

## **Table of Contents**

| Features                                | 1  |

|-----------------------------------------|----|

| Applications                            |    |

| Description                             |    |

| Typical Application Circuit             | 1  |

| Product Family Table                    | 3  |

| Revision History                        | 3  |

| Pin Configuration and Functions         | 4  |

| Specifications                          | 5  |

| Absolute Maximum Ratings (1)            | 5  |

| ESD, Electrostatic Discharge Protection | 5  |

| Recommended Operating Conditions        | 5  |

| Safety Limiting Values                  | 6  |

| Insulation Specifications               | 7  |

| Electrical Characteristics              | 9  |

| Timing Characteristics                  | 11 |

| Parameter Measurement                   | 11 |

| Typical Performance Characteristics     | 14 |

| Detailed Description                    | 16 |

| Overview                                | 16 |

| Functional Block Diagram                | 16 |

| Feature Description                     | 17 |

| Application and Implementation          | 21 |

| Typical Application                     | 21 |

| Layout                                  | 22 |

| Layout Guideline                        | 22 |

| Layout Recommendations                  | 22 |

| Tape and Reel Information               | 23 |

| Package Outline Dimensions              | 25 |

| WSOP8-A                                 | 25 |

| Order Information                       | 26 |

| IMPORTANT NOTICE AND DISCLAIMER         | 27 |

# **Product Family Table**

| Order Number                         | UVLO Threshold (V) | Feature       | Package | Quality Grade |

|--------------------------------------|--------------------|---------------|---------|---------------|

| TPM5350MQ-SOAR-S                     | 12.5               | Miller Clamp  | WSOP8   | Automotive    |

| TPM5350BMQ-SOAR-S (1)                | 8.5                | Miller Clamp  | WSOP8   | Automotive    |

| TPM5350MQ-SO1R-S                     | 12.5               | Miller Clamp  | SOP8    | Automotive    |

| TPM5350SQ-SOAR-S                     | 12.5               | Split Outputs | WSOP8   | Automotive    |

| TPM5350BSQ-SOAR-<br>S <sup>(1)</sup> | 8.5                | Split Outputs | WSOP8   | Automotive    |

| TPM5350SQ-SO1R-S                     | 12.5               | Split Outputs | SOP8    | Automotive    |

| TPM5350M-SOAR                        | 12.5               | Miller Clamp  | WSOP8   | Industrial    |

| TPM5350S-SOAR (1)                    | 12.5               | Split Outputs | WSOP8   | Industrial    |

| TPM5350BS-SOAR (1)                   | 8.5                | Split Outputs | WSOP8   | Industrial    |

<sup>(1)</sup> Contact sales representatives for more details.

## **Revision History**

| Date       | Revision | Notes           |

|------------|----------|-----------------|

| 2024-05-15 | Rev A.0  | Initial release |

www.3peak.com 3 / 28 EA20230502A0

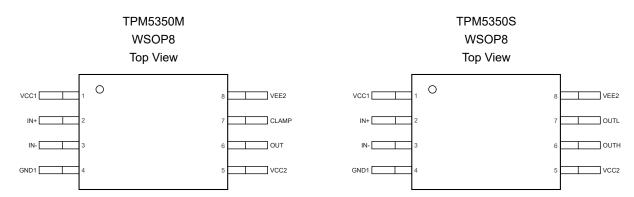

## **Pin Configuration and Functions**

Table 1. Pin Functions: TPM5350M

| Р   | in   | 1/0 | December 1997                                                                                            |  |

|-----|------|-----|----------------------------------------------------------------------------------------------------------|--|

| No. | Name | I/O | Description                                                                                              |  |

| 1   | VCC1 | Р   | Input side power supply. Connect a 0.1-uF capacitor to GND and place it close to the device.             |  |

| 2   | IN+  | I   | Non-inverting input. Internally pulled low if left open.                                                 |  |

| 3   | IN-  | I   | Inverting input. Internally pulled high if left open.                                                    |  |

| 4   | GND1 | G   | Input side power ground                                                                                  |  |

| 5   | VCC2 | Р   | Output side power rail. Connect a capacitor close to the device to the support transient output current. |  |

| 6   | OUTH | 0   | Gate driver pull-up output.                                                                              |  |

| 7   | OUTL | 0   | Gate driver pull-down output.                                                                            |  |

| 8   | VEE2 | G   | Output side ground.                                                                                      |  |

www.3peak.com 4 / 28 EA20230502A0

## **Specifications**

### Absolute Maximum Ratings (1)

|                   | Parameter                                                              | Min      | Max        | Unit |

|-------------------|------------------------------------------------------------------------|----------|------------|------|

| Input             | Input Supply Voltage, VCC1 - GND1                                      | -0.3     | 18         | V    |

| Voltage           | Input Signal Voltage, V <sub>IN+</sub> - GND1, V <sub>IN-</sub> - GND1 | -5       | VCC1 + 0.3 | V    |

| 0                 | Output Supply Voltage, VCC2 - VEE2                                     | -0.3     | 40         | V    |

| Output<br>Voltage | Output Side Voltage with reference to VEE2, VOUTH, VOUTL, VOUT, VCLAMP | VEE2-0.3 | VCC2 + 0.3 | V    |

| $T_J$             | Maximum Junction Temperature                                           | -40      | 150        | °C   |

| T <sub>A</sub>    | Operating Ambient Temperature Range                                    | -40      | 125        | °C   |

| T <sub>STG</sub>  | Storage Temperature Range                                              | -65      | 150        | °C   |

| TL                | Lead Temperature (Soldering, 10 sec)                                   |          | 260        | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

#### **ESD, Electrostatic Discharge Protection**

Table 2. TPM5350M

|     | Parameter                | Condition                  | Minimum Level | Unit |

|-----|--------------------------|----------------------------|---------------|------|

| НВМ | Human Body Model ESD     | ANSI/ESDA/JEDEC JS-001 (1) | ±4            | kV   |

| CDM | Charged Device Model ESD | ANSI/ESDA/JEDEC JS-002 (2) | ±1.5          | kV   |

Table 3. TPM5350S

|     | Parameter                | Condition                  | Minimum Level | Unit |

|-----|--------------------------|----------------------------|---------------|------|

| НВМ | Human Body Model ESD     | ANSI/ESDA/JEDEC JS-001 (1) | ±2            | kV   |

| CDM | Charged Device Model ESD | ANSI/ESDA/JEDEC JS-002 (2) | ±1.5          | kV   |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## **Recommended Operating Conditions**

|                | Parameter                                                           |     | Max | Unit |

|----------------|---------------------------------------------------------------------|-----|-----|------|

| VCC1           | Input Supply Voltage, reference to GND1                             | 3   | 18  | V    |

| VCC2           | Output Supply Voltage, reference to VEE2, 12V UVLO option, TPM5350x | 13  | 36  | V    |

| VCC2           | Output Supply Voltage, reference to VEE2, 8V UVLO option TPM5350Bx  | 9.5 | 36  | V    |

| TJ             | Junction Temperature                                                | -40 | 150 | °C   |

| T <sub>A</sub> | Operating Ambient Temperature                                       | -40 | 125 | °C   |

www.3peak.com 5 / 28 EA20230502A0

<sup>(2)</sup> This data was taken with the JEDEC low effective thermal conductivity test board.

<sup>(3)</sup> This data was taken with the JEDEC standard multilayer test boards.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

(1) Contact 3PEAK representatives for more information.

## **Safety Limiting Values**

|                 | Parameter                                     | Test Conditions                                                                                                | Min | Тур | Max  | Unit |

|-----------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| P <sub>D</sub>  | Maximum power dissipation on input and output | $V_{CC1}$ = 15 V, $V_{CC2}$ = 15 V, f = 2.1-MHz, 50% duty cycle, square wave, 2.2-nF load                      |     |     | 1.2  | W    |

| P <sub>D1</sub> | Maximum input power dissipation               | V <sub>CC1</sub> = 15 V, V <sub>CC2</sub> = 15 V, f = 2.1-<br>MHz, 50% duty cycle, square wave,<br>2.2-nF load |     |     | 50   | mW   |

| P <sub>D2</sub> | Maximum output power dissipation              | $V_{CC1}$ = 15 V, $V_{CC2}$ = 15 V, f = 2.1-MHz, 50% duty cycle, square wave, 2.2-nF load                      |     |     | 1.05 | W    |

www.3peak.com 6 / 28 EA20230502A0

## **Insulation Specifications**

|                   | Parameter                              | Conditions                                                                                                                                                                                                               | Value              | Unit            |

|-------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------|

| CLR               | External Clearance                     | Shortest terminal-to-terminal distance through air                                                                                                                                                                       | > 8.5              | mm              |

| CPG               | External Creepage                      | Shortest terminal-to-terminal distance across the package surface                                                                                                                                                        | > 8.5              | mm              |

| DTI               | Distance through the Insulation        | Minimum internal gap (internal clearance)                                                                                                                                                                                | > 21               | μm              |

| СТІ               | Comparative Tracking Index             |                                                                                                                                                                                                                          | > 600              | V               |

|                   | Material Group                         |                                                                                                                                                                                                                          | 1                  |                 |

|                   | Overvoltage Category per IEC 60664-1   | For Rated Mains Voltage ≤ 600 V <sub>RMS</sub>                                                                                                                                                                           | I-III              |                 |

|                   | Overvoltage dategory per 120 00004-1   | For Rated Mains Voltage ≤ 1000 V <sub>RMS</sub>                                                                                                                                                                          | 1-11               |                 |

|                   | Pollution Degree                       |                                                                                                                                                                                                                          | 2                  |                 |

|                   | Climate Category                       |                                                                                                                                                                                                                          | 40/125/21          |                 |

| C <sub>IO</sub>   | Isolation Capacitance                  | $V_{IO}$ = 0.4 × sin (2 $\pi$ ft), f = 1 MHz                                                                                                                                                                             | 1.2                | pF              |

|                   |                                        | V <sub>IO</sub> = 500 V, T <sub>A</sub> = 25 °C                                                                                                                                                                          | > 10 <sup>12</sup> |                 |

| R <sub>IO</sub>   | Isolation Resistance                   | V <sub>IO</sub> = 500 V, 100°C ≤ T <sub>A</sub> ≤ 125 °C                                                                                                                                                                 | > 10 <sup>11</sup> | Ω               |

|                   |                                        | V <sub>IO</sub> = 500 V, T <sub>A</sub> = 150 °C                                                                                                                                                                         | > 10 <sup>9</sup>  |                 |

| $V_{\text{IORM}}$ | Maximum Repetitive Isolation Voltage   | AC voltage (bipolar)                                                                                                                                                                                                     | 1500               | $V_{PK}$        |

| .,                | Manifestory Manifestory Landau Vallage | AC voltage; TDDB Test                                                                                                                                                                                                    | 1060               | $V_{RMS}$       |

| $V_{\text{IOWM}}$ | Maximum Working Isolation Voltage      | DC voltage                                                                                                                                                                                                               | 1500               | V <sub>DC</sub> |

| V <sub>ІОТМ</sub> | Maximum Transient Isolation Voltage    | $V_{TEST} = V_{IOTM}$ , t = 60 s (qualification);<br>$V_{TEST} = 1.2 \text{ x } V_{IOTM}$ , t = 1 s (100% production)                                                                                                    | 8000               | $V_{PK}$        |

| Viosm             | Maximum Surge Isolation Voltage        | Test method per IEC 62368-1,<br>1.2/50 µs waveform, V <sub>TEST</sub> = 1.3 ×<br>V <sub>IOSM</sub> (qualification) = 11700v                                                                                              | 9000               | $V_{PK}$        |

| V <sub>ISO</sub>  | UL 1577 Withstand Isolation Voltage    | $\begin{split} V_{TEST} = V_{ISO} = 5700 \ V_{RMS}, \ t = 60 \ s \ (in \\ qualification), \ V_{TEST} = 1.2 \times V_{ISO} - 6840 \\ V_{RMS} \ , \ \ t = 1 \ s \ (100\% \ in \ production) \end{split}$                   | 5700               | $V_{RMS}$       |

|                   |                                        | Method a, After Input/Output safety test subgroup 2/3, V <sub>ini</sub> = V <sub>IOTM</sub> , t <sub>ini</sub> = 60 s; V <sub>pd(m)</sub> = 1.2 × V <sub>IORM</sub> , t <sub>m</sub> = 10 s                              | ≤ 5                |                 |

| $q_{pd}$          | Apparent Charge                        | Method a, After environmental tests subgroup 1, $V_{ini} = V_{IOTM}$ , $t_{ini} = 60$ s; $V_{pd(m)} = 1.6 \times V_{IORM}$ , $t_m = 10$ s                                                                                | ≤ 5                | рС              |

|                   |                                        | Method b1; At routine test (100% production) and preconditioning (type test), V <sub>ini</sub> = 1.2 x V <sub>IOTM</sub> , t <sub>ini</sub> = 1 s; V <sub>pd(m)</sub> = 1.875 × V <sub>IORM</sub> , t <sub>m</sub> = 1 s | ≤ 5                |                 |

www.3peak.com 7 / 28 EA20230502A0

(1) All pins on each side of the barrier tied together create a two-terminal device.

www.3peak.com 8 / 28 EA20230502A0

#### **Electrical Characteristics**

All test conditions: VCC1 – GND1 = 3.3 V or 5 V, VCC2 - VEE2 = 15 V,  $V_{EE2}$  referred as GND,  $T_A$  = -40°C to 125°C, Output capacitance  $C_L$  = 100 pF, unless otherwise noted.

|                       | Parameter                                      | Conditions              | Min  | Тур  | Max  | Unit |

|-----------------------|------------------------------------------------|-------------------------|------|------|------|------|

| Supply                |                                                |                         | ·    |      |      | •    |

| Ivcc1                 | Input Supply Quiescent Current                 | f = 500 kHz, Duty = 50% | 1.6  | 2.1  | 2.5  | mA   |

|                       | Output Supply Quiescent                        | VCC2 - GND2 = 15V       | 0.9  | 1.56 | 2.3  |      |

| I <sub>VCC2</sub>     | Current                                        | VCC2 - GND2 = 36V       |      | 1.73 |      | mA   |

| Vuvlor1               | Undervoltage Lock out, VCC1,<br>Rising edge    |                         |      | 2.72 | 2.85 | V    |

| V <sub>UVLOF1</sub>   | Undervoltage Lock out, VCC1, Falling edge      |                         | 2.4  | 2.58 |      | V    |

| V <sub>UVLOHYS1</sub> | Undervoltage Lock out, VCC1,<br>Hysteresis     |                         |      | 0.14 |      | V    |

| Cin                   | Input Parasitic Capacitance                    | f = 0.5 MHz             |      | 15   |      | pF   |

| Under Volta           | ge Lockout, TPM5350 (12-V UVLO V               | /ersion)                |      |      |      |      |

| $V_{\text{UVLO}_{R}}$ | Under Voltage Lock-out Threshold, Rising Edge  |                         | 10.8 | 12.5 | 13.5 | V    |

| Vuvlo_f               | Under Voltage Lock-out Threshold, Falling Edge |                         | 10   | 11.5 | 12.6 | V    |

| V <sub>UVLO_HYS</sub> | UVLO Hysteresis                                |                         | 0.7  | 1    | 1.2  | V    |

| Under Voltag          | ge Lockout, TPM5350B (8-V UVLO \               | Version)                | ,    |      |      |      |

| V <sub>UVLO_F</sub>   | Under Voltage Lock-out Threshold, Falling Edge |                         |      | 8.7  |      | V    |

| V <sub>UVLO_F</sub>   | Under Voltage Lock-out Threshold, Falling Edge |                         |      | 8    |      | V    |

| V <sub>UVLO_HYS</sub> | UVLO Hysteresis                                |                         |      | 0.7  |      | V    |

| LOGIC I/O             |                                                |                         |      |      |      |      |

| V <sub>IT+(IN)</sub>  | Input Threshold, rising edge, IN+, IN-         |                         | 1.6  | 1.7  | 1.9  | V    |

| V <sub>IT-(IN)</sub>  | Input Threshold, falling edge, IN+, IN-        |                         | 1.1  | 1.24 | 1.4  | V    |

| V <sub>HYS(IN)</sub>  | Input Threshold Hysteresis, IN+, IN-           |                         | 0.3  | 0.46 | 0.65 | V    |

| I <sub>IH</sub>       | Input Leakage Current                          | IN+ = VCC1              |      | 10   | 100  | μA   |

|                       | Immust I paleage O                             | IN- = GND1              | -240 | -40  |      | μA   |

| I <sub>IL</sub>       | Input Leakage Current                          | IN- = GND1 - 5V         | -310 | -80  |      | μA   |

| Gate Driver           | Stage                                          |                         |      |      |      |      |

www.3peak.com 9 / 28 EA20230502A0

|                                     | Parameter                                              | Conditions                                                                                             | Min | Тур | Max | Unit |

|-------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| V <sub>OH</sub>                     | High-Level Output Voltage(VCC2 - OUT) and(VCC2 - OUTH) | I <sub>OUT</sub> = –20 mA                                                                              | 70  | 180 | 360 | mV   |

| V <sub>OL</sub>                     | Low-Level Output Voltage (OUT and OUTL)                | IN+ = low, IN- = high; I <sub>O</sub> = 20 mA                                                          |     | 12  | 25  | mV   |

| I <sub>OH</sub> <sup>(1)</sup>      | Peak Source Current                                    | IN+ = high, IN- = low                                                                                  |     | 5   |     | Α    |

| I <sub>OL</sub> <sup>(1)</sup>      | Peak Sink Current                                      | IN+ = high, IN- = low                                                                                  |     | 5   |     | Α    |

| V <sub>CLAMP</sub>                  | Clamp Low-level Current                                | I <sub>CLAMP</sub> = 20 mA                                                                             |     | 26  | 50  | mV   |

| ICLAMP <sup>(1)</sup>               | Clamp Low-level Current for Low-output Voltage         | V <sub>CLAMP</sub> = V <sub>EE2</sub> + 2 V                                                            |     | 1.2 |     | А    |

| V <sub>CLAMPTH</sub>                | Clamp Threshold Voltage                                |                                                                                                        |     | 2.1 | 2.3 | V    |

| V <sub>CLP_OUT</sub> (1)            | Clamping Voltage VOUTH - VCC2 to VOUT - VCC2           | IN+ = HIGH, IN- = LOW,<br>$t_{CLAMP}$ = 10 $\mu$ s, $l_{OUTH}/l_{OUT}$ = 500<br>mA                     |     | 1   |     | V    |

| V <sub>CLP_OUT</sub> <sup>(1)</sup> | Clamping Voltage VEE2 –<br>VOUTL or VEE2 – VCLAMP or   | IN+ = HIGH, IN- = LOW,<br>t <sub>CLAMP</sub> = 10 µs, l <sub>OUTH</sub> /l <sub>OUT</sub> =<br>-500 mA |     | 1.5 |     | V    |

| _                                   | VEE2 - VOUT                                            | IN+ = LOW, IN- = HIGH,<br>I <sub>CLAMP</sub> or I <sub>OUTL</sub> = -20 mA                             |     | 0.9 |     | V    |

| Active Pulldov                      | Active Pulldown                                        |                                                                                                        |     |     |     |      |

| V <sub>OUTSD</sub>                  | Active Pulldown Voltage on OUTL, CLAMP, and OUT        | I <sub>OUTL</sub> or I <sub>OUT</sub> = 750 mA, VCC2<br>= OPEN                                         | 2   |     | 2.5 | V    |

<sup>(1)</sup> Guranteed by design

www.3peak.com 10 / 28 EA20230502A0

## **Timing Characteristics**

|                        | Parameter                                                                      | Test Conditions                                                                                   | Min | Тур  | Max | Unit  |

|------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| t <sub>r</sub>         | Output Rise Time (1)                                                           |                                                                                                   |     | 16   |     | ns    |

| t <sub>f</sub>         | Output Fall Time <sup>(1)</sup>                                                | - 00 III (500) D ( 0 I )                                                                          |     | 9.2  |     | ns    |

| t <sub>PLH</sub>       | Propagation Delay, Low to High                                                 | F <sub>SW</sub> = 20 kHz, (50% Duty Cycle)<br>V <sub>CC</sub> = 15 V , C <sub>LOAD</sub> = 100 pF |     | 39   | 65  | ns    |

| t <sub>PHL</sub>       | Propagation Delay, High to Low                                                 | VCC = 10 V , OLOAD = 100 pi                                                                       |     | 39   | 65  | ns    |

| t <sub>PWD</sub>       | Pulse Width Distortion  t <sub>PHL</sub> -t <sub>PLH</sub>                     |                                                                                                   | 0   | 1.4  | 20  | ns    |

| t <sub>sk(pp)</sub>    | Part-to-Part Skew in Propagation<br>Delay between any Two Parts <sup>(2)</sup> | F <sub>SW</sub> = 20 kHz, (50% Duty Cycle)<br>V <sub>CC</sub> = 15 V, I <sub>F</sub> = 10 mA      |     |      | 25  | ns    |

| V <sub>CC1UVLO_r</sub> | UVLO Recovery Delay, VCC1                                                      |                                                                                                   | 15  | 24.5 | 40  | μs    |

| tvcc2UVLO_r            | UVLO Recovery Delay, VCC2                                                      |                                                                                                   | 15  | 27.5 | 45  | μs    |

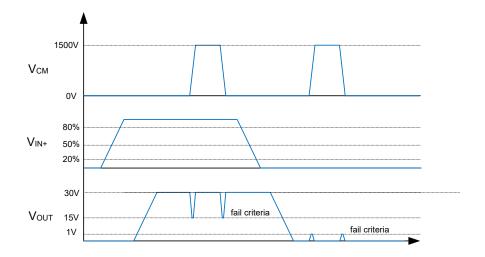

| СМТІ                   | Common-Mode Transient<br>Immunity <sup>(1)</sup>                               | PWM is tied to GND or V <sub>CC1</sub> ,<br>V <sub>CM</sub> = 1200 V                              | 100 | 150  |     | kV/μs |

<sup>(1)</sup> Guaranteed by design.

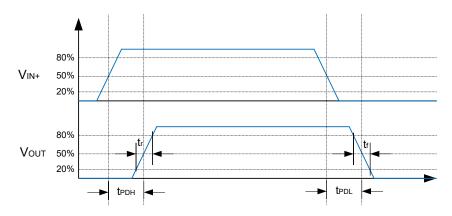

#### **Parameter Measurement**

#### **Driver Parameter**

#### **Driver Timing Diagram**

www.3peak.com 11 / 28 EA20230502A0

<sup>(2)</sup>  $t_{\rm sk(pp)}$  is the magnitude of the difference in propagation delay times between the output of different devices switching in the same direction while operating at identical supply voltages, temperature, input signals, and loads guaranteed by characterization

#### **Output Current Measurement**

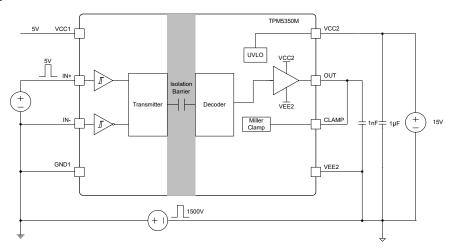

#### **CMTI Test Circuit**

#### **CMTI Test Criteria**

www.3peak.com 12 / 28 EA20230502A0

www.3peak.com 13 / 28 EA20230502A0

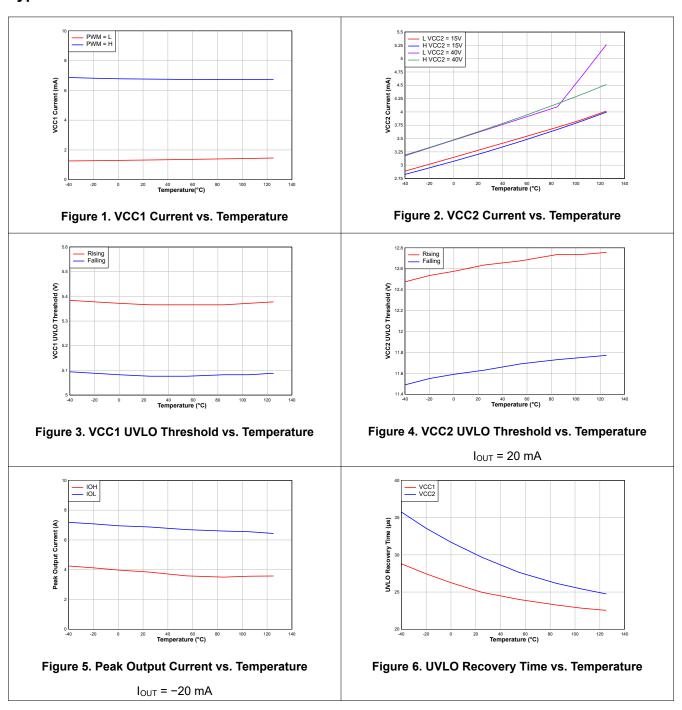

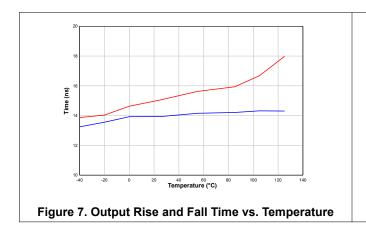

## **Typical Performance Characteristics**

www.3peak.com 14 / 28 EA20230502A0

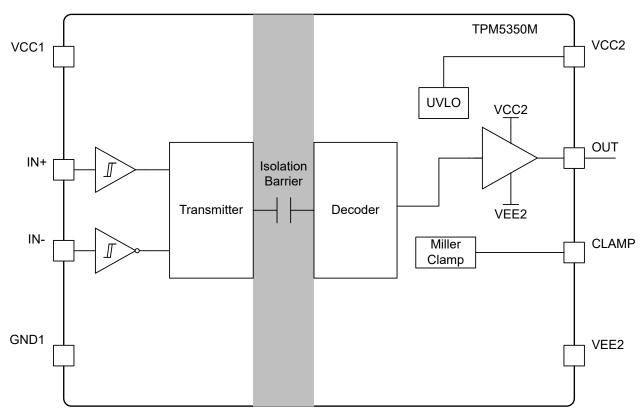

Figure 8. Output Propagation Delay vs. Temperature

www.3peak.com 15 / 28 EA20230502A0

## **Detailed Description**

#### Overview

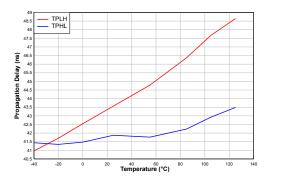

The TPM5350xQ is a single-channel isolated gate driver for MOSFETs, IGBTs, and SiC FETs with TTL/CMOS input stage. It has a 40-V maximum operating driver voltage, which is especially suitable for high-power fast-transient IGBT / SiC applications.

The TPM5350xQ is designed to replace the optocoupler gate driver with an industry-standard wide-body 8-pin package of WSOP8, with more than 8.5-mm creepage and clearance to withstand over 1060- $V_{RMS}$  working voltage, reinforced isolation, and 5.7 k $V_{RMS}$  for the 60 s and a surge rating of 8-k  $V_{PK}$ . 3PEAK proprietary isolation technology supports common-mode transient immunity of greater than 150 k $V_{LMS}$ .

The TPM5350x offers two variations: split output and Miller clamp (refer to the Device Comparison Table). Isolation in the TPM5350 is achieved using high-voltage SiO2-based capacitors with 3PEAK proprietary on-off keying (OOK) modulation scheme. The TPM5350 incorporates advanced circuit techniques to optimize CMTI performance and minimize radiated emissions resulting from high-frequency carrier and IO buffer switching.

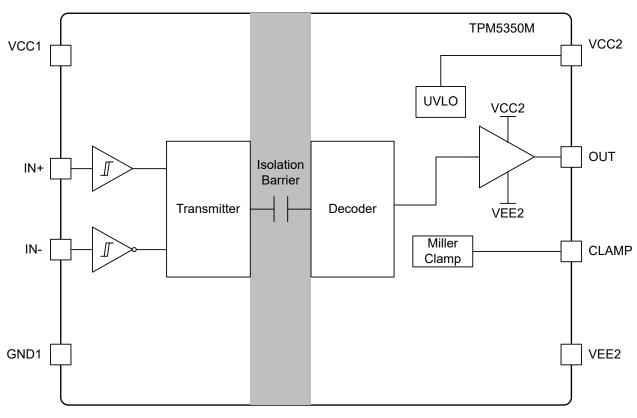

#### **Functional Block Diagram**

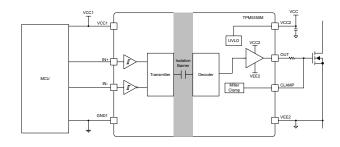

Figure 9. TPM5350M Functional Block Diagram

www.3peak.com 16 / 28 EA20230502A0

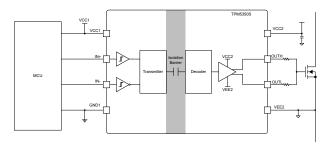

Figure 10. TPM5350S Functional Block Diagram

#### **Feature Description**

#### **Power Supply**

The VCC1 input power supply of the TPM5350 supports a wide voltage range from 3 V to 15 V, while the VCC2 output supply accommodates a voltage range from 9.5 V to 33 V.

When operating with bipolar supplies, the power device is turned off by applying a negative voltage on the gate relative to the emitter or source. This configuration prevents unintentional activation of the power device due to current induced by the Miller effect. In the case of modern SiC MOSFETs, the typical values are 15 V and -3 V. When operating with a unipolar supply, the VCC2 supply is connected to 15 V for SiC MOSFETs. The VEE2 supply is connected to 0 V.

In both scenarios, the TPM5350M device with Miller clamping function can be utilized. The Miller clamping function is implemented by establishing a low-impedance path between the gate of the power device and the VEE2 supply. This allows the Miller current to sink through the clamp pin, thereby ensuring that the gate voltage remains below the turn-on threshold value.

#### **Input Stage**

The input pins (IN+ and IN-) of the TPM5350 family employ CMOS-compatible input-threshold logic, ensuring complete isolation from the VCC2 supply voltage. These pins are designed to be easily driven by logic-level control signals, such as those from 3.3-V microcontrollers. The TPM5350 family typically operates with a high threshold (VIT+(IN)) of 0.55 × VCC1 and a low threshold of 0.45 × VCC1, offering reliable signal compatibility. With a wide hysteresis (Vhys(IN)) of 0.1 × VCC1, the devices exhibit excellent noise immunity and stable performance.

www.3peak.com 17 / 28 EA20230502A0

In the event that any of the inputs are left unconnected, an internal pulldown resistance of 128 k $\Omega$  ensures that the IN+ pin is pulled low, while internal resistance of 128 k $\Omega$  pulls the IN- pin high. 3PEAK recommends, for enhanced noise immunity, to ground any unused input or connecting it to the VCC1 voltage.

A notable advantage of the TPM5350 family is the isolation between the input and output drivers. As a result, the input signal amplitude can be either larger or smaller than VCC2, as long as it remains within the recommended limits. This feature provides flexibility when integrating the gate driver with various control signal sources and allows the user to choose the most suitable VCC2 voltage for a specific gate. However, it is crucial to ensure that the amplitude of any signal applied to IN+ or IN- never exceeds the voltage of VCC1.

#### **Decoder & Output Stage**

The high-frequency signal is converted by the decoder via double-capacitive insulation barrier as the output stage's input. The rail-to-rail output stage provides a high-peak current during the output slewing. The output  $V_{CC}$  supports a maximum of 40-V input.

The output stages of the TPM5350 family are designed with a pull-up structure that optimizes the delivery of peak-source current when it is most needed, specifically during the Miller plateau region of the power-switch turn-on transition. This occurs when the power-switch drain or collector voltage experiences a dV/dt change. The pull-up structure consists of a P-channel MOSFET and an additional N-channel MOSFET connected in parallel.

The N-channel MOSFET plays a crucial role in enhancing the peak-sourcing current for fast turn-on. During the narrow instant when the output is transitioning from a low to a high state, the N-channel MOSFET is briefly turned on, providing a boost to the current. This enables a faster turn-on operation. To provide further insight, the table below provides typical internal resistance values for both the pullup and pulldown structures of the TPM5350, illustrating their characteristics and performance.

| Device    | Grade      | R <sub>NMOS</sub> | R <sub>OH</sub> | R <sub>OL</sub> | RCLAMP | Unit |

|-----------|------------|-------------------|-----------------|-----------------|--------|------|

| TPM5350M  | Industrial | 1.54              | 12              | 0.35            | 1      | Ω    |

| TPM5350MQ | Automotive | 1.54              | 12              | 0.35            | 1      | Ω    |

| TPM5350S  | Industrial | 1.54              | 12              | 0.35            | n/a    | Ω    |

| TPM5350SQ | Automotive | 1.54              | 12              | 0.35            | n/a    | Ω    |

In the TPM5350S version, the pulldown structure consists solely of an N-channel MOSFET. However, in the M version, an additional FET is connected in parallel with the pulldown structure when the CLAMP and OUT pins are linked to the gate of the IGBT or MOSFET. This configuration allows for rail-to-rail operation, providing an output voltage swing between VCC2 and VEE2.

#### **Protection**

#### **Under-Voltage Lock Out (UVLO)**

The TPM5350 family incorporates UVLO (Undervoltage Lockout) functions for both the VCC1 and VCC2 supplies to safeguard IGBTs and MOSFETs from underdriven conditions. These functions monitor the voltages between the VCC1 and GND1, as well as VCC2 and VEE2 pins.

During device start-up or if the VCC voltage falls below the VIT+ (UVLO) threshold or drops below the VIT- (UVLO) threshold after start-up, the UVLO feature activates, holding the affected output low, regardless of the input pins (IN+ and IN-). This ensures that the power devices are not operated under insufficient voltage conditions.

The VCC UVLO protection incorporates a hysteresis feature (Vhys(UVLO)). This hysteresis prevents rapid toggling or instability caused by ground noise in the power supply. It allows the device to tolerate small drops in bias voltage that may occur when the device starts switching and experiences a sudden increase in operating current consumption.

By implementing UVLO functions with hysteresis, the TPM5350 family ensures reliable operation and effectively safeguards IGBTs and MOSFETs against underdriven conditions, thereby enhancing the overall performance and protection of the system.

www.3peak.com 18 / 28 EA20230502A0

Table 4. VCC1 UVLO Logic

| CONDITIONS   | INP | UTS | OUTPUTS |           |  |

|--------------|-----|-----|---------|-----------|--|

| CONDITIONS   | IN+ | IN- | OUTH    | OUT, OUTL |  |

|              | Н   | L   | HiZ     | L         |  |

| V004 I N/I 0 | L   | Н   | HiZ     | L         |  |

| VCC1 UVLO    | Н   | Н   | HiZ     | L         |  |

|              | L   | L   | HiZ     | L         |  |

Table 5. VCC2 UVLO Logic

| CONDITIONS         | INP | UTS    | OUTPUTS |           |  |

|--------------------|-----|--------|---------|-----------|--|

| CONDITIONS         | IN+ | N+ IN- |         | OUT, OUTL |  |

|                    | Н   | L      | HiZ     | L         |  |

| \/OO0       \/   O | L   | Н      | HiZ     | L         |  |

| VCC2 UVLO          | Н   | Н      | HiZ     | L         |  |

|                    | L   | L      | HiZ     | L         |  |

#### **Active Pulldown**

The TPM5350 family incorporates an active pulldown function to ensure that the IGBT or MOSFET gate remains in a low state when no power is connected to the VCC2 supply. This feature is designed to prevent false turn-on of the IGBT or MOSFET on the OUT, OUTL, and CLAMP pins by clamping the output voltage to approximately 2 V.

When the output stages of the driver are unbiased or in a UVLO (Undervoltage Lockout) condition, an active clamp circuit is engaged to limit the voltage rise on the driver outputs. In this state, the upper PMOS (P-channel MOSFET) is held off by a pull-up resistor, while the gate of the lower NMOS (N-channel MOSFET) is connected to the driver output through a 500-k $\Omega$  resistor. This configuration effectively clamps the output voltage to the threshold voltage of the lower NMOS device, which is approximately 1.5 V when no bias power is available.

By utilizing the active pulldown and clamp circuitry, the TPM5350 ensures that the driver outputs are held low and prevents unintended turn-on of the IGBT or MOSFET under unbiased or UVLO conditions. This feature adds an extra layer of protection and ensures the reliable operation of the overall system.

#### **Short Circuit Clamping**

The TPM5350 family incorporates a short-circuit clamping function to protect the IGBT or MOSFET gate from overvoltage breakdown or degradation during short-circuit conditions. This function works by clamping the voltages at the driver output and slightly raising the voltage of the active Miller clamp pins above the VCC2 voltage.

To implement the short-circuit clamping function, a diode connection is added between the dedicated pins and the VCC2 pin within the driver. These internal diodes are capable of conducting up to 500 mA of current for a duration of 10 μs, and they can handle a continuous current of 20 mA. If higher current conduction capability is required, external Schottky diodes can be used to enhance the performance.

By employing the short-circuit clamping function, the TPM5350 provides an additional layer of protection by limiting voltage spikes and current surges during short-circuit events. This helps safeguard the IGBT or MOSFET gate, ensuring its long-term reliability and preventing potential damage from overvoltage conditions.

#### **Active Miller Clamp**

The TPM5350 family incorporates an active Miller-clamp function to mitigate false turn-on of the power switches that may be caused by Miller current in applications utilizing a unipolar power supply. This function is designed to address the specific challenges associated with the use of a unipolar power supply.

www.3peak.com 19 / 28 EA20230502A0

The active Miller-clamp function is achieved by introducing a low impedance path between the gate terminal of the power switch and ground (VEE2) to effectively sink the Miller current. By providing this clamp, the gate voltage of the power switch is limited to less than 2 V during the off state, preventing unintended turn-on.

By implementing the active Miller-clamp function, the TPM5350 family ensures reliable operation by suppressing the effects of Miller current and preventing false turn-on of the power switches. This feature is particularly beneficial in applications utilizing a unipolar power supply, enhancing the overall performance and robustness of the system.

#### **Function Table**

Table 6. Function Tables for TPM5350S

| INP | UTS | OUTPUTS |           |  |  |

|-----|-----|---------|-----------|--|--|

| IN+ | IN- | OUTH    | OUT, OUTL |  |  |

| Н   | L   | Н       | HiZ       |  |  |

| L   | Н   | HiZ     | L         |  |  |

| Н   | Н   | HiZ     | L         |  |  |

| L   | L   | HiZ     | L         |  |  |

Table 7. Function Tables for TPM5350M

| INP | UTS | OUTPUTS |          |  |

|-----|-----|---------|----------|--|

| IN+ | IN- | OUT     | CLAMP    |  |

| Н   | L   | Н       | Inactive |  |

| L   | Н   | Low     | Active   |  |

| Н   | Н   | Low     | Active   |  |

| L   | L   | Low     | Active   |  |

www.3peak.com 20 / 28 EA20230502A0

## **Application and Implementation**

#### Note

Information in the following application sections is not part of the 3PEAK's component specification and 3PEAK does not warrant its accuracy or completeness. 3PEAK's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### **Typical Application**

www.3peak.com 21 / 28 EA20230502A0

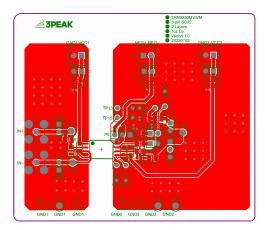

## Layout

#### **Layout Guideline**

- For voltage mode input drivers, a low ESR and ESL capacitor should be placed close to the VCC and VEE pins, and the loop from VCC to VEE should be made small.

- To minimize the inductance of the drive circuit loop, the driver should be placed closely to the transistor.

- The Miller clamp trace should be directly connected to the transistor's gate, and the trace should be kept short.

- To ensure isolation between the primary and secondary sides, avoid placing any PCB traces or copper directly below the driver device. A PCB cutout or groove is recommended to increase the creepage distance.

- To enhance thermal performance, it is recommended to enlarge the PCB copper connected to VCC and VEE.

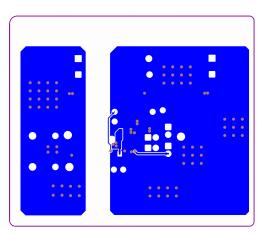

#### **Layout Recommendations**

**Top Layer**

**Bottom Layer**

www.3peak.com 22 / 28 EA20230502A0

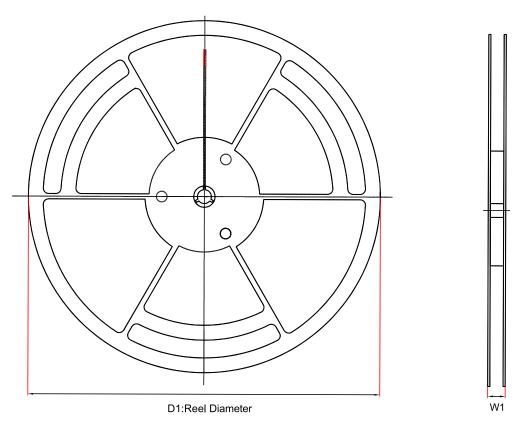

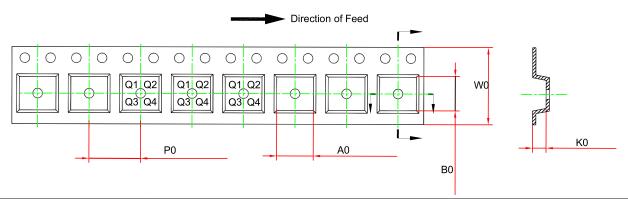

## **Tape and Reel Information**

| Order Number          | Package | D1 ( mm ) | W1<br>( mm ) | A0<br>( mm ) | B0<br>( mm ) | K0<br>( mm ) | P0<br>( mm ) | W0<br>( mm ) | Pin1<br>Quadrant |

|-----------------------|---------|-----------|--------------|--------------|--------------|--------------|--------------|--------------|------------------|

| TPM5350MQ-<br>SOAR-S  | WSOP8   | 330       | 21.6         | 11.95        | 6.2          | 3.1          | 16           | 16           | Q1               |

| TPM5350BMQ-<br>SOAR-S | WSOP8   | 330       | 21.6         | 11.95        | 6.2          | 3.1          | 16           | 16           | Q1               |

| TPM5350M-<br>SOAR     | WSOP8   | 330       | 21.6         | 11.95        | 6.2          | 3.1          | 16           | 16           | Q1               |

# **TPM5350x, TPM5350xQ**

# 5-A / 5-A, Single-Channel Isolated Gate Driver with Miller Clamp, Split Gate

| Order Number          | Package | D1<br>( mm ) | W1<br>( mm ) | A0<br>( mm ) | B0<br>( mm ) | K0<br>( mm ) | P0<br>( mm ) | W0<br>( mm ) | Pin1<br>Quadrant |

|-----------------------|---------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|------------------|

| TPM5350SQ-<br>SOAR-S  | WSOP8   | 330          | 21.6         | 11.95        | 6.2          | 3.1          | 16           | 16           | Q1               |

| TPM5350S-<br>SOAR     | WSOP8   | 330          | 21.6         | 11.95        | 6.2          | 3.1          | 16           | 16           | Q1               |

| TPM5350BSQ-<br>SOAR-S | WSOP8   | 330          | 21.6         | 11.95        | 6.2          | 3.1          | 16           | 16           | Q1               |

| TPM5350BS-<br>SOAR    | WSOP8   | 330          | 21.6         | 11.95        | 6.2          | 3.1          | 16           | 16           | Q1               |

www.3peak.com 24 / 28 EA20230502A0

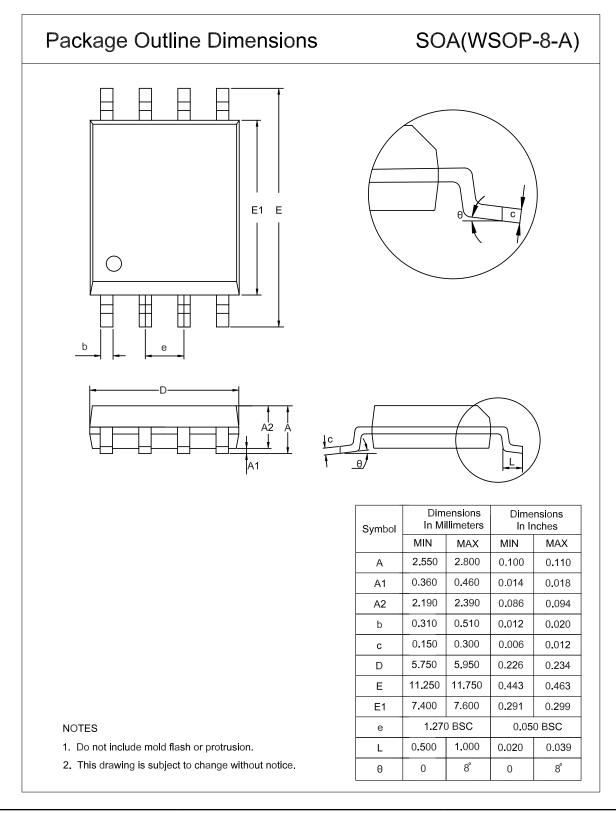

## **Package Outline Dimensions**

#### WSOP8-A

### **Order Information**

| Order Number          | Operating Ambient Temperature Range | Package | Marking<br>Information | MSL | Transport Media,<br>Quantity | Eco Plan |

|-----------------------|-------------------------------------|---------|------------------------|-----|------------------------------|----------|

| TPM5350MQ-SOAR-S      | −40 to 125°C                        | WSOP8   | 535MQ                  | 3   | 1000                         | Green    |

| TPM5350BMQ-SOAR-S (1) | −40 to 125°C                        | WSOP8   | 53BMQ                  | 3   | 1000                         | Green    |

| TPM5350MQ-SO1R-S      | −40 to 125°C                        | WSOP8   | 535MQ                  | 3   | 1000                         | Green    |

| TPM5350SQ-SOAR-S (1)  | −40 to 125°C                        | WSOP8   | 535SQ                  | 3   | 1000                         | Green    |

| TPM5350BSQ-SOAR-S (1) | −40 to 125°C                        | WSOP8   | Q535BS                 | 3   | 1000                         | Green    |

| TPM5350SQ-SO1R-S (1)  | −40 to 125°C                        | WSOP8   | 535SQ                  | 3   | 1000                         | Green    |

| TPM5350M-SOAR         | −40 to 125°C                        | WSOP8   | M535M                  | 3   | 1000                         | Green    |

| TPM5350S-SOAR (1)     | −40 to 125°C                        | WSOP8   | M535S                  | 3   | 1000                         | Green    |

| TPM5350BS-SOAR (1)    | −40 to 125°C                        | WSOP8   | M535BS                 | 3   | 1000                         | Green    |

**Green**: 3PEAK defines "Green" to mean RoHS compatible and free of halogen substances.

#### IMPORTANT NOTICE AND DISCLAIMER

Copyright<sup>©</sup> 3PEAK 2012-2024. All rights reserved.

**Trademarks.** Any of the 思瑞浦 or 3PEAK trade names, trademarks, graphic marks, and domain names contained in this document /material are the property of 3PEAK. You may NOT reproduce, modify, publish, transmit or distribute any Trademark without the prior written consent of 3PEAK.

**Performance Information.** Performance tests or performance range contained in this document/material are either results of design simulation or actual tests conducted under designated testing environment. Any variation in testing environment or simulation environment, including but not limited to testing method, testing process or testing temperature, may affect actual performance of the product.

**Disclaimer.** 3PEAK provides technical and reliability data (including data sheets), design resources (including reference designs), application or other design recommendations, networking tools, security information and other resources "As Is". 3PEAK makes no warranty as to the absence of defects, and makes no warranties of any kind, express or implied, including without limitation, implied warranties as to merchantability, fitness for a particular purpose or non-infringement of any third-party's intellectual property rights. Unless otherwise specified in writing, products supplied by 3PEAK are not designed to be used in any life-threatening scenarios, including critical medical applications, automotive safety-critical systems, aviation, aerospace, or any situations where failure could result in bodily harm, loss of life, or significant property damage. 3PEAK disclaims all liability for any such unauthorized use.

www.3peak.com 27 / 28 EA20230502A0

This page intentionally left blank