### **Features**

- Drives Both High-side and Low-side N-Channel MOSFET with Independent Inputs

- 4-A Peak Output Source and Sink Current Capability

- Max Bootstrap Supply Voltage up to 120 V

- Wide Supply Rail from 7 V to 20 V

- Integrated Bootstrap Diode

- TTL/CMOS Compatible Input, -10-V to 20-V Input Capability

- · 20-ns Propagation Delay Times

- · 2-ns Delay Matching

- 7-ns Rise and 4.5-ns Fall Time with 1000-pF Load

- 15-ns Input Deglitching Time

- 20-ns Minimum Pulse Width

- Supply Rail Under-Voltage Lockout (UVLO)

- Operation from -40°C to 150°C

- Available in SOP8, ESOP8, DFN4X4-8 and DFN4X4-10 Packages

### **Applications**

- Power Supplies for Telecom, Datacom, and Data Centers

- Half-Bridge and Full-Bridge Converters

- Push-Pull Converters

- High-Voltage Synchronous-Buck Converters

- 48-V Fan Driver

### **Description**

The TPM2721x MOSFET drivers are pin-to-pin compatible with industrial-standard 100-V half-bridge drivers. They are designed to control two N-channel MOSFETs in half-bridge or synchronous-buck configurations. They have higher peak currents at 4 A for both pull-up and pull-down, and lower resistance at 0.9  $\Omega$ . This helps drive bigger MOSFETs with less switching loss. They can handle –10 VDC input directly, which is stronger and lets them connect to the gate-drive transformers without external diodes. The drivers work with any supply voltage up to 20 V.

Both high-side and low-side driver stages have an undervoltage lockout that forces outputs low if the supply voltage drops below the set threshold. An integrated bootstrap diode eliminates the need for an external diode in many setups, saving space and reducing costs. The TPM27211 comes in various packages, ESOP8, DFN4X4-10, DFN4X4-8, DFN3X3-8, etc, suitable for high-density designs.

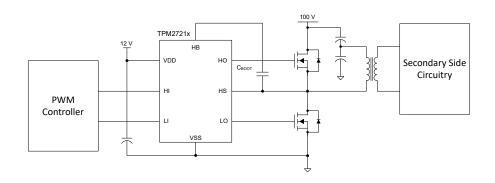

## **Typical Application Circuit**

## **Table of Contents**

| Features                                | 1  |

|-----------------------------------------|----|

| Applications                            |    |

| Description                             | 1  |

| Typical Application Circuit             | 1  |

| Revision History                        | 3  |

| Pin Configuration and Functions         | 4  |

| Specifications                          | 7  |

| Absolute Maximum Ratings                | 7  |

| ESD, Electrostatic Discharge Protection | 7  |

| Recommended Operating Conditions        | 8  |

| Thermal Information                     | 8  |

| Electrical Characteristics              | 9  |

| Typical Performance Characteristics     | 11 |

| Detailed Description                    | 14 |

| Overview                                | 14 |

| Functional Block Diagram                | 15 |

| Feature Description                     | 15 |

| Application and Implementation          | 17 |

| Application Information                 | 17 |

| Typical Application                     | 18 |

| Layout                                  | 19 |

| Layout Guideline                        | 19 |

| Layout Example                          | 19 |

| Tape and Reel Information               | 20 |

| Package Outline Dimensions              | 21 |

| ESOP8                                   | 21 |

| DFN4X4-10                               | 22 |

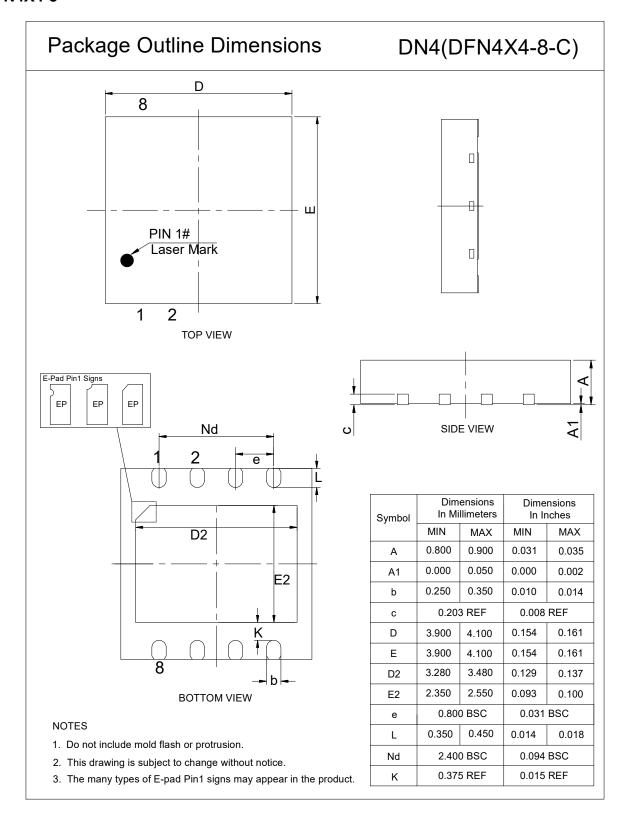

| DFN4X4-8                                | 23 |

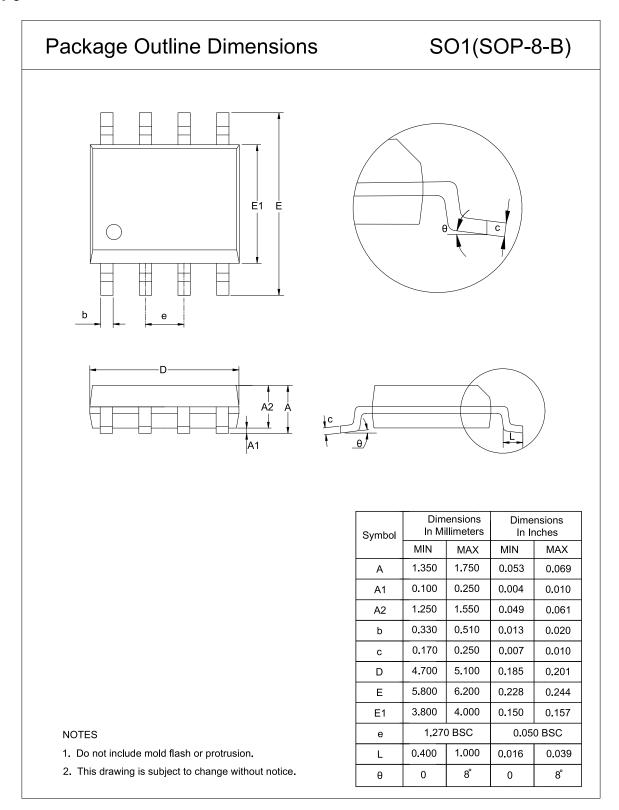

| SOP8                                    | 24 |

| Order Information                       | 25 |

| IMPORTANT NOTICE AND DISCLAIMER         | 26 |

## **Revision History**

| Date       | Revision | Notes            |

|------------|----------|------------------|

| 2025-07-22 | Rev.A.0  | Initial release. |

www.3peak.com 3 / 26 EA20240801A0

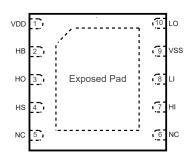

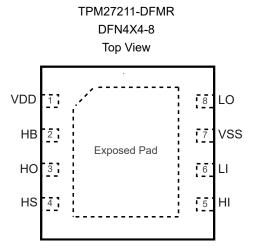

## **Pin Configuration and Functions**

TPM27211-DF9R DFN4X4-10 Top View

**Table 1. Pin Functions**

| Pin No.           |                   |      |     |                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|-------------------|-------------------|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TPM27211-<br>DF9R | TPM27211-<br>DFMR | Name | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 1                 | 1                 | VDD  | Р   | The low-side gate driver in the TPM27211 requires a positive supply, which should be decoupled to the VSS with a typical capacitor value of 1 $\mu$ F to ensure stable operation. If an external boot diode is used, its anode should be connected to this pin.                                                                                                                                                     |  |

| 2                 | 2                 | НВ   | Р   | The high-side bootstrap supply in the TPM27211 includes an integrated bootstrap diode with an external bootstrap capacitor. Attach the positive terminal of this capacitor to the HB pin, with a typical recommendation of 0.1 µF for the HB bypass capacitor, mainly determined by characteristics of the high-side MOSFET. When an external bootstrap diode is used, its cathode should be connected to this pin. |  |

| 3                 | 3                 | НО   | 0   | The high-side output of the TPM27211. This pin should be connected directly to the gate of the high-side power MOSFET or to one terminal of an external gate resistor if used.                                                                                                                                                                                                                                      |  |

| 4                 | 4                 | HS   | Р   | The high-side source connection on the TPM27211 should be connected to the source of the high-side power MOSFET. The negative side of the bootstrap capacitor should be attached to this pin.                                                                                                                                                                                                                       |  |

| 5                 | n/a               | NC   | NC  | Not connected                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 6                 | n/a               | NC   | NC  | Not connected.                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 7                 | 5                 | НІ   | I   | High-side driver logic input, TTL compatible. Floating logic low.                                                                                                                                                                                                                                                                                                                                                   |  |

| 8                 | 6                 | LI   | I   | Low-side driver logic input, TTL compatible. Floating logic low.                                                                                                                                                                                                                                                                                                                                                    |  |

| 9                 | 7                 | VSS  | GND | Supply ground.                                                                                                                                                                                                                                                                                                                                                                                                      |  |

www.3peak.com 4 / 26 EA20240801A0

| Pin No.           |                   |      |     |                                                                                                                                                                                            |

|-------------------|-------------------|------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TPM27211-<br>DF9R | TPM27211-<br>DFMR | Name | I/O | Description                                                                                                                                                                                |

| 10                | 8                 | LO   | 0   | Low-side driver output. The low-side output of the TPM27211 should be connected directly to the gate of the low-side power MOSFET or to one terminal of an external gate resistor if used. |

| Exposed<br>Pad    | Exposed<br>Pad    | EP   | G   | Exposed Pad. Recommend to connect to GND                                                                                                                                                   |

www.3peak.com 5 / 26 EA20240801A0

LO

VSS

HI

# 120-V Supply, 4-A Peak, High-frequency HS and LS Gate Driver

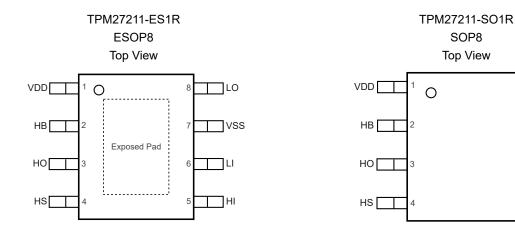

**Table 2. Pin Functions**

| Pin No.        |      |      |     |                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|----------------|------|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ESOP8          | SOP8 | Name | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 1              | 1    | VDD  | Р   | The low-side gate driver in the TPM27211 requires a positive supply, which should be decoupled to the VSS with a typical capacitor value of 1 $\mu$ F to ensure stable operation. If an external boot diode is used, its anode should be connected to this pin.                                                                                                                                                     |  |  |

| 2              | 2    | НВ   | Р   | The high-side bootstrap supply in the TPM27211 includes an integrated bootstrap diode with an external bootstrap capacitor. Attach the positive terminal of this capacitor to the HB pin, with a typical recommendation of 0.1 µF for the HB bypass capacitor, mainly determined by characteristics of the high-side MOSFET. When an external bootstrap diode is used, its cathode should be connected to this pin. |  |  |

| 3              | 3    | НО   | 0   | The high-side output of the TPM27211. This pin should be connected directly to the gate of the high-side power MOSFET or to one terminal of an external gate resistor if used.                                                                                                                                                                                                                                      |  |  |

| 4              | 4    | HS   | Р   | The high-side source connection on the TPM27211 should be connected to the source of the high-side power MOSFET. The negative side of the bootstrap capacitor should be attached to this pin.                                                                                                                                                                                                                       |  |  |

| 5              | 5    | HI   | I   | High-side driver logic input, TTL compatible. Floating logic low.                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 6              | 6    | LI   | I   | Low-side driver logic input, TTL compatible. Floating logic low.                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 7              | 7    | VSS  | GND | Supply ground.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 8              | 8    | LO   | 0   | Low-side driver output. The low-side output of the TPM27211 should be connected directly to the gate of the low-side power MOSFET or to one terminal of an external gate resistor if used.                                                                                                                                                                                                                          |  |  |

| Exposed<br>Pad | n/a  | EP   | G   | Exposed Pad. Recommend to connect to GND                                                                                                                                                                                                                                                                                                                                                                            |  |  |

www.3peak.com 6 / 26 EA20240801A0

### **Specifications**

### **Absolute Maximum Ratings**

All test conditions: over operating free-air temperature, unless otherwise noted. (1)

|                                    | Parameter                                  | Min                   | Max                   | Unit |

|------------------------------------|--------------------------------------------|-----------------------|-----------------------|------|

| Supply Voltage                     | $V_{DD}$                                   | -0.3                  | 20                    | V    |

| Input Voltage                      | HI, LI                                     | -10                   | 20                    | V    |

| Output Voltage                     | LO (DC)                                    | -0.3                  | V <sub>DD</sub> + 0.3 | V    |

| Output Voltage                     | LO (Pulse < 100 ns) <sup>(3)</sup>         | -2                    | V <sub>DD</sub> + 0.3 | V    |

| Bootstrap Voltage                  | НВ                                         | -0.3                  | 120                   | V    |

| High-Side Voltage                  | HB-HS                                      | -0.3                  | 26                    | V    |

| Output Voltage                     | HO (DC)                                    | V <sub>HS</sub> - 0.3 | V <sub>HB</sub> + 0.3 | V    |

| Output Voltage                     | HO (Pulse < 100 ns) (3)                    | V <sub>HS</sub> - 2   | V <sub>HB</sub> + 0.3 | V    |

| High-Side MOSFET Source Voltage    | HS (DC)                                    | -8                    | 120                   | V    |

| High-Side MOSFET<br>Source Voltage | HS (Pulse < 300 ns) <sup>(3)</sup>         | -12                   | 120                   | V    |

| High-Side MOSFET<br>Source Voltage | HS (Pulse < 100 ns) <sup>(3)</sup>         | -18                   | 120                   | V    |

| TJ                                 | Maximum Operating Junction Temperature (2) | -40                   | 150                   | °C   |

| T <sub>STG</sub>                   | Storage Temperature Range                  | -65                   | 150                   | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause device permanent damage. The device is not guaranteed to function outside of its Recommended Operation Conditions.

### **ESD, Electrostatic Discharge Protection**

| Symbol           | Parameter                      | Condition                                                         | Min | Max | Unit |

|------------------|--------------------------------|-------------------------------------------------------------------|-----|-----|------|

|                  | Human Body Model ESD<br>(HBM)  | per ANSI-JEDEC-JS-001-2014 specification, all pins <sup>(1)</sup> | -2  | 2   | kV   |

| V <sub>ESD</sub> | Charged Device Model ESD (CDM) | per ANSI-JEDEC-JS-002-2014 specification, all pins <sup>(1)</sup> | -1  | 1   | kV   |

(1) HBM and CDM stressing are done in accordance with the ANSI/ESDA/JEDEC JS-001-2014 specifications.

www.3peak.com 7 / 26 EA20240801A0

<sup>(2)</sup> The IC includes over-temperature protection to protect the device during overload conditions. The junction temperature exceeds 150°C when the over-temperature protection is active. Continuous operation above the specified maximum operating junction temperature reduces lifetime.

<sup>(3)</sup> Values are verified by characterization and are not production-tested.

## **Recommended Operating Conditions**

Over-operating free-air temperature range unless otherwise noted

|                    | Parameter                                  | Min                           | Тур | Max                   | Unit |

|--------------------|--------------------------------------------|-------------------------------|-----|-----------------------|------|

| $V_{DD}$           | Supply Voltage Range                       | 7                             | 12  | 16                    | V    |

| V <sub>HI,LI</sub> | Driver Input Voltage Range                 | -10                           |     | VDD + 0.3             | V    |

| V                  | Voltage on HS (DC)                         | -8                            |     | 100                   | V    |

| V <sub>HS</sub>    | Voltage on HS (pulse width < 100 ns)       | -12                           |     | 110                   | V    |

| $V_{LO}$           | Voltage on LO                              | 0                             |     | V <sub>DD</sub> + 0.3 | V    |

| $V_{HO}$           | Voltage on HO                              | V <sub>HS</sub>               |     | V <sub>HB</sub> + 0.3 | V    |

| $V_{SR}$           | Slew Rate on HS                            |                               |     | 50                    | V/ns |

| V <sub>НВ</sub>    | Voltage on HB                              | V <sub>HS</sub> +7,<br>VDD -1 |     | V <sub>HS</sub> +16,  | V    |

| I <sub>BST</sub>   | Transient Internal Bootstrap Diode Current |                               |     | 2                     | Α    |

| TJ                 | Operating Junction Temperature             | -40                           |     | 150                   | °C   |

### **Thermal Information**

| Parameter | R <sub>0JA</sub> | R <sub>θJC</sub> | Unit |

|-----------|------------------|------------------|------|

| DFN4X4-8  | 35               | 41               | °C/W |

| DFN4X4-10 | 35               | 41               | °C/W |

| ESOP8     | 34.66            | 42.92            | °C/W |

| SOP8      | 105              | 51               | °C/W |

www.3peak.com 8 / 26 EA20240801A0

### **Electrical Characteristics**

All test conditions:  $V_{DD}$  = 12 V,  $T_J$  = -40°C~150°C, typical values are tested under 25°C, unless otherwise noted.

| Symbol                  | Parameter                   | Conditions                                                                       | Min  | Тур  | Max  | Unit |

|-------------------------|-----------------------------|----------------------------------------------------------------------------------|------|------|------|------|

| Supply C                | urrents                     |                                                                                  |      |      |      |      |

| I <sub>DD</sub>         | VDD Quiescent Current       | $V_{HI} = V_{LI} = 0$                                                            | 200  | 334  | 500  | μA   |

| I <sub>DDO</sub>        | VDD Operating Current       | f <sub>SW</sub> = 500 kHz, C <sub>Load</sub> = 0 nF                              | 1.5  | 2.46 | 4.5  | mA   |

| I <sub>HB</sub>         | HB Quiescent Current        | $V_{HI} = V_{LI} = 0$                                                            | 90   | 138  | 410  | μA   |

| Інво                    | HB Operating Current        | f <sub>SW</sub> = 500 kHz, C <sub>Load</sub> = 0 nF                              | 1.6  | 2.75 | 3.8  | mA   |

| I <sub>HBS</sub>        | HB to VSS Quiescent Current | V <sub>HS</sub> = V <sub>HB</sub> = 110 V                                        |      |      | 1    | μA   |

| I <sub>HBSO</sub>       | HB to VSS Operating Current | $f_{SW} = 500 \text{ kHz}, C_{Load} = 0 \text{ nF}$                              | 0.05 | 0.51 | 0.95 | mA   |

| Inputs                  |                             |                                                                                  |      |      |      |      |

| V <sub>HI, LI,_R</sub>  | Input Logic High Threshold  |                                                                                  | 1.8  | 2.1  | 2.4  | V    |

| V <sub>HI, LI_F</sub>   | Input Logic Low Threshold   |                                                                                  | 0.8  | 1.14 | 1.5  | V    |

| V <sub>HI, LI_Hys</sub> | Hysteresis                  |                                                                                  |      | 0.96 |      | V    |

| Undervol                | tage Protection (UVLO)      |                                                                                  |      |      |      |      |

| $V_{DDR}$               | VDD Rising Threshold        |                                                                                  | 6.1  | 6.55 | 6.85 | V    |

| V <sub>DDF</sub>        | VDD Falling Threshold       |                                                                                  | 5.7  | 6.15 | 6.5  | V    |

| V <sub>DDHYS</sub>      | VDD Threshold Hysteresis    |                                                                                  |      | 0.33 |      | V    |

| $V_{HBR}$               | HB Rising Threshold         |                                                                                  | 5.3  | 5.78 | 6.17 | V    |

| V <sub>HBF</sub>        | HB Falling Threshold        |                                                                                  | 4.9  | 5.27 | 5.7  | V    |

| V <sub>HBHYS</sub>      | HB Threshold Hysteresis     |                                                                                  |      | 0.38 |      | V    |

| LO Gate                 | Driver                      |                                                                                  |      |      |      |      |

| V <sub>LOH</sub>        | Output High Voltage         | $I_{OUT} = -100 \text{ mA}, V_{LOH} = V_{DD} - V_{LO}$                           | 50   | 108  | 220  | mV   |

| V <sub>LOL</sub>        | Output Low Voltage          | I <sub>OUT</sub> = 100 mA                                                        | 18   | 36   | 70   | mV   |

| LOSRC                   | Output Source Peak Current  | C <sub>Load</sub> = 10 nF, V <sub>LO</sub> = 0 V                                 |      | 3.5  |      | Α    |

| ILOSINK                 | Output Sink Peak Current    | C <sub>Load</sub> = 10 nF, V <sub>LO</sub> = 12 V                                |      | 6.5  |      | Α    |

| R <sub>LOH</sub>        | Output Pull High Resistance | I <sub>OUT</sub> = -100 mA                                                       | 0.5  | 1    | 2.2  | Ω    |

| R <sub>LOL</sub>        | Output Pull Low Resistance  | I <sub>OUT</sub> = 100 mA                                                        | 0.18 | 0.4  | 0.7  | Ω    |

| HO Gate                 | Driver                      |                                                                                  |      |      |      |      |

| V <sub>HOH</sub>        | Output High Voltage         | I <sub>OUT</sub> = -100 mA, V <sub>HOH</sub> = V <sub>HB</sub> - V <sub>HO</sub> | 50   | 104  | 220  | mV   |

| V <sub>HOL</sub>        | Output Low Voltage          | I <sub>OUT</sub> = 100 mA                                                        | 20   | 41   | 75   | mV   |

| I<br>HOSRC              | Output Source Peak Current  | C <sub>Load</sub> = 10 nF, V <sub>HO</sub> = 0 V                                 |      | 3.5  |      | А    |

| I <sub>HOSINK</sub>     | Output Sink Peak Current    | C <sub>Load</sub> = 10 nF, V <sub>HO</sub> = 12 V                                |      | 6.5  |      | Α    |

| R <sub>HOH</sub>        | Output Pull High Resistance | I <sub>OUT</sub> = -100 mA                                                       | 0.5  | 1    | 2.2  | Ω    |

| RHOL                    | Output Pull Low Resistance  | I <sub>OUT</sub> = 100 mA                                                        | 0.2  | 0.4  | 0.75 | Ω    |

www.3peak.com 9 / 26 EA20240801A0

| Symbol                   | Parameter                    | Conditions                     | Min | Тур   | Max | Unit |

|--------------------------|------------------------------|--------------------------------|-----|-------|-----|------|

| Bootstra                 | pe Diode                     |                                |     |       |     |      |

| V <sub>FL</sub>          | Low Current Forward Voltage  | I <sub>VDD</sub> – HB = 100 uA | 0.8 | 1.266 | 2.1 | V    |

| V <sub>FH</sub>          | High Current Forward Voltage | I <sub>VDD</sub> – HB = 100 mA | 1.4 | 1.899 | 2.8 | V    |

| R <sub>D</sub>           | Dynamic Resistance           |                                |     | 3.998 | 10  | Ω    |

| Output R                 | ise and Fall Time            |                                |     |       |     |      |

| T <sub>DLFF</sub>        | VLI falling to VLO falling   | C <sub>Load</sub> = 10 pF      |     | 27.6  |     | ns   |

| T <sub>DHFF</sub>        | VHI falling to VHO falling   | C <sub>Load</sub> = 10 pF      |     | 29.4  |     | ns   |

| T <sub>DLRR</sub>        | VLI rising to VLO rising     | C <sub>Load</sub> = 10 pF      |     | 29.2  |     | ns   |

| T <sub>DHRR</sub>        | VHI rising to VHO rising     | C <sub>Load</sub> = 10 pF      |     | 29.4  |     | ns   |

| T <sub>R</sub>           | LO, HO Rise Time             | C <sub>Load</sub> = 1.8 nF     |     | 10.94 |     | ns   |

| T <sub>F</sub>           | LO, HO Fall Time             | C <sub>Load</sub> = 1.8 nF     |     | 5.63  |     | ns   |

| Delay Ma                 | tching                       |                                |     |       |     |      |

| T <sub>MON</sub>         | HO OFF to LO ON              |                                |     | 2     |     | ns   |

| T <sub>MOFF</sub>        | LO OFF to HO ON              |                                |     | 2     |     | ns   |

| Miscellar                | eous                         |                                |     |       |     |      |

| T <sub>MIN_ON</sub>      | Minimum Input Pulse Width    |                                |     | 9     |     | ns   |

| T <sub>IN_Deglitch</sub> | Input Deglitch Time          |                                |     | 15    |     | ns   |

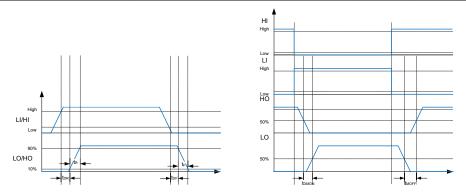

Figure 1. Timing Diagram

www.3peak.com 10 / 26 EA20240801A0

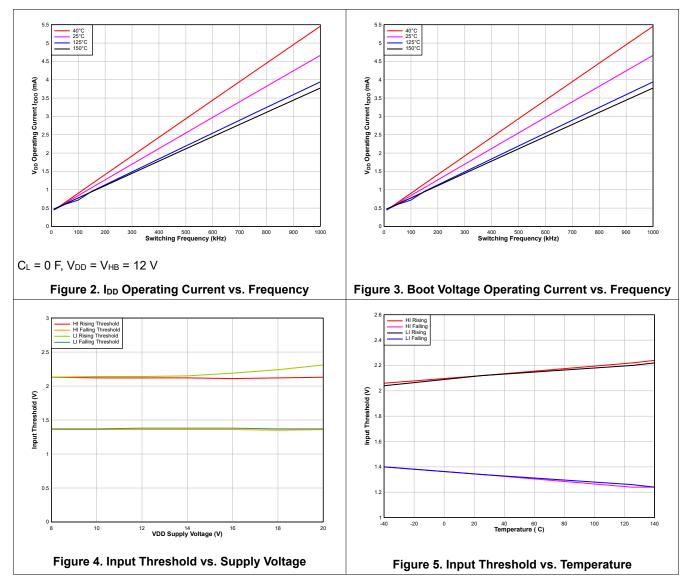

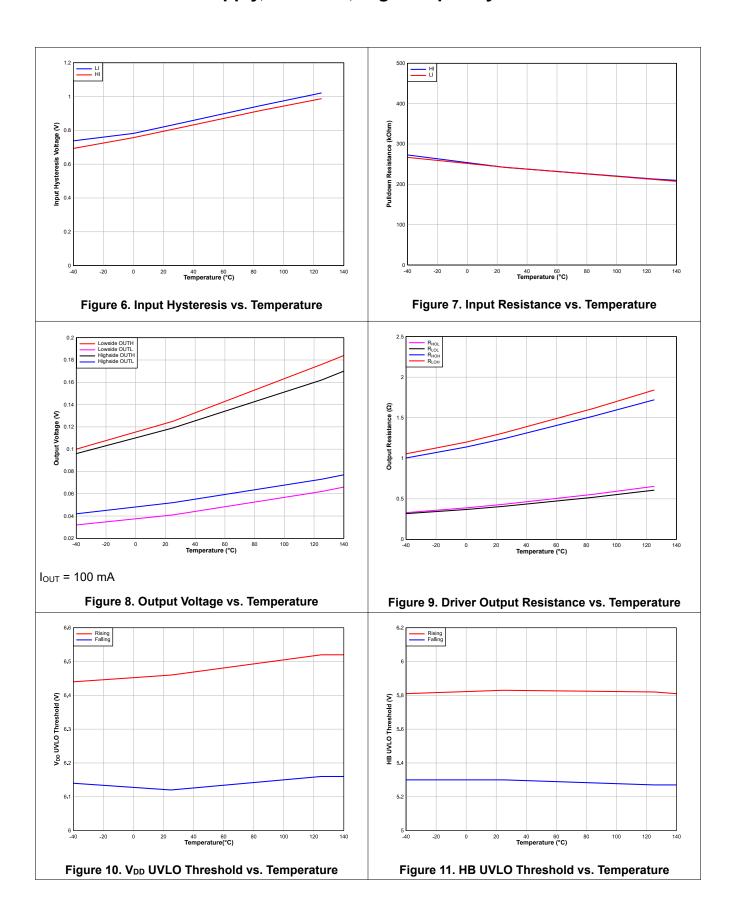

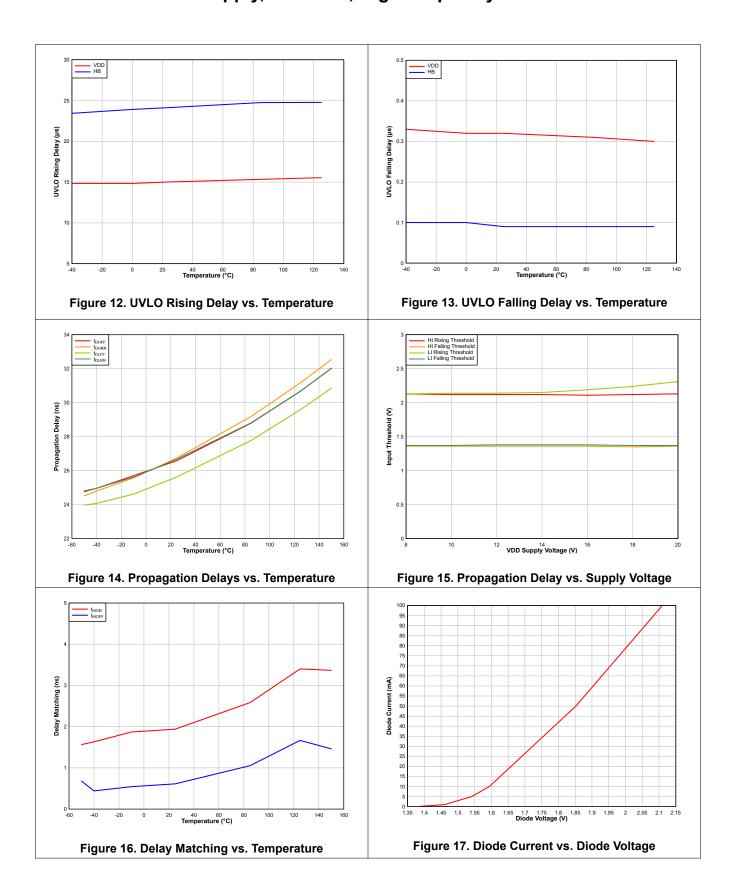

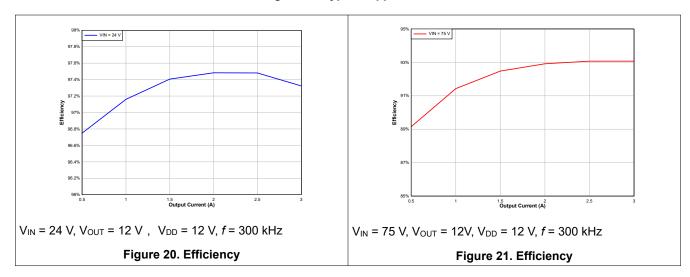

### **Typical Performance Characteristics**

All test conditions:  $V_{DD} = V_{HB} = 12 \text{ V}$ ,  $V_{HS} = V_{SS} = 0 \text{ V}$ , no load on outputs, unless otherwise noted.

www.3peak.com 11 / 26 EA20240801A0

### **Detailed Description**

#### Overview

The TPM27211 is a high-side and low-side MOSFET driver, featuring independent inputs for each side, providing ultimate flexibility in controlling application signals. It includes an integrated boot diode for the bias supply of the high-side driver and is compatible with TTL logic inputs. The high-side driver operates in reference to the switch node (HS), typically connected to the source of the high-side MOSFET and the drain of the low-side MOSFET. The low-side driver is grounded at VSS. Key functions include input stages, under-voltage lockout (UVLO) protection, level shifting, the integrated boot diode, and output driver stages.

Table 3. The TPM27211 Device Logic

| Н | LI | НО | LO |

|---|----|----|----|

| L | L  | L  | L  |

| L | Н  | L  | Н  |

| Н | L  | Н  | L  |

| Н | Н  | Н  | Н  |

www.3peak.com 14 / 26 EA20240801A0

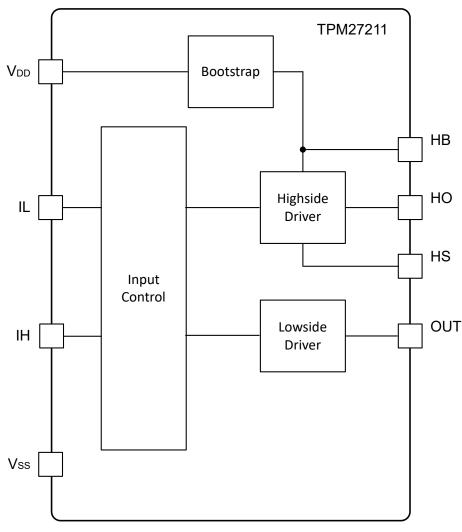

### **Functional Block Diagram**

Figure 18. Functional Block Diagram

### **Feature Description**

#### **Under-Voltage Lockout (UVLO)**

The gate driver incorporates under-voltage lockout (UVLO) protection for the bias supplies of both the high-side and low-side drivers, ensuring that the operation stops when voltages fall below the critical thresholds. The  $V_{DD}$  UVLO safeguards the entire system by disabling both drivers if  $V_{DD}$  is below 7.0 V, with a re-enabling threshold at 7.5 V, while the  $V_{HB}$  UVLO specifically targets the high-side driver, engaging if the  $V_{HB}$  to  $V_{HS}$  differential is below 6.7 V and re-enabling at 7.8 V. These features provide a reliable and stable operation with hysteresis to prevent oscillation around the threshold points.

#### **Input Stage**

The TPM27211 features input stages that facilitate PWM signal interfacing with specific characteristics. It is designed with a pseudo-CMOS input structure offering significant hysteresis and compatibility with various PWM controllers. The TPM27211

www.3peak.com 15 / 26 EA20240801A0

has a nominal impedance of 70 k $\Omega$  with the same capacitance of approximately 2 pF and a pull-down resistance to ground of 70 k $\Omega$ . It provides a more standard logic-level input with a rising threshold at 2.3 V and a falling threshold at 1.6 V.

The TPM27211 input stage withstands the negative voltage as low as −10 V to improve system robustness.

#### **Bootstrap Diode**

The TPM27211 drivers include an integrated boot diode for generating the high-side bias voltage. This diode has its anode connected to  $V_{DD}$  and its cathode connected to  $V_{HB}$ . The  $V_{HB}$  capacitor which is linked to both the HB and HS pins, is recharged during each switching cycle when the HS pin goes to the ground. The boot diode is designed to offer fast recovery, low resistance, and a voltage rating margin, ensuring efficient and dependable performance.

#### **Output Stages**

The output stages of the driver serve as the link to the power MOSFETs in the power train. They are designed for high efficiency, with characteristics, such as high slew rate, minimal resistance, and the ability to handle high peak currents, ensuring that the power MOSFETs switch effectively. The low-side output stage operates with a reference from  $V_{DD}$  to  $V_{SS}$ , while the high-side output stage is referenced between  $V_{HB}$  and  $V_{HS}$ .

www.3peak.com 16 / 26 EA20240801A0

## **Application and Implementation**

Note

Information in the following application sections is not part of the 3PEAK's component specification and 3PEAK does not warrant its accuracy or completeness. 3PEAK's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### **Application Information**

#### **Driver Power Dissipation**

The power dissipation of the gate driver consists of two parts: quiescent power (PDC) and switching power (PG).

The DC component of power loss in the driver is given by:

$$P_{DC} = I_{Q} \times V_{DD} \tag{1}$$

Where:

IQ represents the quiescent current of the driver. This current is used to power all the internal circuits.

The power  $P_G$  is lost in the resistive components of the circuit during the MOSFET/IGBT switching transitions. Approximately half of this power is expended when the load capacitor charges on turn-on, and the other half is lost when the load capacitor discharges on turn-off. Without the use of an external gate resistor between the driver and the MOSFET/IGBT, the entire  $P_G$  is dissipated within the driver package itself. However, by incorporating external gate-drive resistors, the power dissipation is distributed between the internal resistance of the driver and the external gate resistors, effectively sharing the thermal load.

$$P_{G} = Q_{q} \times V_{DD} \times f_{SW}$$

(2)

Where:

- Qg is the gate charge of the power device;

- f<sub>SW</sub> is the switching frequency;

- V<sub>DD</sub> is the supply voltage.

If  $R_G$  is applied between the driver and the gate of the power device to slow down the power device transition, the power dissipation of the driver is shown below:

$$P_{G} = \frac{1}{2} \times Q_{g} \times V_{DD} \times f_{SW} \times \left(\frac{R_{OL}}{R_{OL} + R_{G}} + \frac{R_{OH}}{R_{OH} + R_{G}}\right)$$

(3)

where

- R<sub>OH</sub> is the equivalent pull-up resistance of the TPM27211;

- RoL is the pull-down resistance of the TPM27211;

- R<sub>G</sub> is the gate resistance between the driver output and the gate of the power device.

www.3peak.com 17 / 26 EA20240801A0

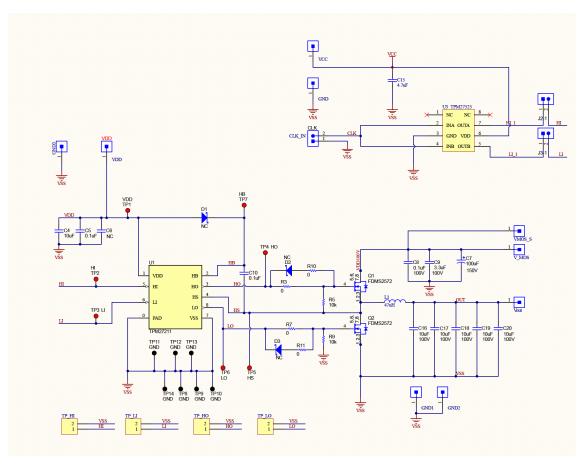

## **Typical Application**

Figure 19. Typical Application

www.3peak.com 18 / 26 EA20240801A0

## Layout

### **Layout Guideline**

- For the voltage mode input driver, a low ESR and ESL capacitor should be placed close to VCC and VEE pins, and make the loop from VCC to VEE small.

- For the current mode input driver, a low ESR and ESL capacitor should be placed close to the cathode and anode pins.

- To ensure isolation performance between the primary and secondary sides, avoid placing any PCB traces or copper below the driver device. A PCB cutout or groove is recommended to increase the creepage distance.

- To enhance thermal performance, a PCB copper connected with VCC and VEE is recommended to be enlarged.

- Use the Kelvin source to decouple the power loop and driver loop.

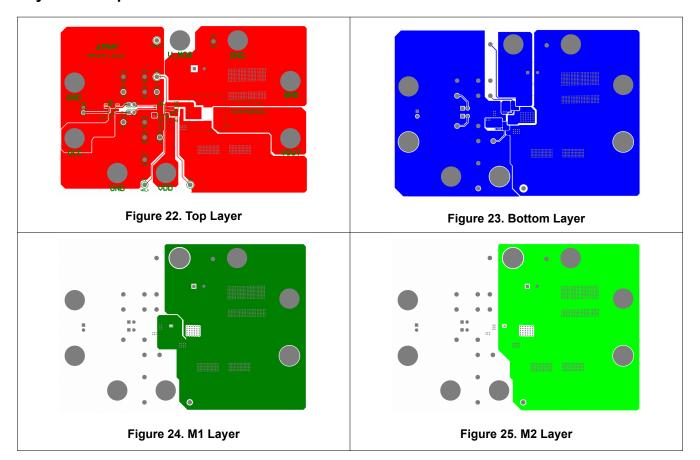

### **Layout Example**

www.3peak.com 19 / 26 EA20240801A0

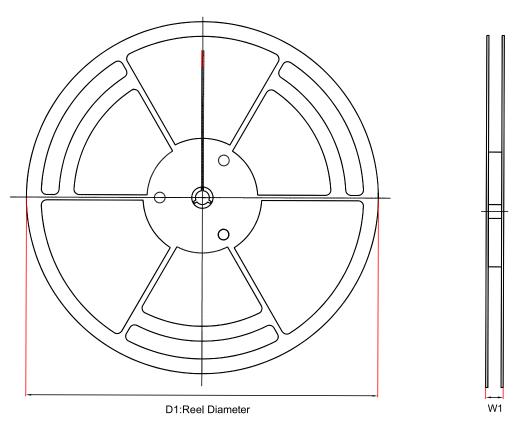

# **Tape and Reel Information**

| Order Number  | Package   | D1   | W1   | A0   | В0   | K0   | P0   | W0   | Pin1     |

|---------------|-----------|------|------|------|------|------|------|------|----------|

|               |           | (mm) | Quadrant |

| TPM27211-ES1R | ESOP8     | 330  | 17.6 | 6.4  | 5.4  | 2.1  | 8    | 12   | Q1       |

| TPM27211-SO1R | SOP8      | 330  | 17.6 | 6.5  | 5.4  | 2    | 8    | 12   | Q1       |

| TPM27211-DFMR | DFN4X4-8  | 330  | 17.6 | 4.3  | 4.3  | 1.1  | 8    | 12   | Q2       |

| TPM27211-DF9R | DFN4X4-10 | 330  | 17.6 | 4.3  | 4.3  | 1.1  | 8    | 12   | Q2       |

www.3peak.com 20 / 26 EA20240801A0

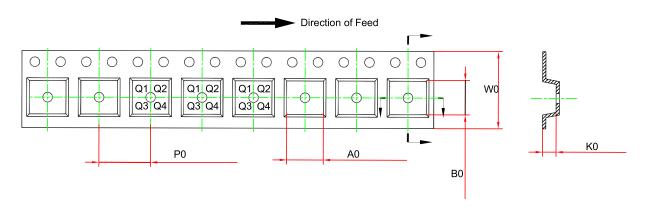

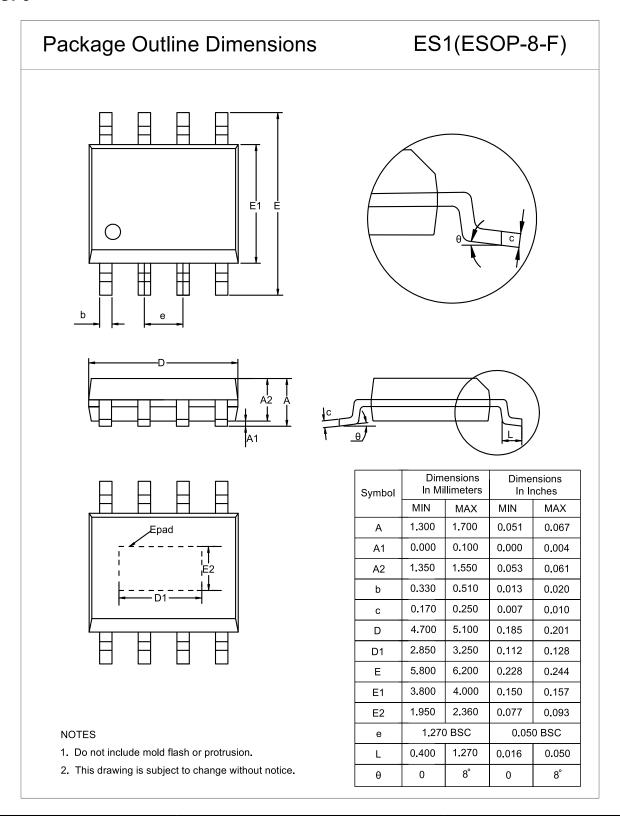

## **Package Outline Dimensions**

### ESOP8

#### **DFN4X4-10**

www.3peak.com 22 / 26 EA20240801A0

#### **DFN4X4-8**

www.3peak.com 23 / 26 EA20240801A0

### SOP8

www.3peak.com 24 / 26 EA20240801A0

### **Order Information**

| Order Number      | Operating Temperature<br>Range | Package   | Marking Information | MSL  | Transport Media, Quantity | Eco Plan |

|-------------------|--------------------------------|-----------|---------------------|------|---------------------------|----------|

| TPM27211-ES1R     | −40 to 125°C                   | ESOP8     | 27211               | MSL1 | Tape and Reel, 4000       | Green    |

| TPM27211-SO1R (1) | −40 to 125°C                   | SOP8      | 27211               | MSL1 | Tape and Reel,4000        | Green    |

| TPM27211-DF9R (1) | −40 to 125°C                   | DFN4X4-10 | 27211               | MSL3 | Tape and Reel,3000        | Green    |

| TPM27211-DFMR     | −40 to 125°C                   | DFN4X4-8  | 27211               | MSL1 | Tape and Reel,3000        | Green    |

<sup>(1)</sup> Contact 3PEAK sales representatives for more information.

**Green**: 3PEAK defines "Green" to mean RoHS compatible and free of halogen substances.

www.3peak.com 25 / 26 EA20240801A0

### IMPORTANT NOTICE AND DISCLAIMER

Copyright<sup>©</sup> 3PEAK 2012-2025. All rights reserved.

**Trademarks.** Any of the 思瑞浦 or 3PEAK trade names, trademarks, graphic marks, and domain names contained in this document /material are the property of 3PEAK. You may NOT reproduce, modify, publish, transmit or distribute any Trademark without the prior written consent of 3PEAK.

**Performance Information.** Performance tests or performance range contained in this document/material are either results of design simulation or actual tests conducted under designated testing environment. Any variation in testing environment or simulation environment, including but not limited to testing method, testing process or testing temperature, may affect actual performance of the product.

**Disclaimer.** 3PEAK provides technical and reliability data (including data sheets), design resources (including reference designs), application or other design recommendations, networking tools, security information and other resources "As Is". 3PEAK makes no warranty as to the absence of defects, and makes no warranties of any kind, express or implied, including without limitation, implied warranties as to merchantability, fitness for a particular purpose or non-infringement of any third-party's intellectual property rights. Unless otherwise specified in writing, products supplied by 3PEAK are not designed to be used in any life-threatening scenarios, including critical medical applications, automotive safety-critical systems, aviation, aerospace, or any situations where failure could result in bodily harm, loss of life, or significant property damage. 3PEAK disclaims all liability for any such unauthorized use.

www.3peak.com 26 / 26 EA20240801A0