#### **Features**

- Input Voltage Range 2 V to 5.5 V

- Sustain up to 22 V Input with Shunt Reference Structure

- · Shunt Reference Output Capability up to 15 mA

- Four-Channel Power Supply Monitor and Sequence Control

- 3.5% Accurate Adjustable Threshold Monitors Voltages down to 0.98V for Each Channel

- Independent Channel Enable/Disable Control

- Independent Channel Adjustable Time by Capacitor

- Open Drain Output

- Global Enable Control All Channels

- Power Good Indication for All Channels

- 5% High Accuracy of Sequence Timing

- QFN3.5x3.5-20 Package

### **Applications**

- Communications

- · Servers and Networking Elements

- Multiple Power Supply Sequencing

- Microcontroller Power Sequencing

### **Description**

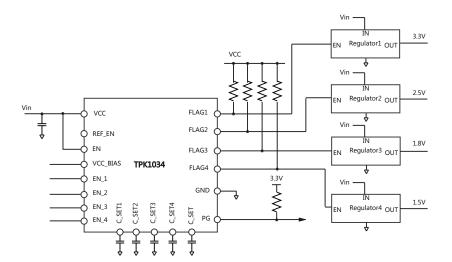

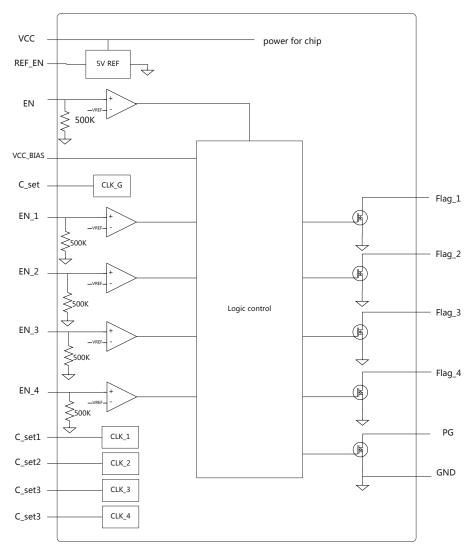

TPK1034 is a low voltage four-channel power monitor and sequencer. The power supply range is 2 V to 5.5 V, while if the shunt reference is enabled, the TPK1034 can sustain up to 22 V supply voltage. Each channel has an independent and adjustable threshold that can monitor voltage down to 0.98 V. If the monitored voltage falls below the threshold, the corresponding output is low. If the monitored voltage rises above the threshold, the output turns high after a capacitor-set delay time, the channel output is open-drain configuration.

With the power monitor function, the TPK1034 can achieve power sequencing control, and the capacitor of each channel can adjust the sequencing timing.

TPK1034 has an overall enable control for all channel outputs. When overall enable is active, each channel can be controlled by the corresponding enable. The overall enable control can disable all channel outputs by turning channel output low in a fixed sequence from channel 4 to channel 3, then channel 2 and channel 1. There is a delay time before each channel outputs low, which can be adjustable by another capacitor.

TPK1034 also includes a power good indication with opendrain active high to indicate all channels output high.

### **Typical Application Circuit**

### **Table of Contents**

| Features                                | 1  |

|-----------------------------------------|----|

| Applications                            | 1  |

| Description                             | 1  |

| Typical Application Circuit             | 1  |

| Product Family Table                    | 3  |

| Revision History                        | 3  |

| Pin Configuration and Functions         | 4  |

| Specifications                          | 6  |

| Absolute Maximum Ratings                | 6  |

| ESD, Electrostatic Discharge Protection | 6  |

| Thermal Information                     | 6  |

| Electrical Characteristics              | 7  |

| Typical Performance Characteristics     | 9  |

| Detailed Description                    | 11 |

| Overview                                | 11 |

| Functional Block Diagram                | 12 |

| Feature Description                     | 12 |

| Application and Implementation          | 15 |

| Application Information                 | 15 |

| Typical Application                     | 15 |

| Tape and Reel Information               | 17 |

| Package Outline Dimensions              | 18 |

| QFN3.5X3.5-20                           | 18 |

| Order Information                       | 19 |

| IMPORTANT NOTICE AND DISCLAIMER         | 20 |

## **Product Family Table**

| Order Number   | MSL | MPQ  | Marking | Package       |

|----------------|-----|------|---------|---------------|

| TPK1034-QF6R-S | 1   | 4000 | K1034   | QFN3.5x3.5-20 |

### **Revision History**

| Date      | Revision | Notes           |

|-----------|----------|-----------------|

| 2024-9-30 | Rev.A.0  | Initial release |

www.3peak.com 3 / 20 FA20240601A0

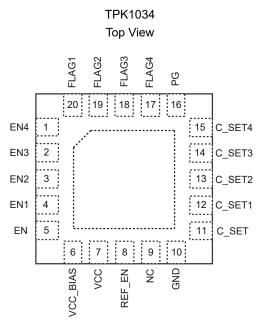

## **Pin Configuration and Functions**

Table 1. Pin Functions: TPK1034

| Pin No. | Name | I/O | Description                                                                                                                                                                                                                                                                                  |

|---------|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | EN4  | I   | Channel 4 power monitor or channel enable control. If the voltage on this pin falls below the internal falling threshold, FLAG4 output is low. If the voltage on this pin rises above the rising threshold, FLGA4 output is high after delay time programmed by the capacitor on C_SET4.     |

| 2       | EN3  | I   | Channel 3 power monitor or channel enable control. If the voltage on this pin falls below the internal falling threshold, FLAG3 output is low. If the voltage on this pin rises above the rising threshold, FLGA3 output is high after the delay time programmed by the capacitor on C_SET3. |

| 3       | EN2  | I   | Channel 2 power monitor or channel enable control. If the voltage on this pin falls below the internal falling threshold, FLAG2 output is low. If the voltage on this pin rises above the rising threshold, FLGA2 output is high after the delay time programmed by the capacitor on C_SET2. |

| 4       | EN1  | I   | Channel 1 power monitor or channel enable control. If the voltage on this pin falls below the internal falling threshold, FLAG1 output is low. If the voltage on this pin rises above the rising threshold, FLGA1 output is high after the delay time programmed by the capacitor on C_SET1. |

| 5       | EN   | I   | Overall EN Control. Drive EN high, then each channel can be used.                                                                                                                                                                                                                            |

www.3peak.com 4 / 20 FA20240601A0

| Pin No. | Name     | I/O | Description                                                                                                    |

|---------|----------|-----|----------------------------------------------------------------------------------------------------------------|

| 6       | VCC_BIAS | I   | Bias Voltage before VCC power on. Provide a bias voltage on this pin to pull the Flag low before VCC power on. |

| 7       | VCC      | I   | Input power supply.                                                                                            |

| 8       | REF_EN   | I   | Shunt reference enable input. Leave it not connected if used, connect to VCC if not used.                      |

| 9       | NC       | -   | Not Connected.                                                                                                 |

| 10      | GND      | GND | Ground.                                                                                                        |

| 11      | C_SET    | 0   | Overall delay time set pin. Connect a capacitor from C_SET to GND to set the all channels power down delay.    |

| 12      | C_SET1   | 0   | Delay time set pin 1. Connect a capacitor from C_SET1 to GND to set the FLAG1 high delay time.                 |

| 13      | C_SET2   | 0   | Delay time set pin 2. Connect a capacitor from C_SET2 to GND to set the FLAG1 high delay time.                 |

| 14      | C_SET3   | 0   | Delay time set pin 3. Connect a capacitor from C_SET3 to GND to set the FLAG1 high delay time.                 |

| 15      | C_SET4   | 0   | Delay time set pin 4. Connect a capacitor from C_SET4 to GND to set the FLAG1 high delay time.                 |

| 16      | PG       | 0   | Power Good                                                                                                     |

| 17      | FLAG4    | 0   | Channel 4 output.                                                                                              |

| 18      | FLAG3    | 0   | Channel 3 output.                                                                                              |

| 19      | FLAG2    | 0   | Channel 2 output.                                                                                              |

| 20      | FLAG1    | 0   | Channel 1 output.                                                                                              |

www.3peak.com 5 / 20 FA20240601A0

### **Specifications**

#### **Absolute Maximum Ratings**

|                  | Parameter                                                                   | Min  | Max | Unit |

|------------------|-----------------------------------------------------------------------------|------|-----|------|

| Input            | VCC, EN, EN1, EN2, EN3, EN4, VCC_BIAS, REF_EN to GND                        | -0.3 | 6   | V    |

| Output           | C_SET, C_SET1, C_SET2, C_SET3,<br>C_SET4, PG, FLAG1, FLAG2, FLAG3,<br>FLAG4 | -0.3 | 6   | V    |

| TJ               | Maximum Junction Temperature                                                | -40  | 150 | °C   |

| T <sub>A</sub>   | Operating Temperature Range                                                 | -40  | 125 | °C   |

| T <sub>STG</sub> | Storage Temperature Range                                                   | -65  | 150 | °C   |

| TL               | Lead Temperature (Soldering 10 sec)                                         |      | 260 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

#### **ESD, Electrostatic Discharge Protection**

|     | Parameter                | Condition                  | Minimum Level | Unit |

|-----|--------------------------|----------------------------|---------------|------|

| НВМ | Human Body Model ESD     | ANSI/ESDA/JEDEC JS-001 (1) | 2000          | V    |

| CDM | Charged Device Model ESD | ANSI/ESDA/JEDEC JS-002 (2) | 500           | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### **Thermal Information**

| Package Type  | θ <sub>JA</sub> | θ <sub>ЈВ</sub> | <b>Ө</b> лс | Unit |

|---------------|-----------------|-----------------|-------------|------|

| QFN3.5x3.5-20 | 34.1            | 8.1             | 20.8        | °C/W |

www.3peak.com 6 / 20 FA20240601A0

<sup>(2)</sup> This data was taken with the JEDEC low effective thermal conductivity test board.

<sup>(3)</sup> This data was taken with the JEDEC standard multilayer test boards.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### **Electrical Characteristics**

All test conditions:  $V_{CC}=2V\sim5.5V$ ,  $T_A=40^{\circ}C$  to  $125^{\circ}C$ , unless otherwise noted.

| Symbol                 | Parameter                   | Test Conditions                                                           | Min   | Тур   | Max   | Unit   |  |

|------------------------|-----------------------------|---------------------------------------------------------------------------|-------|-------|-------|--------|--|

| Power Sup              | Power Supply                |                                                                           |       |       |       |        |  |

| V <sub>CC</sub>        | Input Supply Voltage        |                                                                           | 2     |       | 5.5   | V      |  |

|                        | 0                           | V <sub>CC</sub> = 5 V, REF is disabled                                    |       |       | 250   | μA     |  |

| IQ                     | Operation Quiescent Current | V <sub>CC</sub> = 3.3 V, REF is disabled                                  |       |       | 250   | μA     |  |

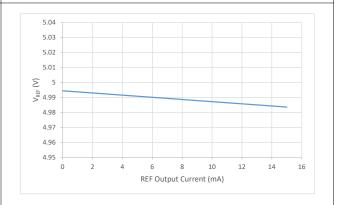

| V <sub>REF</sub>       | Shunt Reference Voltage     | VCC as shunt reference output voltage when shunt reference is enabled     | 4.85  | 5     | 5.15  | V      |  |

| I <sub>REF</sub>       | Reference Output Capability |                                                                           |       |       | 15    | mA     |  |

| UVLO                   | Under Voltage Lockout       | Vcc rising                                                                |       | 1.8   |       | V      |  |

| UVLO_HY<br>S           |                             |                                                                           |       | 0.2   |       | V      |  |

| REF_EN                 |                             |                                                                           |       |       |       |        |  |

| .,                     | REF_EN High Threshold       | REF_EN rising                                                             |       | 3.85  |       | V      |  |

| V <sub>REF_EN</sub>    | REF_EN Low Threshold        | REF_EN falling                                                            |       | 1.2   |       | V      |  |

| R <sub>REF_EN</sub>    | REF_EN Internal Pulldown    |                                                                           |       | 500   |       | kΩ     |  |

| Enable and             | d Monitor Threshold         |                                                                           |       |       |       |        |  |

| V <sub>IH_EN</sub>     | EN High Threshold Voltage   | EN rising                                                                 | 1.193 | 1.23  | 1.267 | V      |  |

| VIH_EN_HYS             | EN Hysteresis               | EN falling                                                                | 0.2   | 0.24  |       | V      |  |

| R <sub>EN</sub>        | EN Pull-down Resistor       |                                                                           |       | 550   |       | kΩ     |  |

| t <sub>GR_EN</sub>     | EN Glitch Rejection         |                                                                           |       | 500   |       | ns     |  |

| V <sub>IN_ENx</sub>    | ENx Fall Threshold Voltage  | ENx falling, $x = 1,2,3,4$                                                | 0.943 | 0.983 | 1.022 | V      |  |

| V <sub>IH_ENx_HY</sub> | ENx Hysteresis              | EN rising, x = 1,2,3,4                                                    |       | 0.23  |       | V      |  |

| R <sub>ENx</sub>       | ENx Pull-down Resistor      | x = 1,2,3,4                                                               |       | 550   |       | kΩ     |  |

| t <sub>GR_ENx</sub>    | ENx Glitch Rejection        | x = 1,2,3,4                                                               |       | 500   |       | ns     |  |

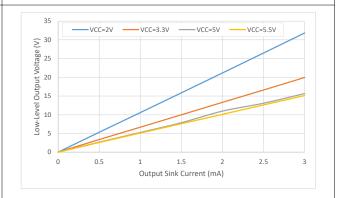

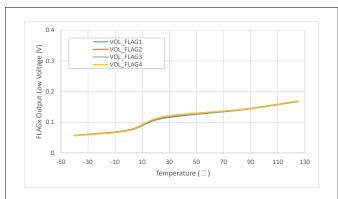

| Flag/PG O              | utput                       |                                                                           |       |       |       |        |  |

| I <sub>LKG_FLAGx</sub> | FLAGx Leakage Current       | V <sub>FLAGx</sub> =5 V, x = 1, 2, 3, 4                                   |       |       | 1     | μA     |  |

|                        | 5140 04 11                  | I <sub>FLAGx</sub> = 3 mA, x=1, 2, 3, 4, VCC > 1.2 V                      |       |       | 0.2   | \<br>\ |  |

| Vol_flagx              | FLAGx Output Low            | I <sub>FLAGx</sub> = 3 mA, x = 1, 2, 3, 4, VCC<br>= 0 V, VCC_BIAS > 1.2 V |       |       | 0.2   | V      |  |

| I <sub>PG</sub>        | PG Leakage Current          | V <sub>PG</sub> = 5 V                                                     |       |       | 1     | μA     |  |

|                        |                             | I <sub>PG</sub> = 3 mA, VCC > 1.2 V                                       |       |       | 0.2   | V      |  |

| V <sub>PG</sub>        | PG Output Low               | IPG = 3 mA, VCC = 0, VCC_Bias > 1.2 V                                     |       |       | 0.2   | V      |  |

www.3peak.com 7 / 20 FA20240601A0

| Symbol                   | Parameter                          | Test Conditions                 | Min    | Тур   | Max    | Unit |

|--------------------------|------------------------------------|---------------------------------|--------|-------|--------|------|

| Timing                   |                                    |                                 |        |       | -      |      |

| V <sub>HTH</sub>         | High Threshold Level               |                                 |        | 1.06  |        | V    |

| V <sub>LTH</sub>         | Low Threshold Level                |                                 |        | 0.47  |        | V    |

| I <sub>SRC</sub>         | Source Current                     |                                 |        | 9.7   |        | μA   |

| I <sub>SNK</sub>         | Sink Current                       |                                 |        | 9.7   |        | μA   |

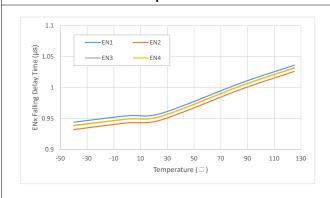

|                          |                                    | C_SETx open, x = 1, 2, 3, 4     |        | 75    |        | μs   |

| t <sub>ENx_FLAGx_</sub>  | END High to Elementical Deleve     | C_SETx = 330 pF, x = 1, 2, 3, 4 |        | 4.9   |        | ms   |

| CLK                      | ENx High to Flagx High Delay       | C_SETx = 1 nF, x= 1, 2, 3, 4    | 14.145 | 14.89 | 15.634 | ms   |

|                          |                                    | C_SETx =100 nF, x = 1, 2, 3, 4  | 1414.5 | 1489  | 1563.4 | ms   |

| t <sub>ENx_FALGx_L</sub> | ENx Low to Flagx Low Delay         |                                 |        | 1     |        | μs   |

|                          |                                    | C_SET = open                    |        | 300   |        | μs   |

|                          | ENLLt- Fla I Dala                  | C_SET = 330 pF                  |        | 19.6  |        | ms   |

| t <sub>EN_FLAG1</sub>    | EN Low to Flag1 Low Delay          | C_SET = 1 nF                    | 56.58  | 59.56 | 62.536 | ms   |

|                          |                                    | C_SET = 100 nF                  | 5658   | 5956  | 6253.6 | ms   |

|                          |                                    | C_SET = open                    |        | 225   |        | μs   |

|                          | ENLLt- Fla Pala                    | C_SET = 330 pF                  |        | 14.7  |        | ms   |

| t <sub>EN_FLAG2</sub>    | EN Low to Flag2 Low Delay          | C_SET = 1 nF                    | 42.435 | 44.67 | 46.902 | ms   |

|                          |                                    | C_SET = 100 nF                  | 4243.5 | 4467  | 4690.2 | ms   |

|                          |                                    | C_SET = open                    |        | 150   |        | μs   |

|                          | EN Laurta Flaga Laur Dalau         | C_SET = 330 pF                  |        | 9.8   |        | ms   |

| len_flag3                | EN_FLAG3 EN Low to Flag3 Low Delay | C_SET = 1 nF                    | 28.29  | 29.78 | 31.268 | ms   |

|                          |                                    | C_SET = 100 nF                  | 2829   | 2978  | 3126.8 | ms   |

|                          |                                    | C_SET = open                    |        | 75    |        | μs   |

|                          | ENLL out to Flora 1 and Dalan      | C_SET = 330 pF                  |        | 4.9   |        | ms   |

| t <sub>EN_FLAG4</sub>    | EN Low to Flag4 Low Delay          | C_SET = 1 nF                    | 14.145 | 14.89 | 15.634 | ms   |

|                          |                                    | C_SET = 100 nF                  | 1414.5 | 1489  | 1563.4 | ms   |

www.3peak.com 8 / 20 FA20240601A0

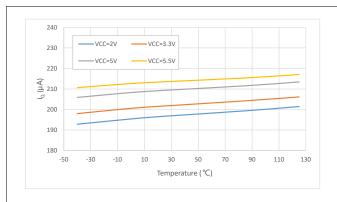

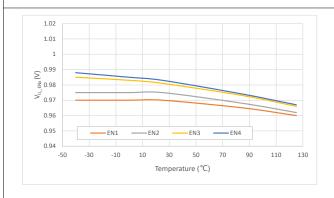

#### **Typical Performance Characteristics**

All test conditions: V<sub>CC</sub>=5V, T<sub>A</sub>=25°C, unless otherwise noted.

540

CC

90

520

530

510

REN REN1 REN2 REN3 REN4

500

-50 -30 -10 10 30 50 70 90 110 130

Temperature (°C)

Figure 1. Quiescent Current (Shunt Reference Disabled) vs. Temperature

Figure 2. EN, EN1, EN2, EN3, EN4 Pull Down Resistor vs.

Temperature

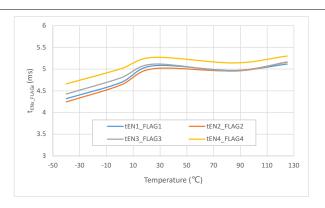

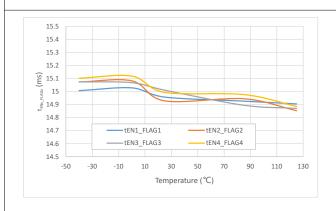

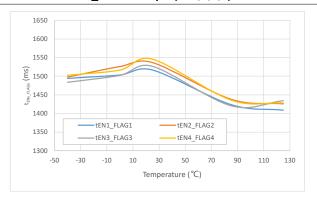

Figure 3. EN1, EN2, EN3 and EN4 Falling Threshold vs.

Temperature

Figure 4. Shunt Ref Output Voltage vs. Output Current

Figure 5. ENx Falling Delay Time vs. Temperature with VCC=5V

Figure 6. FLAGx (x=1,2,3,4) Output Low Voltage vs.

Output Sink Current

www.3peak.com 9 / 20 FA20240601A0

Figure 7. FLAGx (x=1,2,3,4) Output Low Voltage vs. Temperature with VCC=0V and Vbias=1.2V

Figure 8. ENx to FLAGx High Delay vs. Temperature with C\_SETx=330pF (x=1,2,3,4)

Figure 9. ENx to FLAGx High Delay vs. Temperature with C\_SETx=1nF (x=1,2,3,4)

Figure 10. ENx to FLAGx High Delay vs. Temperature with C\_SETx=100nF (x=1,2,3,4)

www.3peak.com 10 / 20 FA20240601A0

### **Detailed Description**

#### Overview

TPK1034 is a low voltage four-channel power sequencer. The power supply range is 2 V to 5.5 V, if the shunt reference structure is enabled, the TPK1034 can sustain up to 22 V supply voltage. Each channel has an independent and adjustable threshold that can monitor voltage down to 0.98 V. If the monitored voltage falls below the threshold, the corresponding output is low. If the monitored voltage rises above the threshold, the output turns high after a capacitor-set delay time, the channel output is open-drain configuration.

With the power monitor function, the TPK1034 can achieve power sequencing control, and the capacitor of each channel can adjust the sequencing timing.

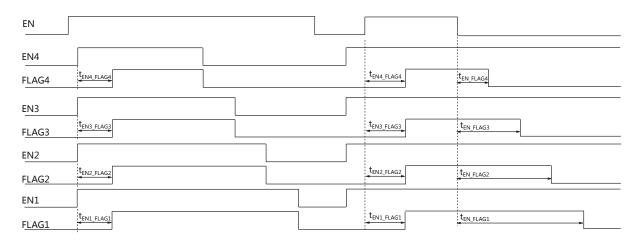

TPK1034 has an overall enable control for all channel outputs. When overall enable is active, each channel can be controlled by corresponding enable. The overall enable control can disable all channel outputs by turning channel output low in a fixed sequence from channel 4 to channel 3, then channel 2 and channel 1. There is a delay time before each channel output low, which can be adjustable by another capacitor.

TPK1034 also includes a power good indication with open-drain active high to indicate all channels output high.

www.3peak.com 11 / 20 FA20240601A0

### **Functional Block Diagram**

Figure 11. Functional Block Diagram

#### **Feature Description**

#### REF\_EN

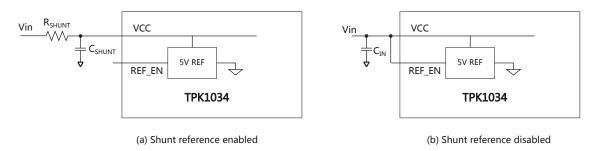

TPK1034 has a shunt reference design to support up to 22V supply voltage. The shunt reference is enabled by leaving REF\_EN not connected, which will be pulled down internally, while an external resistor R<sub>SHUNT</sub> is needed between the external power supply and VCC pin, as shown in below Figure 12(a). The shunt reference is designed at 5V to supply the TPK1034 internal circuit, and can also provide an external load up to 15mA. If the external power supply is 5V or lower, it is not necessary to enable the shunt reference, REF\_EN can be connected to the VCC pin, as shown in Figure 12(b).

www.3peak.com 12 / 20 FA20240601A0

Figure 12. Shunt Reference Circuit

#### **Power Monitor**

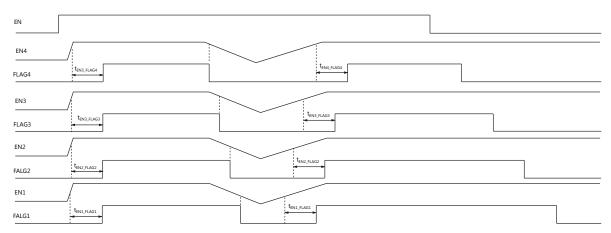

TPK1034 has four power monitor pins: EN1, EN2, EN3, EN4. The internal of each pin is a comparator with a high accurate reference voltage of 0.98 V. With the external divided resistors, each pin can monitor power supply above 0.98V. If the voltage of each pin falls below the falling threshold voltage, V<sub>IN\_ENx</sub>, the corresponding output, FLAGx, is low. In contrast, if the voltage of each pin rises above the rising threshold, the corresponding output turns high after an individual capacitor set delay time. There is overall EN, which should be enabled first, then the four channels can be functional, as the below figure shows.

Figure 13. Power Monitor

#### Sequence

With the independent control of each channel and delay time set by individual capacitors, TPK1034 can achieve flexible power sequence control. The overall EN controls all channels, which should be enabled first, while if EN is low, all channel output turns low with a fixed pattern that from flag4 to flag3, then flag2 and flag1, after a delay time that is programmed by another capacitor. The below figure shows the channel sequence.

www.3peak.com 13 / 20 FA20240601A0

Figure 14. Channel Sequence

#### **Timing**

Each channel output high delay time is programmed by a capacitor for the corresponding channel, the delay time equation is

$$t_X = 14.8945 \text{ms} \times \text{C\_SET}_X (\text{nF}) + 0.075 \text{ms}$$

(1)

where, X is 1, 2, 3, or 4, and C\_SETX is the corresponding capacitor.

The off delay time t5 has the same equation, while the capacitor is that at the C\_SET pin.

#### PG

TPK1034 has power good indication, PG, and output. If all channel outputs, FLAG1 to FLAG4, are high, PG is high, otherwise, PG is low. PG is an open drain configuration, which should be pulled high externally.

#### VCC\_BIAS

The VCC\_BIAS pin can be supplied by a bias voltage before VCC powers on, to avoid FLAGx and PG not providing strong enough pull-down capability only during the VCC power-up period. An external  $1M\Omega$  to  $10M\Omega$  can be connected between VCC\_BIAS and external bias voltage, which is used to limit the current flowing into the VCC\_BIAS pin.

www.3peak.com 14 / 20 FA20240601A0

### **Application and Implementation**

#### Note

Information in the following application sections is not part of the 3PEAK's component specification and 3PEAK does not warrant its accuracy or completeness. 3PEAK's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### **Application Information**

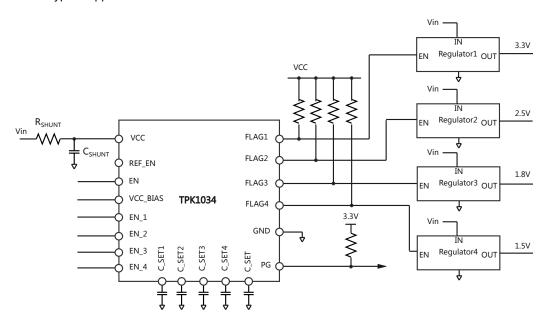

TPK1034 is a four-channel power monitor and sequencer. Each channel has an independent enable control and individual capacitor-set delay time. The overall enabled control of all the channels, and all the channels off sequence delay time can be set by another capacitor. The channel output and PG are open-drain configurations with active high, which need to be pulled up.

#### **Typical Application**

Figure 15 shows the typical application schematic of the TPK1034 with shunt reference enabled

Figure 15. Typical Application Circuit

#### **Shunt Reference Design Guide**

When shunt reference is enabled, VCC is regulated at 5 V if the input voltage is above 5 V. VCC is designed to provide up to 15 mA output capability, R<sub>SHUNT</sub> is needed to limit the output current under different input voltage, C<sub>SHUNT</sub> is needed for VCC regulation stability. Users can refer recommeded values of R<sub>SHUNT</sub> and C<sub>SHUNT</sub> in the below table.

Table 2. R<sub>SHUNT</sub> and C<sub>SHUNT</sub> Guide

| Vin  | Recommended R <sub>SHUNT</sub> at 15mA VCC Output<br>Capability | Recommended C <sub>SHUNT</sub> |

|------|-----------------------------------------------------------------|--------------------------------|

| 5.5V | 30Ω                                                             | 1μF to 10μF                    |

www.3peak.com 15 / 20 FA20240601A0

| 8V  | 190Ω | 1μF to 10μF |

|-----|------|-------------|

| 11V | 390Ω | 1μF to 10μF |

| 20V | 1kΩ  | 1μF to 10μF |

www.3peak.com 16 / 20 FA20240601A0

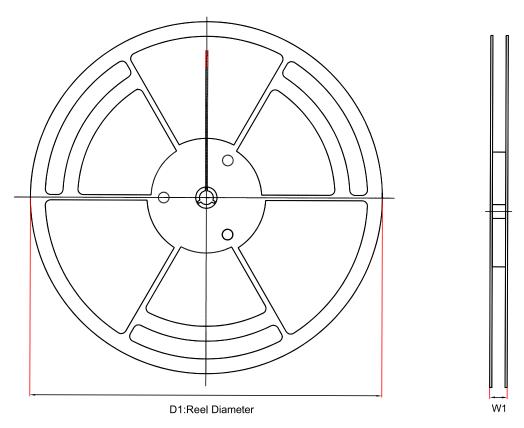

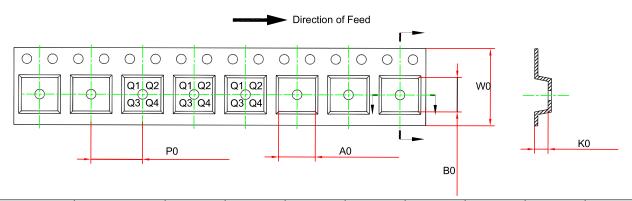

## **Tape and Reel Information**

| Order Number       | Package       | D1 (mm) | W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P0 (mm) | W0 (mm) | Pin1<br>Quadrant |

|--------------------|---------------|---------|---------|---------|---------|---------|---------|---------|------------------|

| TPK1034-<br>QF6R-S | QFN3.5x3.5-20 | 330.0   | 17.6    | 3.8     | 3.8     | 1.1     | 8.0     | 12.0    | Q1               |

www.3peak.com 17 / 20 FA20240601A0

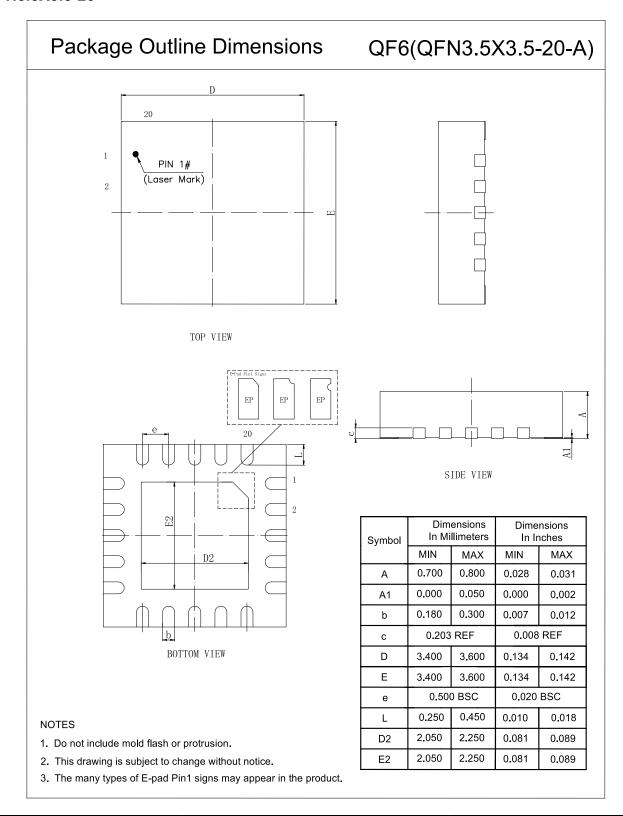

### **Package Outline Dimensions**

#### QFN3.5X3.5-20

### **Order Information**

| Order Number   | Operating Temperature Range | Package       | Marking Information | MSL | Transport Media, Quantity | Eco Plan |  |

|----------------|-----------------------------|---------------|---------------------|-----|---------------------------|----------|--|

| TPK1034-QF6R-S | -40 to 125°C                | QFN3.5x3.5-20 | K1034               | 1   | 4000                      | Green    |  |

**Green**: 3PEAK defines "Green" to mean RoHS compatible and free of halogen substances.

www.3peak.com 19 / 20 FA20240601A0

#### IMPORTANT NOTICE AND DISCLAIMER

Copyright<sup>©</sup> 3PEAK 2012-2024. All rights reserved.

**Trademarks.** Any of the 思瑞浦 or 3PEAK trade names, trademarks, graphic marks, and domain names contained in this document /material are the property of 3PEAK. You may NOT reproduce, modify, publish, transmit or distribute any Trademark without the prior written consent of 3PEAK.

**Performance Information.** Performance tests or performance range contained in this document/material are either results of design simulation or actual tests conducted under designated testing environment. Any variation in testing environment or simulation environment, including but not limited to testing method, testing process or testing temperature, may affect actual performance of the product.

**Disclaimer.** 3PEAK provides technical and reliability data (including data sheets), design resources (including reference designs), application or other design recommendations, networking tools, security information and other resources "As Is". 3PEAK makes no warranty as to the absence of defects, and makes no warranties of any kind, express or implied, including without limitation, implied warranties as to merchantability, fitness for a particular purpose or non-infringement of any third-party's intellectual property rights. Unless otherwise specified in writing, products supplied by 3PEAK are not designed to be used in any life-threatening scenarios, including critical medical applications, automotive safety-critical systems, aviation, aerospace, or any situations where failure could result in bodily harm, loss of life, or significant property damage. 3PEAK disclaims all liability for any such unauthorized use.

www.3peak.com 20 / 20 FA20240601A0