### Features

- ADC Performance:

- Analog Multiplexer with 6-full Differential or 12single Ended Inputs

- Programmable Gain: 1 to 128

- Programmable Data Rates: 2.5 SPS to 8 kSPS

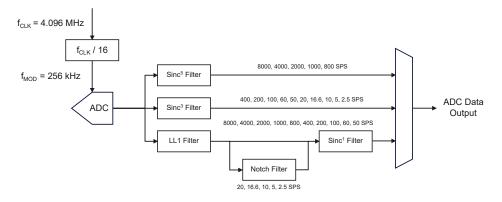

- Digital Filter: Simultaneous 50-Hz and 60-Hz Rejection at ≤ 20 SPS with Low-Latency Digital Filter

- Integrated Functions:

- Dual-Matched Programmable Current Sources for Sensor Excitation: 10 μA to 2000 μA

- Internal Reference: 2.5 V

Internal Oscillator

- Internal Temperature Sensor

- Extended Fault Detection Circuits

- Self-Offset and System Calibration

- GPIO and GPO Pins with External Mux Control

- Digital Interface

- 3-/4- wire SPI-Compatible Interface with CRC Checking

- Digital Supply: 2.7 V to 5 V

- Package: TQFP5x5-32

- Operating Temperature Range: -40°C to +125°C

### Applications

- Process Control: PLC/DCS Modules

- Voltage, Current, Temperature, and Pressure Measurement Flow Meters

- Temperature Controllers

- Medical and Scientific Instrumentation

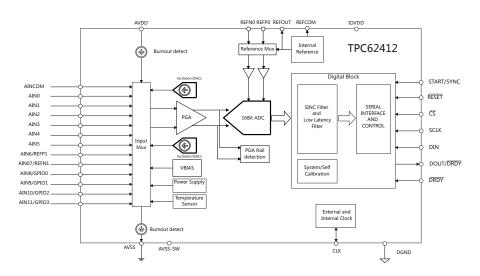

### Description

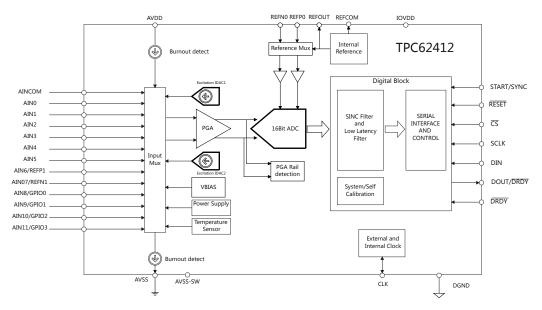

The TPC62412 is a precision 12-channel, multiplexed ADC with integrated PGA and many other features, offering accurate measurement for low-bandwidth input signals, and lower-system cost and component count.

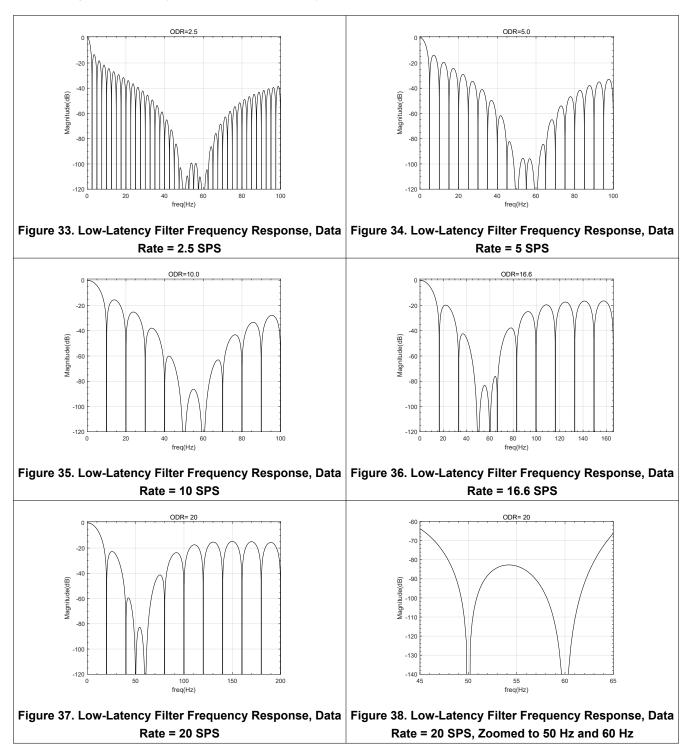

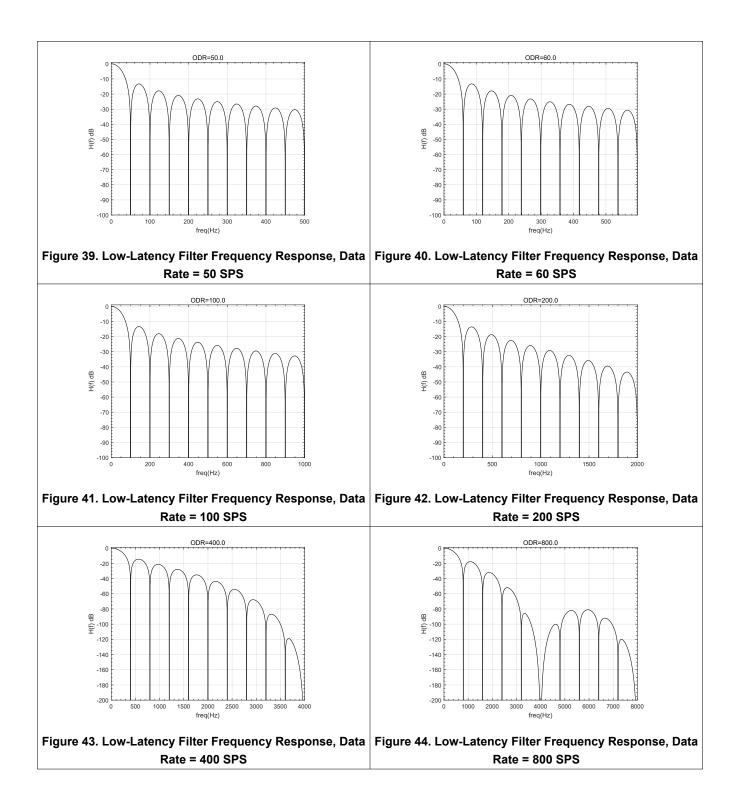

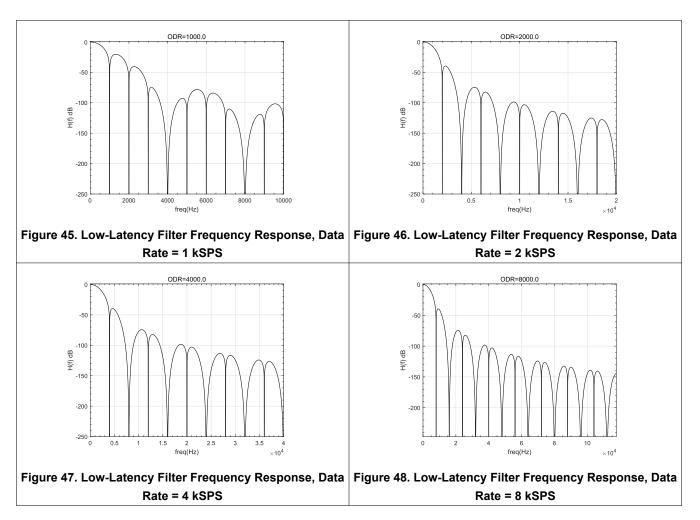

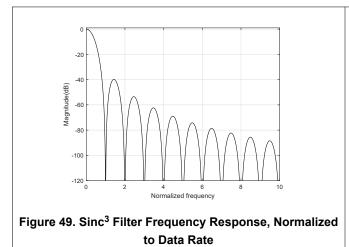

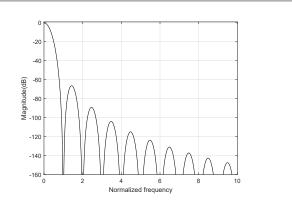

The device has a 16-bit delta-sigma converter, with configurable data rates. There is a sinc5 filter for optimized noise performance, and low-latency filter for fast settling with 50-/60-Hz rejection for noisy industrial environments.

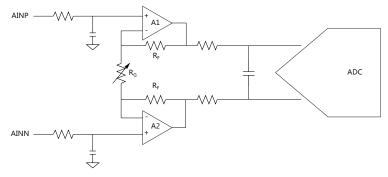

A low-noise programmable gain amplifier provides 1 to 128 gain options to amplify low-level signals.

Additionally, the device integrates a precision 2.5-V bandgap reference and an integrated oscillator.

Two programmable excitation current sources are available for easy RTD biasing for temperature measurement.

Finally, more features such as burn out, CRC, voltage bias, system monitoring, and GPIOs are integrated.

The device is available in the TQFP5X5-32 package.

## **Typical Application Circuit**

### **Table of Contents**

| Features                                | 1  |

|-----------------------------------------|----|

| Applications                            | 1  |

| Description                             | 1  |

| Typical Application Circuit             | 1  |

| Product Family Table                    | 3  |

| Revision History                        |    |

| Pin Configuration and Functions         | 4  |

| Specifications                          | 6  |

| Absolute Maximum Ratings <sup>(1)</sup> | 6  |

| ESD, Electrostatic Discharge Protection | 6  |

| Recommended Operating Conditions        | 7  |

| Thermal Information                     | 7  |

| Electrical Characteristics              | 8  |

| Timing Specifications                   | 14 |

| Timing Diagrams                         | 15 |

| Typical Performance Characteristics     |    |

| Noise Performance                       | 22 |

| Detailed Description                    |    |

| Overview                                |    |

| Functional Block Diagram                |    |

| Feature Description                     |    |

| Device Functional Modes                 |    |

| Programming                             | 53 |

| Register Map                            | 63 |

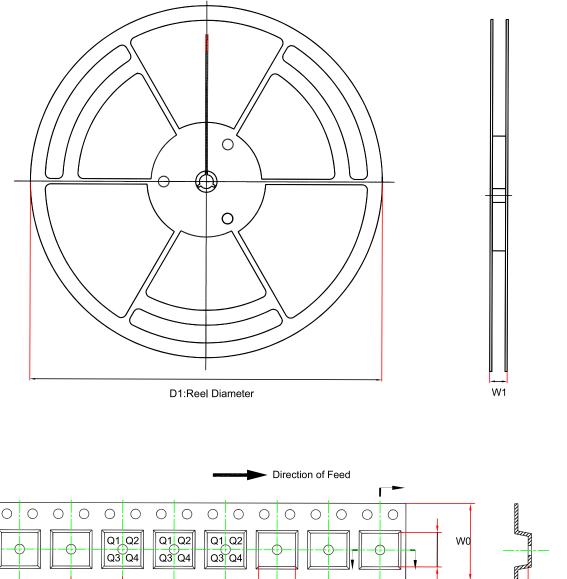

| Tape and Reel Information               | 76 |

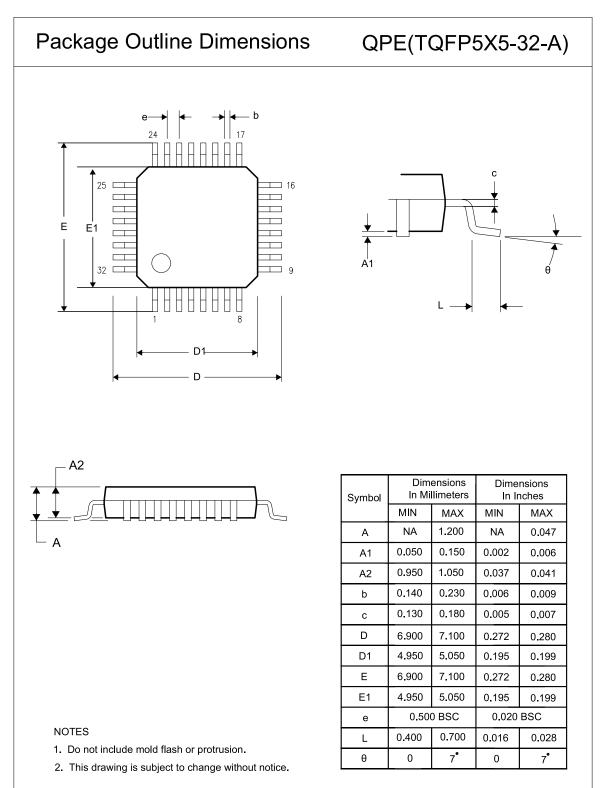

| Package Outline Dimensions              |    |

| TQFP5X5-32                              | 77 |

| Order Information                       |    |

| IMPORTANT NOTICE AND DISCLAIMER         | 79 |

## **Product Family Table**

| Order Number  | ADC resolution | ADC channel | Temperature Range | Package    |  |

|---------------|----------------|-------------|-------------------|------------|--|

| TPC62412-QPER | 16             | 12          | −40°C to 125°C    | TQFP5X5-32 |  |

## **Revision History**

| Date       | Revision | Notes             |

|------------|----------|-------------------|

| 2025-02-10 | Rev.A.0  | Initial released. |

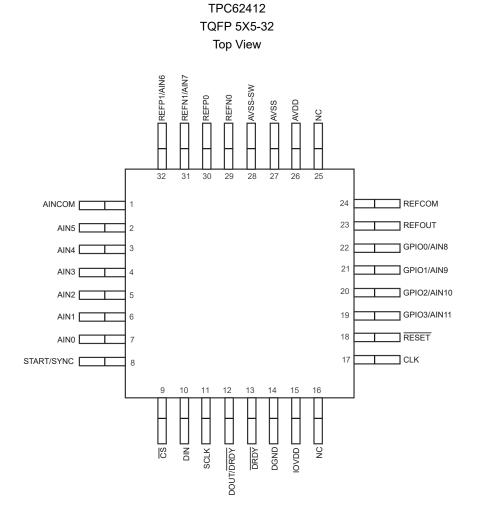

### **Pin Configuration and Functions**

Table 1. Pin Functions

|         | Pin        | Function      | Description (1)                                   |

|---------|------------|---------------|---------------------------------------------------|

| Pin No. | Name       | Function      | Description <sup>(1)</sup>                        |

| 1       | AINCOM     | Analog input  | Common analog input for single-ended measurements |

| 2       | AIN5       | Analog input  | Analog input 5                                    |

| 3       | AIN4       | Analog input  | Analog input 4                                    |

| 4       | AIN3       | Analog input  | Analog input 3                                    |

| 5       | AIN2       | Analog input  | Analog input 2                                    |

| 6       | AIN1       | Analog input  | Analog input 1                                    |

| 7       | AIN0       | Analog input  | Analog input 0                                    |

| 8       | START/SYNC | Digital input | Start conversion                                  |

| 9       | CS         | Digital input | Chip select; active low                           |

| Pin     |             | -                   |                                                                                                                              |

|---------|-------------|---------------------|------------------------------------------------------------------------------------------------------------------------------|

| Pin No. | Name        | Function            | Description <sup>(1)</sup>                                                                                                   |

| 10      | DIN         | Digital input       | Serial data input                                                                                                            |

| 11      | SCLK        | Digital input       | Serial clock input                                                                                                           |

| 12      | DOUT/DRDY   | Digital output      | Serial data output combined with data ready; active low                                                                      |

| 13      | DRDY        | Digital output      | Data ready; active low                                                                                                       |

| 14      | DGND        | Digital ground      | Digital ground                                                                                                               |

| 15      | IOVDD       | Digital supply      | Digital I/O power supply. In case IOVDD is not tied to DVDD, connect a 100-nF (or larger) capacitor to DGND.                 |

| 16      | NC          | _                   | Leave unconnected or connect to AVSS                                                                                         |

| 17      | CLK         | Digital input       | External clock input. Connect to DGND to use the internal oscillator.                                                        |

| 18      | RESET       | Digital input       | Reset; active low                                                                                                            |

| 19      | GPIO3/AIN11 | Analog input/output | General-purpose I/O <sup>(2)</sup> ; analog input 11                                                                         |

| 20      | GPIO2/AIN10 | Analog input/output | General-purpose I/O <sup>(2)</sup> ; analog input 10                                                                         |

| 21      | GPIO1/AIN9  | Analog input/output | General-purpose I/O <sup>(2)</sup> ; analog input 9                                                                          |

| 22      | GPIO0/AIN8  | Analog input/output | General-purpose I/O <sup>(2)</sup> ; analog input 8                                                                          |

| 23      | REFOUT      | Analog output       | Positive voltage reference output. Connect a 1-µF to 47-µF capacitor to REFCOM if the internal voltage reference is enabled. |

| 24      | REFCOM      | Analog output       | Negative voltage reference output. Connect to AVSS.                                                                          |

| 25      | NC          | _                   | Leave unconnected or connect to AVSS                                                                                         |

| 26      | AVDD        | Analog supply       | Positive analog power supply. Connect a 330-nF (or larger) capacitor to AVSS.                                                |

| 27      | AVSS        | Analog supply       | Negative analog power supply                                                                                                 |

| 28      | AVSS-SW     | Analog supply       | Negative analog power supply; low-side switch.<br>Connect to AVSS.                                                           |

| 29      | REFN0       | Analog input        | Negative external reference input 0                                                                                          |

| 30      | REFP0       | Analog input        | Positive external reference input 0                                                                                          |

| 31      | REFN1/AIN7  | Analog input        | Negative external reference input 1; analog input 7                                                                          |

| 32      | REFP1/AIN6  | Analog input        | Positive external reference input 1; analog input 6                                                                          |

(1) General-purpose inputs and outputs use logic levels based on the analog supply.

### **Specifications**

#### Absolute Maximum Ratings <sup>(1)</sup>

|                       |                                                     | Min        | Мах         | Unit |

|-----------------------|-----------------------------------------------------|------------|-------------|------|

|                       | AVDD to AVSS                                        | -0.3       | 5.5         | V    |

| Cumple ( ) (alta na   | AVSS to DGND                                        | -2.8       | 0.3         | V    |

| Supply Voltage        | DVDD to DGND                                        | -0.3       | 3.9         | V    |

|                       | IOVDD to DGND                                       | -0.3       | 5.5         | V    |

| Analog Input Voltage  | AINx, GPIOx, REFPx, REFNx, REFCOM                   | AVSS - 0.3 | AVDD + 0.3  | V    |

| Digital Input Voltage | CS, SCLK, DIN, DOUT/DRDY, DRDY, START, RESET, CLK   | DGND - 0.3 | IOVDD + 0.3 | V    |

| la mut Currant        | Continuous, AVSS-SW, REFN0, REFOUT                  | -100       | 100         | mA   |

| Input Current         | Continuous, all other pins except power-supply pins | -10        | 10          | mA   |

| T <sub>A</sub>        | Operating Temperature Range                         | -40        | 125         | °C   |

| TJ                    | Maximum Junction Temperature                        |            | 150         | °C   |

| T <sub>STG</sub>      | Storage Temperature Range                           | -65        | 150         | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

### ESD, Electrostatic Discharge Protection

| Symbol | Parameter                | Condition                             | Minimum Level | Unit |

|--------|--------------------------|---------------------------------------|---------------|------|

| HBM    | Human Body Model ESD     | ANSI/ESDA/JEDEC JS-001 (1)            | ±7000         | V    |

| CDM    | Charged Device Model ESD | ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ±1500         | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **Recommended Operating Conditions**

|                       | Parameter                              | Test Conditions                                         | Min                      | Тур   | Мах                      | Units |

|-----------------------|----------------------------------------|---------------------------------------------------------|--------------------------|-------|--------------------------|-------|

| Power Su              | ıpply                                  | 1                                                       | ГП                       |       | I                        |       |

|                       |                                        | AVDD to AVSS                                            | 3                        |       | 5.5                      | V     |

| AVDD                  | Analog Power Supply                    | AVSS to DGND                                            | -2.5                     | 0     | 0                        | V     |

|                       |                                        | AVDD to DGND                                            | 1.5                      |       | 5.5                      | V     |

|                       |                                        | IOVDD to DGND                                           | 2                        |       | 5.5                      | V     |

| DVDD                  | Digital Power Supply                   | IOVDD to AVSS                                           | 2                        |       | 8                        | V     |

|                       |                                        | PGA Bypassed                                            | AVSS - 0.05              |       | AVDD + 0.05              | V     |

| V <sub>(AINx)</sub>   | Absolute Input Voltage                 | PGA Enabled,<br>Gain = 1 to 8                           |                          |       |                          | V     |

|                       |                                        | PGA Enabled,<br>Gain =16 to 128                         | AVSS + 0.15              |       | AVDD - 0.35              | V     |

| VIN                   | Differential Input Voltage             | V <sub>IN</sub> = V <sub>AINP</sub> - V <sub>AINN</sub> | −V <sub>REF</sub> /Gain  |       | V <sub>REF</sub> /Gain   | V     |

| Voltage F             | Reference Input                        | ·                                                       |                          |       | - :                      |       |

| V <sub>REF</sub>      | Absolute Differential Input<br>Voltage |                                                         | 1                        |       | AVDD - AVSS              | V     |

| .,                    | Absolute Negative Reference            | REF BUF Bypassed                                        | AVSS                     |       | V <sub>(REFPx)</sub> - 1 | V     |

| V <sub>(REFNx)</sub>  | Voltage                                | REF BUF Enable                                          | AVSS + 0.5               |       | V <sub>(REFPx)</sub> – 1 | V     |

| .,                    | Absolute Positive Reference            | REF BUF Bypass                                          | V <sub>(REFNx)</sub> + 1 |       | AVDD + 0.05              | V     |

| V <sub>(RFEFPx)</sub> | Voltage                                | REF BUF Enable                                          | V <sub>(REFNx)</sub> + 1 |       | AVDD - 0.5               | V     |

| External              | Clock Source                           | ·                                                       |                          |       |                          |       |

| f <sub>CLK</sub>      | External Clock Frequency               |                                                         | 2                        | 4.096 | 4.5                      | MHz   |

|                       | Duty Cycle                             |                                                         | 40                       | 50    | 60                       | %     |

| Internal C            | Clock Source                           |                                                         |                          |       |                          |       |

| f <sub>CLK</sub>      | Clock Frequency                        |                                                         |                          | 4.096 |                          | MHz   |

|                       | Accuracy                               |                                                         | -2                       |       | 2                        | %     |

| General I             | Purpose Inputs                         |                                                         |                          |       |                          |       |

|                       | GPIO Input Voltage                     |                                                         | AVSS - 0.05              |       | AVDD + 0.05              | V     |

| Digital In            | puts                                   |                                                         |                          |       |                          |       |

|                       | Digital Input Voltage                  |                                                         | DGND                     |       | IOVDD                    | V     |

| Temperat              | ture Range                             |                                                         |                          |       |                          |       |

| TJ                    | Operating Junction Temperature         |                                                         | -40                      |       | 125                      | °C    |

### **Thermal Information**

| Package Type | θ <sub>JA</sub> | θ <sub>JC(top)</sub> | θ <sub>JB</sub> | Unit |

|--------------|-----------------|----------------------|-----------------|------|

| TQFP5X5-32   | 70.56           | 19.2                 | 45.07           | °C/W |

#### **Electrical Characteristics**

All minimum/maximum specifications at  $T_A = -40^{\circ}$ C to  $+125^{\circ}$ C and all typical specifications at  $T_A = 25^{\circ}$ C,

AVDD = 3.0 V to 5.5 V, IOVDD = 3.3 V, AVSS = 0 V, unless otherwise noted.

| Parameter            | Test Conditions                                                                   | Min   | Тур                            | Мах | Units              |

|----------------------|-----------------------------------------------------------------------------------|-------|--------------------------------|-----|--------------------|

| Analog Input         |                                                                                   |       |                                |     |                    |

|                      | AVDD = 5.5 V, PGA Gain = 1<br>T <sub>A</sub> = $-40^{\circ}$ C to $+85^{\circ}$ C | 1.834 | 3.427                          |     |                    |

|                      | AVDD = 5.5 V, PGA Gain = 2<br>T <sub>A</sub> = $-40^{\circ}$ C to $+85^{\circ}$ C | 1.316 | 2.621                          |     |                    |

|                      | AVDD = 5.5 V, PGA Gain = 4<br>$T_A = -40^{\circ}$ C to +85°C                      | 0.811 | 1.417                          |     |                    |

| Differential Input   | AVDD = 5.5 V, PGA Gain = 8<br>$T_A = -40^{\circ}$ C to +85°C                      | 0.500 | 0.798                          |     | 00                 |

| Impedance            | AVDD = 5.5 V, PGA Gain = 16<br>$T_A = -40^{\circ}$ C to +85°C                     | 0.272 | 0.426                          |     | GΩ                 |

|                      | AVDD = 5.5 V, PGA Gain = 32<br>$T_A = -40^{\circ}$ C to +85°C                     | 0.157 | 0.231                          |     |                    |

|                      | AVDD = 5.5 V, PGA Gain = 64<br>$T_A = -40^{\circ}$ C to +85°C                     | 0.129 | 0.206                          |     |                    |

|                      | AVDD = 5.5 V, PGA Gain = 128<br>$T_A = -40^{\circ}$ C to +85°C                    | 0.104 | 0.191                          |     |                    |

| PGA                  |                                                                                   |       |                                |     |                    |

| Gain Settings        |                                                                                   |       | 1, 2, 4, 8, 16,<br>32, 64, 128 |     |                    |

| Startup Time         | Enabling the PGA in conversion mode                                               |       | 190                            |     | μs                 |

| System Performance   |                                                                                   |       |                                |     |                    |

| Resolution           |                                                                                   | 16    |                                |     | Bits               |

| Data Rate            |                                                                                   | 2.5   |                                | 8 k | SPS                |

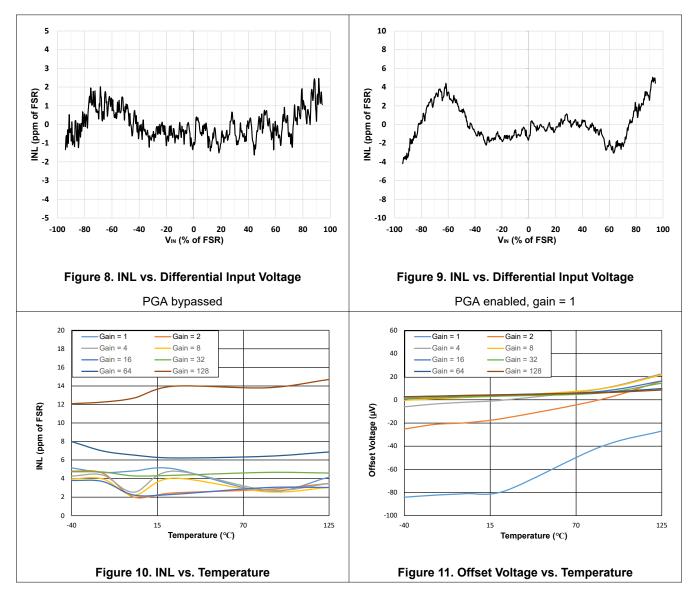

|                      | PGA bypassed, $T_A = 25^{\circ}C$<br>V <sub>CM</sub> = AVDD/2                     |       | 2.5                            | ±10 |                    |

| INL (Best Fit)       | PGA gain = 1 to 8<br>V <sub>CM</sub> = AVDD/2                                     |       | 5                              |     | ppm <sub>FSR</sub> |

|                      | PGA gain = 16 to 128<br>V <sub>CM</sub> = AVDD/2                                  |       | 6                              |     |                    |

|                      | T <sub>A</sub> = 25°C, PGA bypassed                                               | -188  | 78                             | 170 |                    |

|                      | $T_A = 25^{\circ}C$ , PGA enabled, gain = 1                                       | -205  | 81                             | 200 |                    |

| Input Offset Voltage | $T_A = 25^{\circ}C$ , PGA enabled, gain = 2                                       | -100  | 15                             | 100 | μV                 |

|                      | $T_A$ = 25°C, PGA enabled, gain = 4                                               | -50   | 15                             | -50 |                    |

|                      | $T_A = 25^{\circ}C$ , PGA enabled, gain = 8                                       | -30   | 5                              | 30  |                    |

| Parameter        | Test Conditions                                                                  | Min                                   | Тур              | Max          | Units  |

|------------------|----------------------------------------------------------------------------------|---------------------------------------|------------------|--------------|--------|

|                  | $T_A$ = 25°C, PGA enabled, gain = 16                                             | -20                                   | 6                | 20           |        |

|                  | $T_A = 25^{\circ}C$ , PGA enabled,<br>gain = 32 to 128                           | -15                                   | 5                | 15           |        |

|                  | T <sub>A</sub> = 25°C, PGA bypassed,<br>after internal vos calibration           | on the orde                           | er of noisepp at | t the set DR |        |

|                  | $T_A$ = 25°C, PGA enabled, gain = 1 to<br>128, after internal offset calibration | on the order of noisepp at the set DR |                  |              |        |

|                  | T <sub>A</sub> = 25°C, PGA bypassed,<br>global chop enabled                      | -2.3                                  | 0.1              | 2.2          |        |

|                  | $T_A$ = 25°C, PGA enabled, gain = 1, global chop enabled                         | -2.3                                  | 0.1              | 2.2          | - μV   |

|                  | AVDD = 5.5 V, PGA bypassed                                                       |                                       | 21               |              |        |

|                  | AVDD = 5.5 V, PGA Gain = 1<br>$T_A = -40^{\circ}C$ to +85°C                      |                                       | 200              | 715          |        |

|                  | AVDD = 5.5 V, PGA Gain = 2<br>$T_A = -40^{\circ}C$ to +85°C                      |                                       | 82               | 275          |        |

|                  | AVDD = 5.5 V, PGA Gain = 4<br>$T_A = -40^{\circ}C$ to +85°C                      |                                       | 55               | 160          |        |

|                  | AVDD = 5.5 V, PGA Gain = 8<br>$T_A = -40^{\circ}C$ to +85°C                      |                                       | 42               | 105          |        |

| Offset Drift     | AVDD = 5.5 V, PGA Gain = 16<br>$T_A = -40^{\circ}C$ to +85°C                     |                                       | 31               | 75           | nV/°C  |

|                  | AVDD = 5.5 V, PGA Gain = 32<br>$T_A = -40^{\circ}C$ to +85°C                     |                                       | 18               | 55           |        |

|                  | AVDD = 5.5 V, PGA Gain = 64<br>$T_A = -40^{\circ}C$ to +85°C                     |                                       | 17               | 51           |        |

|                  | AVDD = 5.5 V, PGA Gain = 128<br>$T_A = -40^{\circ}C$ to +85°C                    |                                       | 21               | 50           |        |

|                  | AVDD = 5.5 V, PGA bypassed or enable, Global chop                                |                                       | 0.5              |              |        |

|                  | T <sub>A</sub> = 25°C, PGA bypassed                                              | -0.06                                 | 0.01             | 0.06         |        |

|                  | T <sub>A</sub> = 25°C, PGA Gain = 1                                              | -0.06                                 | 0.01             | 0.06         |        |

|                  | T <sub>A</sub> = 25°C, PGA Gain = 2                                              | -0.10                                 | 0.02             | 0.11         |        |

| Gain Error       | T <sub>A</sub> = 25°C, PGA Gain = 4                                              | -0.13                                 | 0.02             | 0.13         |        |

| (Exclude Voltage | T <sub>A</sub> = 25°C, PGA Gain = 8                                              | -0.17                                 | 0.04             | 0.17         | %FSR   |

| Reference Error) | T <sub>A</sub> = 25°C, PGA Gain = 16                                             | -0.17                                 | 0.03             | 0.17         |        |

|                  | T <sub>A</sub> = 25°C, PGA Gain = 32                                             | -0.17                                 | 0.04             | 0.18         |        |

|                  | T <sub>A</sub> = 25°C, PGA Gain = 64                                             | -0.17                                 | 0.04             | 0.18         |        |

|                  | T <sub>A</sub> = 25°C, PGA Gain = 128                                            | -0.17                                 | 0.04             | 0.18         |        |

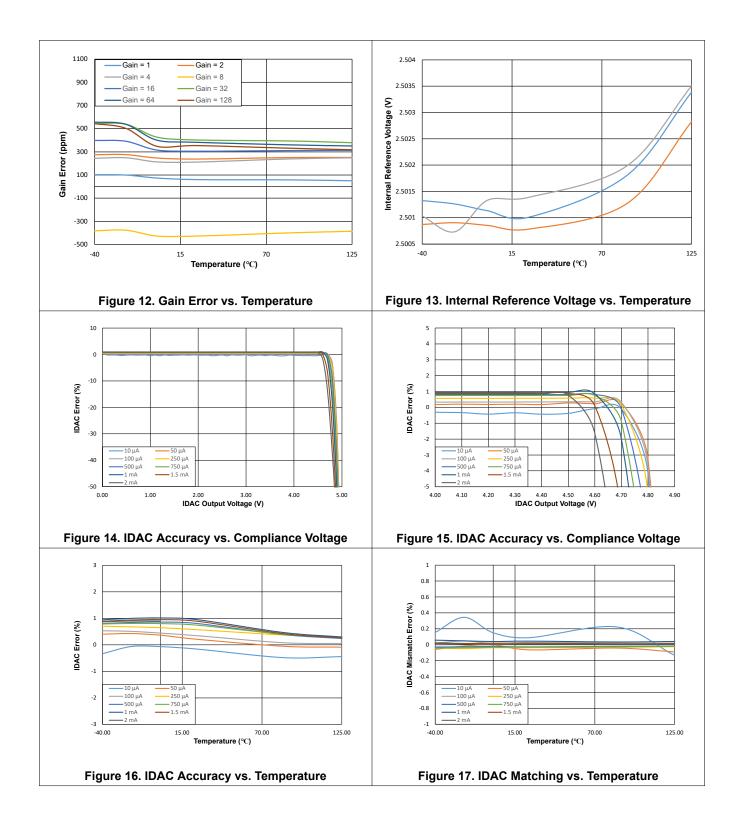

| Gain Drift       | AVDD = 5.5 V, PGA bypassed                                                       |                                       | 0.4              |              | ppm/°C |

| Parameter                     | Test Conditions                                                                                                                               | Min | Тур | Мах | Units             |  |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------------------|--|

|                               | AVDD = 5.5 V, PGA Gain = 1<br>T <sub>A</sub> = $-40^{\circ}$ C to $+85^{\circ}$ C                                                             |     | 0.6 | 1.6 |                   |  |

| (Exclude Voltage              | AVDD = 5.5 V, PGA Gain = 2<br>$T_A = -40^{\circ}$ C to +85°C                                                                                  |     | 0.5 | 1.3 |                   |  |

|                               | AVDD = 5.5 V, PGA Gain = 4<br>T <sub>A</sub> = -40°C to +85°C                                                                                 |     | 0.6 | 1.6 |                   |  |

|                               | AVDD = 5.5 V, PGA Gain = 8<br>T <sub>A</sub> = -40°C to +85°C                                                                                 |     | 0.5 | 1.5 |                   |  |

| Reference Error)              | AVDD = 5.5 V, PGA Gain = 16<br>$T_A = -40^{\circ}$ C to +85°C                                                                                 |     | 0.8 | 2.4 |                   |  |

|                               | AVDD = 5.5 V, PGA Gain = 32<br>$T_A = -40^{\circ}$ C to +85°C                                                                                 |     | 1.3 | 3.5 |                   |  |

|                               | AVDD = 5.5 V, PGA Gain = 64<br>$T_A = -40^{\circ}$ C to +85°C                                                                                 |     | 1.4 | 3.8 |                   |  |

|                               | AVDD = 5.5 V, PGA Gain = 128<br>$T_A = -40^{\circ}$ C to +85°C                                                                                |     | 1.5 | 4.4 |                   |  |

| Noise (Input-referred)        | PGA Gain = 128, DR = 2.5 SPS,<br>Sinc <sup>3</sup> filter                                                                                     |     | 60  |     | nV <sub>RMS</sub> |  |

|                               | $f_{IN}$ = 50 Hz or 60 Hz (±1 Hz),<br>DR = 10 SPS, Sinc <sup>3</sup> filter                                                                   |     | 88  |     |                   |  |

|                               | $f_{IN}$ = 50 Hz or 60 Hz (±1 Hz), DR = 10<br>SPS, Sinc <sup>3</sup> filter, external $f_{CLK}$ = 4.096<br>MHz                                |     | 102 |     |                   |  |

|                               | $f_{IN}$ = 50 Hz or 60 Hz (±1 Hz),<br>DR = 20 SPS, low-latency filter                                                                         |     | 79  |     |                   |  |

| NMRR<br>Normal-mode Rejection | $f_{IN}$ = 50 Hz or 60 Hz (±1 Hz), DR = 20<br>SPS, low-latency filter, external $f_{CLK}$ = 4.096 MHz                                         |     | 94  |     | dB                |  |

| Ratio                         | $f_{IN} = 50 \text{ Hz} (\pm 1 \text{ Hz}), \text{ DR} = 50 \text{ SPS},$<br>Sinc <sup>3</sup> filter                                         |     | 87  |     |                   |  |

|                               | $f_{IN}$ = 50 Hz (±1 Hz), DR = 50 SPS,<br>Sinc <sup>3</sup> filter, external f <sub>CLK</sub> = 4.096 MHz                                     |     | 102 |     |                   |  |

|                               | $f_{IN} = 60 \text{ Hz} (\pm 1 \text{ Hz}), \text{ DR} = 60 \text{ SPS},$<br>Sinc <sup>3</sup> filter                                         |     | 89  |     |                   |  |

|                               | $f_{IN} = 60 \text{ Hz} (\pm 1 \text{ Hz}), \text{ DR} = 60 \text{ SPS},$<br>sinc <sup>3</sup> filter, external $f_{CLK} = 4.096 \text{ MHz}$ |     | 106 |     |                   |  |

|                               | At DC                                                                                                                                         | 104 | 122 |     |                   |  |

| CMRR Common-mode              | $f_{CM}$ = 50 Hz or 60 Hz (±1 Hz),<br>DR = 2.5 SPS to 10 SPS, Sinc <sup>3</sup> filter                                                        |     | 122 |     | dB                |  |

| Rejection Ratio               | $f_{CM}$ = 50 Hz or 60 Hz (±1 Hz), DR = 2.5<br>SPS, 5 SPS, 10 SPS, 20 SPS,<br>low-latency filter                                              |     | 111 |     | – dB              |  |

| Parameter                            | Test Conditions                              | Min   | Тур                                 | Max        | Units            |

|--------------------------------------|----------------------------------------------|-------|-------------------------------------|------------|------------------|

| PSRR Power-supply                    | AVDD at DC                                   | 83    | 95                                  |            |                  |

| Rejection Ratio                      | AVDD at 50 Hz or 60 Hz                       |       | 90                                  |            |                  |

| Voltage Reference Inputs             |                                              |       |                                     | -          |                  |

|                                      | Reference buffers disabled, external         |       | 4.0                                 |            |                  |

| Absolute Input Current               | V <sub>REF</sub> = 2.5 V, REFP1/REFN1 inputs |       | 1.6                                 |            | uA/V             |

|                                      | Reference buffers enabled, external          |       | 0.3                                 |            | nA               |

|                                      | V <sub>REF</sub> = 2.5 V, REFP1/REFN1 inputs |       | 0.0                                 |            |                  |

| Internal Voltage Referenc            | e                                            | 1     | 1                                   | 1          | 1                |

| V <sub>REF</sub>                     | Output Voltage                               |       | 2.5                                 |            | V                |

| Accuracy                             | T <sub>A</sub> = 25°C, AVDD = 3.3 V          | -0.1% | ±0.03%                              | 0.1%       |                  |

| Temperature Drift                    | T <sub>A</sub> = −40 to 125°C                |       | 5                                   |            | ppm/°C           |

| Output Current                       | sink and source                              | -1    |                                     | 1          | mA               |

| Short-circuit Limit Current          | sink or source                               |       | 4                                   |            | mA               |

| PSRR Power-supply<br>Rejection Ratio | AVDD at DC                                   |       | 89                                  |            | dB               |

| Load Regulation                      | Load Current = −1 to 1 mA                    |       | 150                                 |            | µV/mA            |

| Startup Time                         | 1-μF capacitor on REFOUT,<br>0.001% settling |       | 2                                   |            | ms               |

| Capacitive Load Stability (1)        | Capacitor on REFOUT                          | 1     |                                     | 47         | μF               |

| Reference Noise                      | f =0.1 to 10 Hz,<br>1 μF capacitor on REFOUT |       | 9                                   |            | μV <sub>PP</sub> |

| Internal Oscillator                  |                                              | 1     |                                     | 1          |                  |

|                                      | Frequency                                    |       | 4.096                               |            | MHz              |

| f <sub>CLK</sub>                     | Accuracy                                     | -1.5% |                                     | 1.5%       |                  |

| Excitation Current Source            |                                              |       |                                     |            | 1                |

| Current Setting                      |                                              |       | , 50, 100, 250,<br>), 1000, 1500, 2 |            | μΑ               |

|                                      | 10 μA to 750 μA, 0.1% deviation              | AVSS  |                                     | AVDD - 0.4 | V                |

| Compliance Voltage                   | 1 mA to 2 mA, 0.1% deviation                 | AVSS  |                                     | AVDD - 0.6 | V                |

|                                      | T <sub>A</sub> = 25°C, 10 μA to 100 μA       | -5%   | ±0.7%                               | 5%         |                  |

| Accuracy (Each IDAC)                 | $T_A = 25^{\circ}C$ , 250 µA to 2 mA         | -3%   | ±0.5%                               | 3%         |                  |

|                                      | $T_A = 25^{\circ}C$ , 10 µA to 100 µA        |       | 0.15%                               | 0.80%      |                  |

| Current Mismatch                     | T <sub>A</sub> = 25°C, 250 μA to 750 μA      |       | 0.10%                               | 0.60%      |                  |

| betwewn IDACs                        | $T_A = 25^{\circ}$ C, 1 mA to 2 mA           |       | 0.07%                               | 0.40%      |                  |

| Temperature Drift                    | 10 µA to 750 µA                              |       | 20                                  |            |                  |

| (Each IDAC)                          | 1 m to 2 mA                                  |       | 10                                  |            | ppm/°C           |

|                                      | 10 µA to 100 µA                              |       |                                     |            |                  |

| Temperature Drift                    |                                              |       | 5                                   |            | ppm/°C           |

| Parameter                  | Test Conditions                                                                | Min         | Тур                        | Max         | Units    |

|----------------------------|--------------------------------------------------------------------------------|-------------|----------------------------|-------------|----------|

| Startup Time               |                                                                                |             | 25                         |             | μs       |

| BIAS Voltage               |                                                                                |             | L                          | 1           | I        |

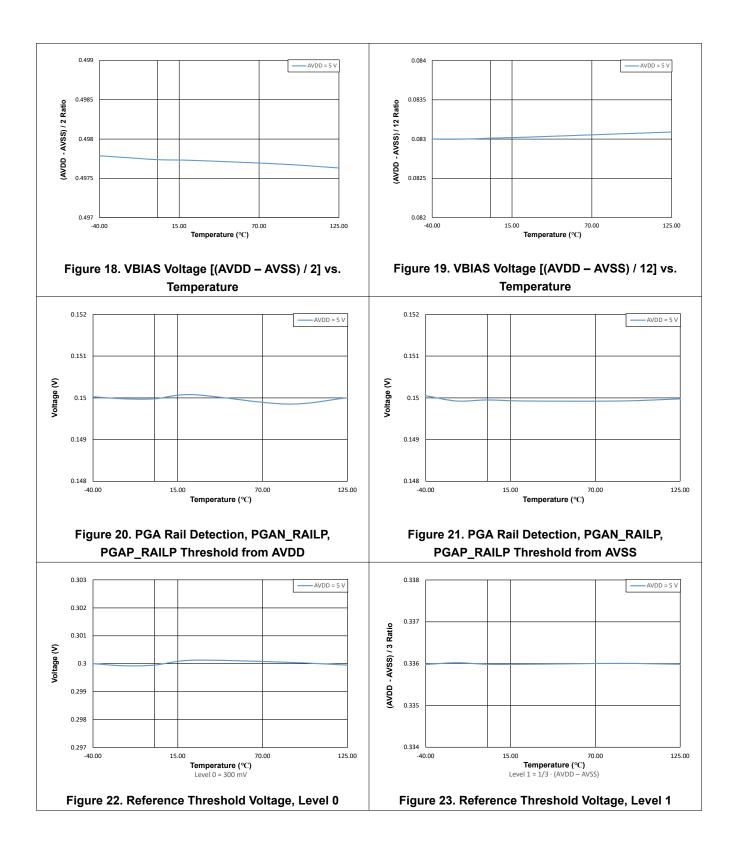

| VBIAS                      | Output Voltage Settings                                                        |             | AVDD+AVSS)/<br>AVDD+AVSS)/ |             | V        |

| Output Impedance           |                                                                                |             | 380                        |             | Ω        |

| Startup Time               | Capacitive load on all selected analog inputs $C_{LOAD}$ = 1 µF, 0.1% settling |             | 2.8                        |             | ms       |

| Burnout Current Source     | s (BOCS)                                                                       |             |                            |             |          |

| Current Setting            |                                                                                |             | 0.2, 1, 10                 |             | μA       |

|                            | 0.2 μΑ                                                                         |             | ±8%                        |             |          |

| Accuracy                   | 1 μΑ                                                                           |             | ±4%                        |             |          |

|                            | 10 µA                                                                          |             | ±2%                        |             |          |

| PGA Rail Detection         |                                                                                |             | L                          | I           | <u> </u> |

| Positive Rail Threshold    | Refer to the output of the PGA                                                 |             | AVDD - 0.15                |             | V        |

| Negative Rail Threshold    | Refer to the output of the PGA                                                 |             | AVSS + 0.15                |             | V        |

| <b>Reference Detection</b> |                                                                                |             |                            |             | 1        |

| Threshold 1                |                                                                                |             | 0.3                        |             | V        |

| Threshold 2                |                                                                                | 1/3         | * (AVDD – AV               | SS)         | V        |

| Threshold 2 Accuracy       | T <sub>A</sub> = 25°C                                                          | -3%         | ±1%                        | 3%          |          |

| Pull-together Resistance   |                                                                                |             | 1                          |             | MΩ       |

| Supply Voltage Monitors    | ;                                                                              |             |                            |             |          |

| _                          | (AVDD – AVSS) / 4 monitor                                                      |             | ±1%                        |             |          |

| Accuracy                   | DVDD / 4 monitor                                                               |             | ±1%                        |             |          |

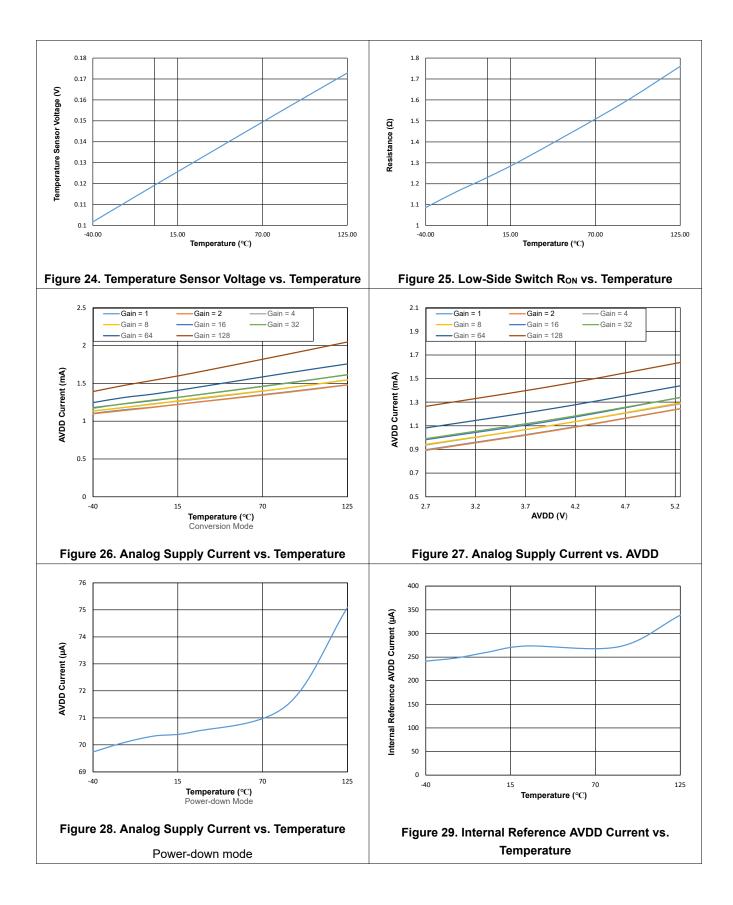

| Temperature Sensor         |                                                                                |             |                            |             |          |

| Output Voltage             | T <sub>A</sub> = 25°C                                                          |             | 130                        |             | mV       |

| Temperature Coefficient    |                                                                                |             | 431                        |             | µV/°C    |

| Accuracy                   |                                                                                |             | ±2                         |             | °C       |

| Low-side Power Switch      |                                                                                |             |                            |             |          |

| R <sub>ON</sub>            | On Resistance                                                                  |             | 1.3                        | 3           | Ω        |

| Current Through Switch     |                                                                                |             | 75                         |             | mA       |

| GPIOs                      |                                                                                |             |                            |             |          |

| V <sub>IL</sub>            | Logic input level, low                                                         | AVSS - 0.05 |                            | 0.3*AVDD    | V        |

| V <sub>IH</sub>            | Logic input level, high                                                        | 0.7*AVDD    |                            | AVDD + 0.05 | V        |

| V <sub>OL</sub>            | Logic output level, low, I <sub>OL</sub> = 1 mA                                | AVSS        |                            | 0.2*AVDD    | V        |

| V <sub>OH</sub>            | Logic output level, high, I <sub>OH</sub> = 1 mA                               | 0.8*AVDD    |                            | AVDD        | V        |

| Digital Interface          |                                                                                |             |                            |             |          |

| VIL                        | Logic input level, low                                                         | DGND        |                            | 0.3*IOVDD   | V        |

| V <sub>IH</sub>            | Logic input level, high                                                        | 0.7*IOVDD   |                            | IOVDD       | V        |

| Parameter                           | Test Conditions                                                                             | Min             | Тур             | Мах              | Units |

|-------------------------------------|---------------------------------------------------------------------------------------------|-----------------|-----------------|------------------|-------|

| V <sub>OL</sub>                     | Logic output level, low, l <sub>OL</sub> = 1 mA                                             | DGND            |                 | 0.2*IOVDD        | V     |

| V <sub>OH</sub>                     | Logic output level, high, I <sub>OH</sub> = 1 mA                                            | 0.8*IOVDD       |                 | IOVDD            | V     |

| Input Current                       | DGND ≤ V <sub>Digital Input</sub> ≤ IOVDD                                                   | -1              |                 | 1                | uA    |

|                                     | ) = 3.3 V, Internal Reference with buffer er<br>, 1k SPS Data Rates, V <sub>IN</sub> = 0 V) | nabled, IDACs [ | Disabled, VBIAS | S Disabled, Flag | IS    |

|                                     | Power-down mode                                                                             |                 | 33              | 50               | uA    |

|                                     | Standby mode, PGA bypassed                                                                  |                 | 0.8             | 1.5              |       |

|                                     | Conversion mode, PGA bypassed                                                               |                 | 0.86            | 1.6              |       |

|                                     | Conversion mode, PGA enabled,<br>gain = 1, 2                                                |                 | 0.88            | 1.6              |       |

| lavdd                               | Conversion mode, PGA enabled,<br>gain = 4, 8                                                |                 | 0.93            | 1.8              | mA    |

|                                     | Conversion mode, PGA enabled,<br>gain = 16, 32                                              |                 | 0.97            | 1.9              |       |

|                                     | Conversion mode, PGA enabled,<br>gain = 64                                                  |                 | 1.08            | 1.99             |       |

|                                     | Conversion mode, PGA enabled,<br>gain = 128                                                 |                 | 1.26            | 2.25             |       |

| P <sub>D</sub><br>Power Dissipation | Conversion mode, PGA enabled,<br>gain = 1                                                   |                 | 3.3             |                  | mW    |

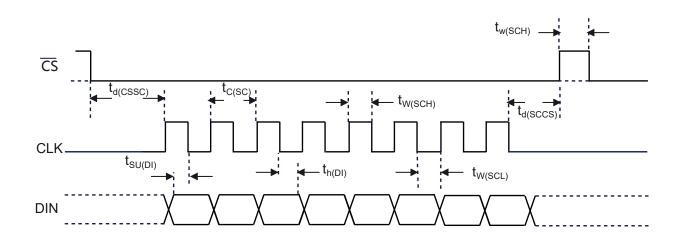

### **Timing Specifications**

#### Timing Requirements <sup>(1)</sup>

All minimum/maximum specifications at  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$  and all typical specifications at  $T_J = 25^{\circ}C$ ,

IOVDD = 2 V to 5.5 V, DOUT = 20 pF to DGND, unless otherwise noted.

|                             | Parameter                                                                                                                                                        | Min  | Max  | Unit <sup>(2)</sup> |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|---------------------|

| Serial In                   | terface                                                                                                                                                          |      |      |                     |

| t <sub>d(CSSC)</sub>        | Delay time, first SCLK rising edge after $\overline{CS}$ falling edge                                                                                            | 20   |      | ns                  |

| t <sub>d(SCCS)</sub>        | Delay time, $\overline{\text{CS}}$ rising edge after final SCLK falling edge                                                                                     | 20   |      | ns                  |

| t <sub>w(CSH)</sub>         | Pulse duration, $\overline{CS}$ high                                                                                                                             | 30   |      | ns                  |

| t <sub>c(SC)</sub>          | SCLK period                                                                                                                                                      | 100  |      | ns                  |

| t <sub>w(SCH)</sub>         | Pulse duration, SCLK high                                                                                                                                        | 40   |      | ns                  |

| t <sub>w(SCL)</sub>         | Pulse duration, SCLK low                                                                                                                                         | 40   |      | ns                  |

| t <sub>su(DI)</sub>         | Setup time, DIN valid before SCLK falling edge                                                                                                                   | 15   |      | ns                  |

| t <sub>h(DI)</sub>          | Hold time, DIN valid after SCLK falling edge                                                                                                                     | 20   |      | ns                  |

| $t_{d(CMD)}$                | Delay time, between bytes or commands                                                                                                                            | 0    |      | ns                  |

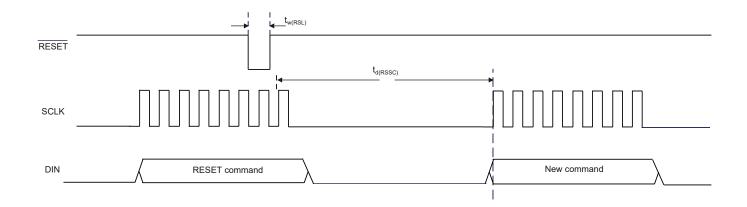

| Reset P                     | in line line line line line line line li                                                                                                                         | ·    |      |                     |

| t <sub>w(RSL)</sub>         | Pulse duration, RESET low                                                                                                                                        | 4    |      | t <sub>CLK</sub>    |

| $t_{\text{d}(\text{RSSC})}$ | Delay time, first SCLK rising edge after $\overline{\text{RESET}}$ rising edge (or 7th SCLK falling edge of RESET command)                                       | 4096 |      | tськ                |

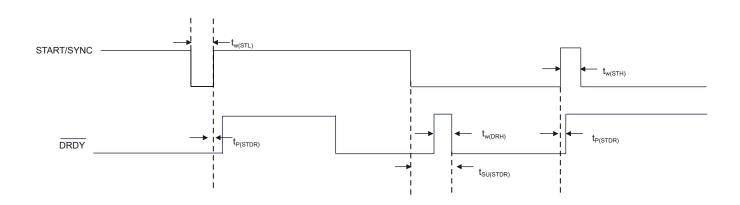

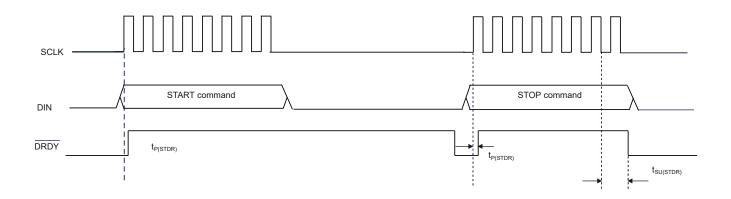

| START/S                     | SYNC Pin                                                                                                                                                         | ·    |      |                     |

| $t_{w(\text{STH})}$         | Pulse duration, START/SYNC high                                                                                                                                  | 4    | 1765 | t <sub>CLK</sub>    |

| t <sub>w(STL)</sub>         | Pulse duration, START/SYNC low                                                                                                                                   | 4    |      | t <sub>CLK</sub>    |

| $t_{su(STDR)}$              | Setup time, START/SYNC falling edge (or 7th SCLK falling edge of STOP command) before DRDY falling edge to stop further conversions (continuous conversion mode) | 32   |      | t <sub>CLK</sub>    |

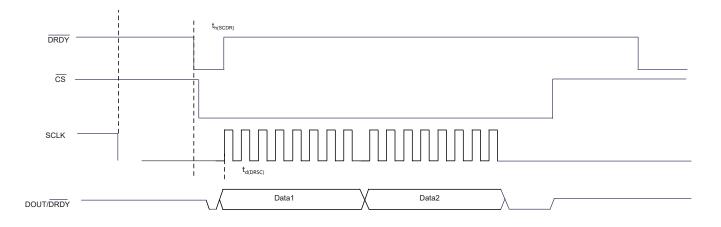

| Reading                     | Conversion Data without Rdata Command                                                                                                                            |      |      |                     |

| $t_{h(SCDR)}$               | Hold time, SCLK low before DRDY falling edge <sup>(3)</sup>                                                                                                      | 28   |      | t <sub>CLK</sub>    |

| t <sub>d(DRSC)</sub>        | Delay time, SCLK rising edge after DRDY falling edge <sup>(3)</sup>                                                                                              | 4    |      | t <sub>CLK</sub>    |

(1) Parameters are guaranteed by design.

(2)  $t_{CLK} = 1 / f_{CLK}$ .

(3) Only applicable when reading data without the RDATA command. All commands can be sent without any SCLK to DRDY signal timing restrictions.

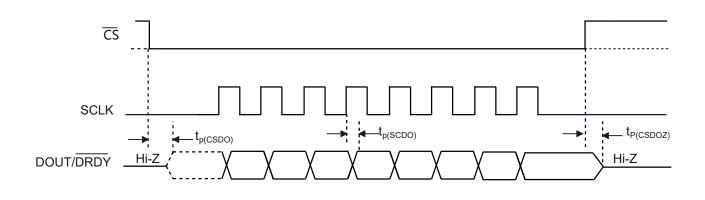

#### Switching Characteristics (1)

All minimum/maximum specifications at  $T_J = -40^{\circ}$ C to  $+125^{\circ}$ C and all typical specifications at  $T_J = 25^{\circ}$ C,

IOVDD = 2 V to 5.5 V, DOUT = 20 pF to DGND, unless otherwise noted.

|                       | Parameter                                                                                                                  | Min             | Тур | Max | Unit <sup>(2)</sup> |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----|---------------------|

| $t_{\text{p(CSDO)}}$  | Propagation delay time, $\overline{\text{CS}}$ falling edge to DOUT driven                                                 | 0               |     | 25  | ns                  |

| t <sub>p(SCDO)</sub>  | Propagation delay time, SCLK rising edge to valid new DOUT                                                                 | 3               |     | 30  | ns                  |

| t <sub>p(CSDOZ)</sub> | Propagation delay time, $\overline{\text{CS}}$ rising edge to DOUT high impedance                                          | 0               |     | 25  | ns                  |

| $t_{\text{p(STDR)}}$  | Propagation delay time, START/SYNC rising edge (or first SCLK rising edge of any command or data read) to DRDY rising edge |                 |     | 2   | t <sub>CLK</sub>    |

| $t_{w(\text{DRH})}$   | Pulse duration, DRDY high                                                                                                  | 24              |     |     | ns                  |

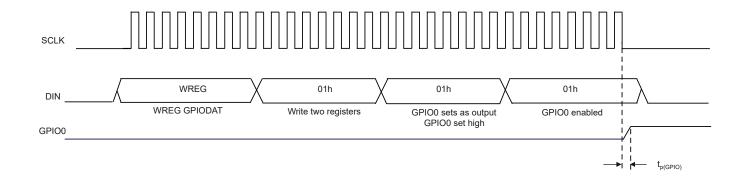

| t <sub>p(GPIO)</sub>  | Propagation delay time, last SCLK falling edge of WREG command to GPIOx output valid                                       | 3               |     | 100 | ns                  |

|                       | SPI timeout per 8 bit <sup>(3)</sup>                                                                                       | 2 <sup>15</sup> |     |     | ns                  |

(1) Parameters are guaranteed by design.

(2) t<sub>CLK</sub> = 1 / f<sub>CLK</sub>.

(3) Only applicable when reading data without the RDATA command. All commands can be sent without any SCLK to DRDY signal timing restrictions.

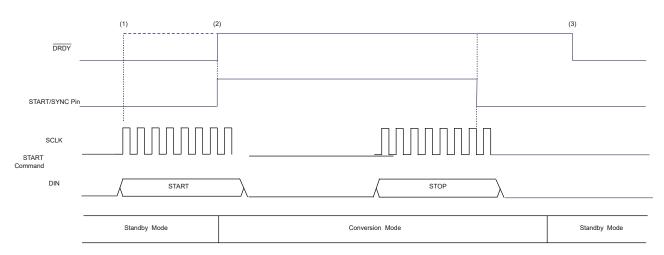

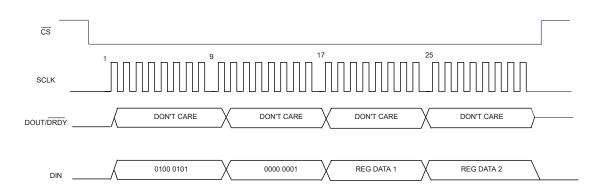

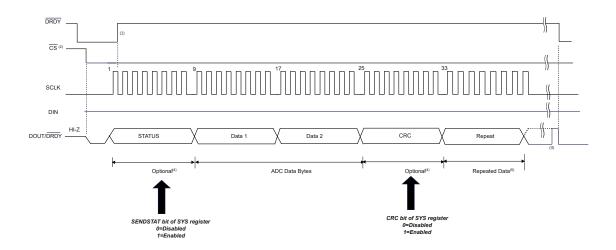

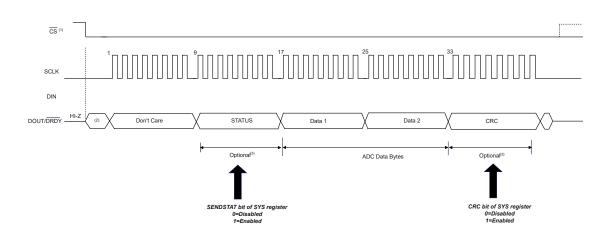

#### **Timing Diagrams**

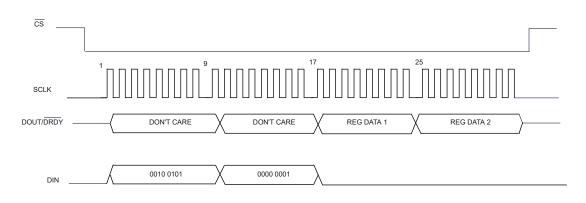

Figure 1. Serial Interface Timing Requirements

Figure 2. Serial Interface Switching Characteristics

Figure 3. RESET Pin and RESET Command Timing Requirements

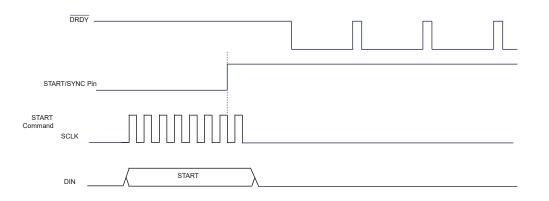

Figure 5. START Command Timing Requirements

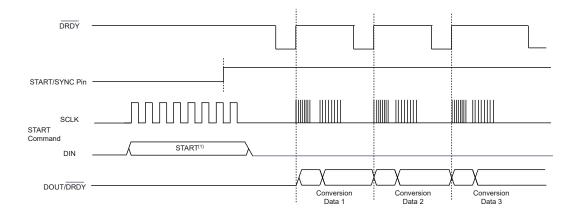

Figure 6. Read Data Direct (without an RDATA Command) Timing Requirements

### **Typical Performance Characteristics**

All test conditions: V<sub>REF</sub> = 2.5 V internal, AVDD = 5 V, IOVDD = 3.3 V, internal 4.096-MHz oscillator, and PGA enabled,

#### $T_A = 25^{\circ}C$ , unless otherwise noted.

## **TPC62412**

#### **Noise Performance**

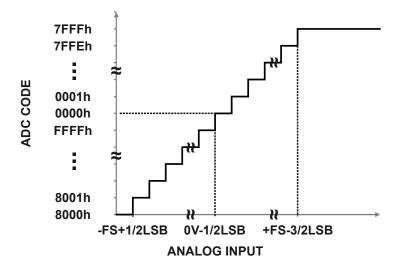

Delta-sigma ( $\Delta\Sigma$ ) analog-to-digital converters (ADCs) are based on the principle of oversampling. The ratio between modulator frequency and output data rate is called the *oversampling ratio* (OSR). By increasing the OSR, and thus reducing the output data rate, the noise performance of the ADC can be optimized. In other words, the input-referred noise drops when reducing the output data rate because more samples of the internal modulator are averaged to yield one conversion result. Increasing the gain also reduces the input-referred noise, which is particularly useful when measuring low-level signals.

Use the following equations to calculate effective resolution and noise-free resolution when using a reference voltage other than 2.5 V.

| Effective Resolution = In[(2 · V <sub>REF</sub> /Gain)/V <sub>RMS - Noise</sub> ]/In(2)   | (1) |

|-------------------------------------------------------------------------------------------|-----|

| Noise – Free Resolution = In[(2 · V <sub>REF</sub> /Gain)/V <sub>PP – Noise</sub> ]/In(2) | (2) |

# Table 2. Noise in $\mu V_{RMS}$ with Sinc Filter, at AVDD = 3.3 V, AVSS = 0 V, PGA Enabled, Global Chop Disabled, and Internal 2.5-V Reference

|                 | Sinc Filter |        |        |        |         |         |         |          |  |  |  |

|-----------------|-------------|--------|--------|--------|---------|---------|---------|----------|--|--|--|

| DATA RATE (SPS) | GAIN=1      | GAIN=2 | GAIN=4 | GAIN=8 | GAIN=16 | GAIN=32 | GAIN=64 | GAIN=128 |  |  |  |

| 2.5             | 76.3        | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 5               | 76.3        | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 10              | 76.3        | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 16.6            | 76.3        | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 20              | 76.3        | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 50              | 76.3        | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 60              | 76.3        | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 100             | 76.3        | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 200             | 76.3        | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 400             | 76.3        | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 800             | 76.3        | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 1000            | 76.3        | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 2000            | 76.3        | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 4000            | 76.3        | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.66     |  |  |  |

| 8000            | 76.3        | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.89     |  |  |  |

|                 | Sinc Filter |        |        |        |         |         |         |          |  |  |

|-----------------|-------------|--------|--------|--------|---------|---------|---------|----------|--|--|

| DATA RATE (SPS) | GAIN=1      | GAIN=2 | GAIN=4 | GAIN=8 | GAIN=16 | GAIN=32 | GAIN=64 | GAIN=128 |  |  |

| 2.5             | 76.3        | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |

| 5               | 76.3        | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |

| 10              | 76.3        | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |

| 16.6            | 76.3        | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |

| 20              | 76.3        | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |

| 50              | 76.3        | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |

| 60              | 76.3        | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |

| 100             | 76.3        | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.73     |  |  |

| 200             | 76.3        | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.97     |  |  |

| 400             | 76.3        | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.5     | 1.42     |  |  |

| 800             | 76.3        | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.9     | 1.72     |  |  |

| 1000            | 76.3        | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 2.0     | 2.04     |  |  |

| 2000            | 29.94       | 38.1   | 19.1   | 9.5    | 4.8     | 3.2     | 3.0     | 2.66     |  |  |

| 4000            | 45.80       | 38.1   | 19.1   | 9.5    | 5.5     | 4.6     | 4.3     | 3.98     |  |  |

| 8000            | 50.94       | 38.1   | 19.1   | 9.5    | 6.7     | 6.4     | 5.7     | 5.35     |  |  |

Table 3. Noise in  $\mu V_{PP}$  with Sinc Filter, at AVDD = 3.3 V, AVSS = 0 V, PGA Enabled, Global Chop Disabled, and Internal 2.5-V Reference

Table 4. Effective Resolution from RMS Noise with Sinc Filter at AVDD = 3.3 V, AVSS = 0 V, PGA Enabled, Global

Chop Disabled, and Internal 2.5-V Reference

|                 | Sinc Filter |        |        |        |         |         |         |          |  |  |  |

|-----------------|-------------|--------|--------|--------|---------|---------|---------|----------|--|--|--|

| DATA RATE (SPS) | GAIN=1      | GAIN=2 | GAIN=4 | GAIN=8 | GAIN=16 | GAIN=32 | GAIN=64 | GAIN=128 |  |  |  |

| 2.5             | 16          | 16     | 16     | 16     | 16      | 16      | 16      | 16       |  |  |  |

| 5               | 16          | 16     | 16     | 16     | 16      | 16      | 16      | 16       |  |  |  |

| 10              | 16          | 16     | 16     | 16     | 16      | 16      | 16      | 16       |  |  |  |

| 16.6            | 16          | 16     | 16     | 16     | 16      | 16      | 16      | 16       |  |  |  |

| 20              | 16          | 16     | 16     | 16     | 16      | 16      | 16      | 16       |  |  |  |

| 50              | 16          | 16     | 16     | 16     | 16      | 16      | 16      | 16       |  |  |  |

| 60              | 16          | 16     | 16     | 16     | 16      | 16      | 16      | 16       |  |  |  |

| 100             | 16          | 16     | 16     | 16     | 16      | 16      | 16      | 16       |  |  |  |

| 200             | 16          | 16     | 16     | 16     | 16      | 16      | 16      | 16       |  |  |  |

| 400             | 16          | 16     | 16     | 16     | 16      | 16      | 16      | 16       |  |  |  |

| 800             | 16          | 16     | 16     | 16     | 16      | 16      | 16      | 16       |  |  |  |

| 1000            | 16          | 16     | 16     | 16     | 16      | 16      | 16      | 16       |  |  |  |

| 2000            | 16          | 16     | 16     | 16     | 16      | 16      | 16      | 16       |  |  |  |

| 4000            | 16          | 16     | 16     | 16     | 16      | 16      | 16      | 16       |  |  |  |

| 8000            | 16          | 16     | 16     | 16     | 16      | 16      | 16      | 15.4     |  |  |  |

|                 | Sinc Filter |        |        |        |         |         |         |          |  |  |  |

|-----------------|-------------|--------|--------|--------|---------|---------|---------|----------|--|--|--|

| DATA RATE (SPS) | GAIN=1      | GAIN=2 | GAIN=4 | GAIN=8 | GAIN=16 | GAIN=32 | GAIN=64 | GAIN=128 |  |  |  |

| 2.5             | 16          | 16     | 16     | 16     | 16      | 16      | 16      | 16       |  |  |  |

| 5               | 16          | 16     | 16     | 16     | 16      | 16      | 16      | 16       |  |  |  |

| 10              | 16          | 16     | 16     | 16     | 16      | 16      | 16      | 16       |  |  |  |

| 16.6            | 16          | 16     | 16     | 16     | 16      | 16      | 16      | 16       |  |  |  |

| 20              | 16          | 16     | 16     | 16     | 16      | 16      | 16      | 16       |  |  |  |

| 50              | 16          | 16     | 16     | 16     | 16      | 16      | 16      | 16       |  |  |  |

| 60              | 16          | 16     | 16     | 16     | 16      | 16      | 16      | 16       |  |  |  |

| 100             | 16          | 16     | 16     | 16     | 16      | 16      | 16      | 15.7     |  |  |  |

| 200             | 16          | 16     | 16     | 16     | 16      | 16      | 16      | 15.3     |  |  |  |

| 400             | 16          | 16     | 16     | 16     | 16      | 16      | 15.7    | 14.7     |  |  |  |

| 800             | 16          | 16     | 16     | 16     | 16      | 16      | 15.3    | 14.5     |  |  |  |

| 1000            | 16          | 16     | 16     | 16     | 16      | 16      | 15.2    | 14.2     |  |  |  |

| 2000            | 16          | 16     | 16     | 16     | 16      | 15.6    | 14.7    | 13.8     |  |  |  |

| 4000            | 16          | 16     | 16     | 16     | 15.8    | 15.0    | 14.2    | 13.3     |  |  |  |

| 8000            | 16          | 16     | 16     | 16     | 15.5    | 14.6    | 13.7    | 12.8     |  |  |  |

Table 5. Noise-Free Resolution from Peak-to-Peak Noise with Sinc Filter at AVDD = 3.3 V, AVSS = 0 V, PGA Enabled,Global Chop Disabled, and Internal 2.5-V Reference

Table 6. Noise in µV<sub>RMS</sub> with Low-Latency Filter, at AVDD = 3.3 V, AVSS = 0 V, PGA Enabled, Global Chop Disabled, and Internal 2.5-V Reference

|                 | Low-Latency Filter |        |        |        |         |         |         |          |  |  |  |

|-----------------|--------------------|--------|--------|--------|---------|---------|---------|----------|--|--|--|

| DATA RATE (SPS) | GAIN=1             | GAIN=2 | GAIN=4 | GAIN=8 | GAIN=16 | GAIN=32 | GAIN=64 | GAIN=128 |  |  |  |

| 2.5             | 76.3               | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 5               | 76.3               | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 10              | 76.3               | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 16.6            | 76.3               | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 20              | 76.3               | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 50              | 76.3               | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 60              | 76.3               | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 100             | 76.3               | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 200             | 76.3               | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 400             | 76.3               | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 800             | 76.3               | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 1000            | 76.3               | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 2000            | 76.3               | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 4000            | 76.3               | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.87     |  |  |  |

| 8000            | 76.3               | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 1.14     |  |  |  |

|                 | Low-Latency Filter |        |        |        |         |         |         |          |  |  |  |

|-----------------|--------------------|--------|--------|--------|---------|---------|---------|----------|--|--|--|

| DATA RATE (SPS) | GAIN=1             | GAIN=2 | GAIN=4 | GAIN=8 | GAIN=16 | GAIN=32 | GAIN=64 | GAIN=128 |  |  |  |

| 2.5             | 76.3               | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 5               | 76.3               | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 10              | 76.3               | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 16.6            | 76.3               | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 20              | 76.3               | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |  |  |  |

| 50              | 76.3               | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.67     |  |  |  |

| 60              | 76.3               | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.71     |  |  |  |

| 100             | 76.3               | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.94     |  |  |  |

| 200             | 76.3               | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.4     | 1.27     |  |  |  |

| 400             | 76.3               | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 2.0     | 1.80     |  |  |  |

| 800             | 76.3               | 38.1   | 19.1   | 9.5    | 4.8     | 2.8     | 2.6     | 2.44     |  |  |  |

| 1000            | 76.3               | 38.1   | 19.1   | 9.5    | 4.8     | 3.2     | 2.9     | 2.84     |  |  |  |

| 2000            | 76.3               | 38.1   | 19.1   | 9.5    | 4.8     | 4.0     | 3.6     | 3.50     |  |  |  |

| 4000            | 76.3               | 62.2   | 21.8   | 13.4   | 7.3     | 6.1     | 5.7     | 5.21     |  |  |  |

| 8000            | 96.0               | 63.4   | 22.8   | 16.0   | 9.9     | 8.0     | 7.7     | 6.82     |  |  |  |

Table 7. Noise in  $\mu V_{PP}$  with Low-Latency Filter, at AVDD = 3.3 V, AVSS = 0 V, PGA Enabled, Global Chop Disabled, and Internal 2.5-V Reference

# Table 8. Effective Resolution from RMS Noise with Low-Latency Filter at AVDD = 3.3 V, AVSS = 0 V, PGA Enabled,Global Chop Disabled, and Internal 2.5-V Reference

|                 |        |        |        | Low-Late | ncy Filter |         |         |          |

|-----------------|--------|--------|--------|----------|------------|---------|---------|----------|

| DATA RATE (SPS) | GAIN=1 | GAIN=2 | GAIN=4 | GAIN=8   | GAIN=16    | GAIN=32 | GAIN=64 | GAIN=128 |

| 2.5             | 16     | 16     | 16     | 16       | 16         | 16      | 16      | 16       |

| 5               | 16     | 16     | 16     | 16       | 16         | 16      | 16      | 16       |

| 10              | 16     | 16     | 16     | 16       | 16         | 16      | 16      | 16       |

| 16.6            | 16     | 16     | 16     | 16       | 16         | 16      | 16      | 16       |

| 20              | 16     | 16     | 16     | 16       | 16         | 16      | 16      | 16       |

| 50              | 16     | 16     | 16     | 16       | 16         | 16      | 16      | 16       |

| 60              | 16     | 16     | 16     | 16       | 16         | 16      | 16      | 16       |

| 100             | 16     | 16     | 16     | 16       | 16         | 16      | 16      | 16       |

| 200             | 16     | 16     | 16     | 16       | 16         | 16      | 16      | 16       |

| 400             | 16     | 16     | 16     | 16       | 16         | 16      | 16      | 16       |

| 800             | 16     | 16     | 16     | 16       | 16         | 16      | 16      | 16       |

| 1000            | 16     | 16     | 16     | 16       | 16         | 16      | 16      | 16       |

| 2000            | 16     | 16     | 16     | 16       | 16         | 16      | 16      | 16       |

| 4000            | 16     | 16     | 16     | 16       | 16         | 16      | 16      | 15.5     |

| 8000            | 16     | 16     | 16     | 16       | 16         | 16      | 16      | 15.1     |

|                 |        |        |        | Low-Late | ency Filter |         |         |          |

|-----------------|--------|--------|--------|----------|-------------|---------|---------|----------|

| DATA RATE (SPS) | GAIN=1 | GAIN=2 | GAIN=4 | GAIN=8   | GAIN=16     | GAIN=32 | GAIN=64 | GAIN=128 |

| 2.5             | 16     | 16     | 16     | 16       | 16          | 16      | 16      | 16       |

| 5               | 16     | 16     | 16     | 16       | 16          | 16      | 16      | 16       |

| 10              | 16     | 16     | 16     | 16       | 16          | 16      | 16      | 16       |

| 16.6            | 16     | 16     | 16     | 16       | 16          | 16      | 16      | 16       |

| 20              | 16     | 16     | 16     | 16       | 16          | 16      | 16      | 16       |

| 50              | 16     | 16     | 16     | 16       | 16          | 16      | 16      | 15.8     |

| 60              | 16     | 16     | 16     | 16       | 16          | 16      | 16      | 15.7     |

| 100             | 16     | 16     | 16     | 16       | 16          | 16      | 16      | 15.3     |

| 200             | 16     | 16     | 16     | 16       | 16          | 16      | 16      | 14.9     |

| 400             | 16     | 16     | 16     | 16       | 16          | 16      | 15.3    | 14.4     |

| 800             | 16     | 16     | 16     | 16       | 16          | 15.8    | 14.9    | 14.0     |

| 1000            | 16     | 16     | 16     | 16       | 16          | 15.6    | 14.7    | 13.7     |

| 2000            | 16     | 16     | 16     | 16       | 16          | 15.3    | 14.4    | 13.4     |

| 4000            | 16     | 15.3   | 15.8   | 15.5     | 15.4        | 14.6    | 13.8    | 12.9     |

| 8000            | 15.7   | 15.3   | 15.7   | 15.3     | 14.9        | 14.3    | 13.3    | 12.5     |

Table 9. Noise-Free Resolution from Peak-to-Peak Noise with Low-Latency Filter at AVDD = 3.3 V, AVSS = 0 V, PGA

Enabled, Global Chop Disabled, and Internal 2.5-V Reference

# Table 10. Noise in $\mu V_{RMS}$ with Sinc Filter, at AVDD = 3.3 V, AVSS = 0 V, PGA Enabled, Global Chop Enabled, and Internal 2.5-V Reference

|                 |        |        |        | Sinc   | Filter  |         |         |          |

|-----------------|--------|--------|--------|--------|---------|---------|---------|----------|

| DATA RATE (SPS) | GAIN=1 | GAIN=2 | GAIN=4 | GAIN=8 | GAIN=16 | GAIN=32 | GAIN=64 | GAIN=128 |

| 2.5             | 76.3   | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |

| 5               | 76.3   | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |

| 10              | 76.3   | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |

| 16.6            | 76.3   | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |

| 20              | 76.3   | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |

| 50              | 76.3   | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |

| 60              | 76.3   | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |

| 100             | 76.3   | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |

| 200             | 76.3   | 38.1   | 19.1   | 9.5    | 4.8     | 2.4     | 1.2     | 0.60     |