# **TPC6160S**

### 16-Bit, 8 kSPS, 4-Channel Sigma-Delta ADC with Internal Reference and Temperature Sensor

### Features

- 16-Bit, 8 kSP, 4-Channel ADC

- Wide Supply Range: 2.7 V to 5.5 V

- Programmable Data Rate:

- 64 SPS to 8 kSPS

- Single-Cycle Settling

- Supporting Four Single-Ended or Two Differential Inputs

- Internal PGA

- Internal Low-Drift Voltage Reference

- Internal Temperature Sensor

- SPI Compatible Interface

- Package: MSOP3x3-10

- Wide Operating Temperature Range: −40°C to +125°C

### Applications

- Current-shunt Measurements

- Voltage Measurements

- Temperature Measurements

### Description

The TPC6160S is a 16-bit Sigma-Delta ADC for high precision and low power measurement. The TPC6160S features an internal programmable gain amplifier (PGA), voltage reference, oscillator, digital filter, and temperature sensor. The device supports a wide range of supply voltages from 2.7 V to 5.5 V.

The data rate of TPC6160S is configurable from 64 SPS to 8 kSPS. The PGA provides input ranges spanning from  $\pm 256$  mV to  $\pm 6.144$  V, with the analog input negative voltage down to -128 mV, which allows both high precision positive and negative signal measurement. The integrated input mux supports two differential pairs or four independent single-ended inputs. The internal temperature sensor can be used for general temperature monitoring or thermal-couple cold-junction compensation.

The TPC6160S can be set in single-shot conversion mode or continuous conversion mode. Single-shot mode features power down after conversion, which is suitable for low-power applications. The digital interface supports communication with various host controllers with SPI-compatible serial interface. The TPC6160S is available in MSOP10 package and operates from  $-40^{\circ}$ C to  $+125^{\circ}$ C.

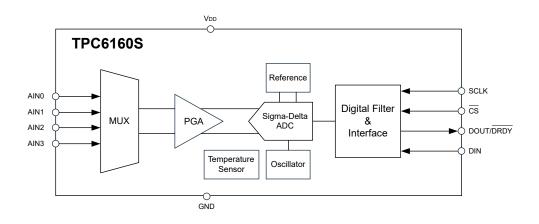

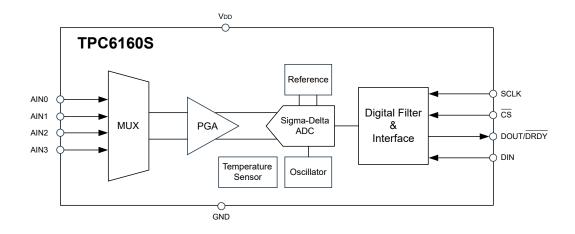

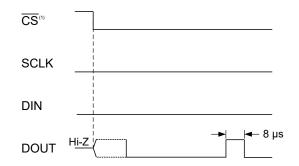

# Functional Block Diagram

### **Table of Contents**

| Features                                | 1  |

|-----------------------------------------|----|

| Applications                            | 1  |

| Description                             | 1  |

| Functional Block Diagram                | 1  |

| Product Family Table                    | 3  |

| Revision History                        | 3  |

| Pin Configuration and Functions         | 4  |

| Specifications                          | 5  |

| Absolute Maximum Ratings <sup>(1)</sup> | 5  |

| ESD, Electrostatic Discharge Protection | 5  |

| Recommended Operating Conditions        | 5  |

| Thermal Information                     | 5  |

| Electrical Characteristics              | 6  |

| Timing Specifications <sup>(1)</sup>    | 8  |

| Typical Performance Characteristics     | 9  |

| Noise Performance                       | 11 |

| Detailed Description                    | 13 |

| Overview                                | 13 |

| Functional Block Diagram                | 13 |

| Feature Description                     | 14 |

| Digital Interface                       | 17 |

| Register Summary                        | 22 |

| Tape and Reel Information               |    |

| Package Outline Dimensions              |    |

| MSOP10                                  | 26 |

| Order Information                       | 27 |

| IMPORTANT NOTICE AND DISCLAIMER         |    |

|                                         |    |

### Product Family Table

| Order Number  | Channels | Resolution | Throughput | Package | Interface | Grade      |

|---------------|----------|------------|------------|---------|-----------|------------|

| TPC6160S-VS2R | 4        | 16 Bits    | 8 kSPS     | MSOP10  | SPI       | Industrial |

### **Revision History**

| Date       | Revision | Notes            |

|------------|----------|------------------|

| 2024-11-13 | Rev.A.0  | Initial release. |

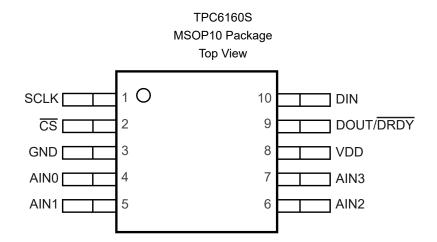

### **Pin Configuration and Functions**

Table 1. Pin Functions: TPC6160S

|     | Pin       | <b>T</b> urner (1)  | Description                                                                                              |  |

|-----|-----------|---------------------|----------------------------------------------------------------------------------------------------------|--|

| No. | Name      | Type <sup>(1)</sup> | Description                                                                                              |  |

| 1   | SCLK      | DI                  | Serial clock input. This pin acts as the serial clock input for data transfers.                          |  |

| 2   | CS        | DI                  | Chip Select. This active low logic input frames the data transfer. If not used, connect this pin to GND. |  |

| 3   | GND       | Р                   | Ground.                                                                                                  |  |

| 4   | AIN0      | AI                  | Analog Input for Channel 0. If not used, float this pin or tie to VDD.                                   |  |

| 5   | AIN1      | AI                  | Analog Input for Channel 1. If not used, float this pin or tie to VDD.                                   |  |

| 6   | AIN2      | AI                  | Analog Input for Channel 2. If not used, float this pin or tie to VDD.                                   |  |

| 7   | AIN3      | AI                  | Analog Input for Channel 3. If not used, float this pin or tie to VDD.                                   |  |

| 8   | VDD       | Р                   | Power supply. Connect a 0.1 $\mu$ F power supply decoupling capacitor to GND.                            |  |

| 9   | DOUT/DRDY | DO                  | Serial data output combined with data ready; active low.                                                 |  |

| 10  | DIN       | DI                  | Serial data input.                                                                                       |  |

(1) AI is analog input, GND is ground, P is power supply, DI is digital input, and DO is digital output.

### **Specifications**

### Absolute Maximum Ratings (1)

|                            | Parameter                        |           |           |    |  |

|----------------------------|----------------------------------|-----------|-----------|----|--|

| Analog Voltage             | Analog Input Voltage to GND      | GND - 0.3 | VDD + 0.3 | V  |  |

| Distict Matter             | Digital Input Voltage to AGND    | GND - 0.3 | VDD + 0.3 | V  |  |

| Digital Voltage            | Digital Output Voltage to AGND   | GND - 0.3 | VDD + 0.3 | V  |  |

| Supply Voltage             | VDD to GND                       | -0.3      | 5.5       | V  |  |

| Input current (continuous) | Any Pin except Power Supply Pins | -10       | 10        | mA |  |

| TJ                         | Maximum Junction Temperature     |           | 150       | °C |  |

| T <sub>A</sub>             | Operating Temperature Range      | -40       | 125       | °C |  |

| T <sub>STG</sub>           | Storage Temperature Range        | -65       | 150       | °C |  |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

### ESD, Electrostatic Discharge Protection

| Symbol | Parameter                | Condition                             | Minimum Level | Unit |

|--------|--------------------------|---------------------------------------|---------------|------|

| НВМ    | Human Body Model ESD     | ANSI/ESDA/JEDEC JS-001 (1)            | ±4            | kV   |

| CDM    | Charged Device Model ESD | ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ±1.5          | kV   |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **Recommended Operating Conditions**

| Parameter             | Parameter                               |                                 |        | Тур | Мах    | Unit |

|-----------------------|-----------------------------------------|---------------------------------|--------|-----|--------|------|

| VDD                   | Power Supply                            | VDD to GND                      | 2.7    |     | 5.5    | V    |

| FSR                   | Full-scale Input Voltage <sup>(1)</sup> | $VIN = V_{(AINP)} - V_{(AINN)}$ | ±0.256 |     | ±6.144 | V    |

| V <sub>(AINx)</sub>   | Absolute Input Voltage                  | Absolute Input Voltage          |        |     | VDD    | V    |

| Digital input Voltage | Absolute Input Voltage                  | Absolute Input Voltage          |        |     | VDD    | V    |

| T <sub>A</sub>        | Operating Ambient Tempera               | ture                            | -40    |     | 125    | °C   |

(1) This parameter expresses the full-scale range of the ADC scaling. No more than VDD + 0.3 V or 5.5 V (whichever is smaller) must be applied to this device.

### **Thermal Information**

| Package Type | θ <sub>JA</sub> | θյς | Unit |

|--------------|-----------------|-----|------|

| MSOP10       | 125             | 48  | °C/W |

### **Electrical Characteristics**

All test conditions: VDD = 3.3 V, data rate = 64 SPS, and FSR =  $\pm 2.048$  V, T<sub>A</sub> = -40 °C to 125 °C, unless otherwise noted.

| Parameter                        | Test                             | Conditions                       | Min                                          | Тур   | Max    | Unit   |

|----------------------------------|----------------------------------|----------------------------------|----------------------------------------------|-------|--------|--------|

| Analog Inputs                    |                                  |                                  |                                              |       | 1      |        |

|                                  | FSR = ±6.144 V <sup>(1)</sup>    |                                  |                                              | 1.3   |        | MΩ     |

|                                  | FSR = ±4.096 V <sup>(1)</sup>    |                                  |                                              | 0.7   |        | MΩ     |

| Common-mode Input                | FSR = ±2.048 V                   |                                  |                                              | 0.45  |        | MΩ     |

| Impedance                        | FSR = ±1.024 V                   |                                  |                                              | 0.47  |        | MΩ     |

|                                  | FSR = ±0.512 V                   |                                  |                                              | 0.26  |        | MΩ     |

|                                  | FSR = ±0.256 V                   |                                  |                                              | 0.25  |        | MΩ     |

|                                  | FSR = ±6.144 V <sup>(1)</sup>    |                                  |                                              | 0.59  |        | MΩ     |

|                                  | FSR = ±4.096 V <sup>(1)</sup>    |                                  |                                              | 0.33  |        | MΩ     |

| Differential Input               | FSR = ±2.048 V                   |                                  |                                              | 0.18  |        | MΩ     |

| Impedance                        | FSR = ±1.024 V                   |                                  |                                              | 0.10  |        | MΩ     |

|                                  | FSR = ±0.512 V                   |                                  |                                              | 0.07  |        | MΩ     |

|                                  | FSR = ±0.256 V                   |                                  |                                              | 0.07  |        | MΩ     |

| System Performance               |                                  |                                  |                                              |       |        |        |

| Resolution                       | NO missing code                  |                                  | 16                                           |       |        | Bits   |

| DR                               | Data rate                        |                                  | 64, 128, 256, 512, 1024, 2000,<br>4000, 8000 |       | SPS    |        |

|                                  | Data rate variation              | All data rates                   | - 10%                                        |       | 10%    |        |

| INL                              | Integral nonlinearity            | DR = 1024 SPS,<br>FSR = ±2.048 V |                                              | ±0.6  | ±1     | LSB    |

| Offset Error                     | FSR = ±2.048 V, differ           | rential inputs                   |                                              | ±1    | ±3.2   | LSB    |

| Offset Drift                     | FSR = ±2.048 V                   |                                  |                                              | 0.01  |        | LSB/°C |

| Offset Power-supply<br>Rejection | FSR = ±2.048 V, DC s             | supply variation                 |                                              | 6     |        | LSB/V  |

| Offset Channel Match             | Match between any tw             | vo inputs                        |                                              | 0.7   |        | LSB    |

| Gain Error                       | FSR = ±2.048 V, T <sub>A</sub> = | 25°C                             |                                              | 0.05% | ±0.15% |        |

|                                  | FSR = ±0.256 V                   |                                  |                                              | 3.7   |        | ppm/°C |

| Gain Drift <sup>(2)</sup>        | FSR = ±2.048 V                   |                                  |                                              | 3.7   | 10     | ppm/°C |

|                                  | FSR = ±6.144 V <sup>(1)</sup>    |                                  | 3.7                                          |       | ppm/°C |        |

|                                  | Gain power-supply rejection      |                                  |                                              | 78    |        | dB     |

| Gain Match                       | Match between any two gains      |                                  |                                              | 0.05% | 0.10%  |        |

| Gain Channel Match               | Match between any tw             | vo inputs                        |                                              | 0.01% | 0.10%  |        |

|                                  | Common-mode                      | At DC, FSR = ±0.256 V            |                                              | 126   |        | dB     |

| CMRR                             | rejection ratio                  | At DC, FSR = ±2.048 V            |                                              | 115   |        | dB     |

| Parameter              | Test C                          | Conditions                           | Min       | Тур     | Мах       | Unit |

|------------------------|---------------------------------|--------------------------------------|-----------|---------|-----------|------|

|                        |                                 | At DC, FSR = ±6.144 V <sup>(1)</sup> |           | 108     |           | dB   |

|                        |                                 | f <sub>см</sub> = 50 Hz, DR = 1 kSPS |           | 114     |           | dB   |

|                        |                                 | f <sub>см</sub> = 60 Hz, DR = 1 kSPS |           | 113     |           | dB   |

| Temperature Sensor     |                                 | ·                                    |           |         |           |      |

| Temperature Range      |                                 |                                      | -40       |         | 125       | °C   |

| Temperature Resolution | 14-bit                          |                                      |           | 0.03125 |           |      |

|                        | $T_{A} = -40^{\circ}C$ to 125°C |                                      |           | ±3      |           | °C   |

| Accuracy               | vs supply                       |                                      |           | ±1      |           | °C/V |

| Digital Input/Outputs  |                                 |                                      |           |         |           |      |

| V <sub>IH</sub>        | High-level input voltage        | e                                    | 0.7 x VDD |         | VDD       | V    |

| VIL                    | Low-level input voltage         | )                                    | GND       |         | 0.2 x VDD | V    |

| Ін                     | Input leakage, high             | V <sub>IH</sub> = 5.5 V              | -10       |         | 10        | μA   |

| IL .                   | Input leakage, low              | V <sub>IL</sub> = GND                | -10       |         | 10        | μA   |

| Digital Output         |                                 |                                      |           |         | 1 1       |      |

| Voн                    | ISOURCE = 1 mA                  |                                      | 0.8 x VDD |         |           | V    |

| V <sub>OL</sub>        | I <sub>SINK</sub> = 1 mA        |                                      | GND       |         | 0.2 x VDD | V    |

| Power Supply           |                                 |                                      |           |         | 1 1       |      |

|                        |                                 | Power-down, T <sub>A</sub> = 25°C    |           | 4.6     | 7         | μA   |

|                        |                                 | Power-down                           |           | 5.3     | 10        | μA   |

| Ivdd                   | Supply current                  | Operating, $T_A = 25^{\circ}C$       |           | 4.2     | 5         | mA   |

|                        |                                 | Operating                            |           | 4.2     | 5.5       | mA   |

| P <sub>D</sub>         | Power dissipation               | VDD = 3.3 V                          |           | 14      | 20        | mW   |

| Temperature Range      | Specified performance           |                                      | -40       |         | +125      | °C   |

(1) This parameter expresses the full-scale range of the ADC scaling. No more than VDD + 0.3 V or 5.5 V (whichever is smaller) must be applied to this device.

(2) Maximum value specified by characterization.

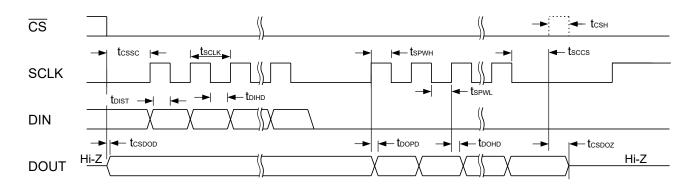

### Timing Specifications <sup>(1)</sup>

All test conditions: VDD = 2.7 V to 5.5 V and  $T_A$  = -40 °C to 125 °C, unless otherwise noted.

| Parameter         | Description                                                                       | Min | Тур | Мах  | Unit |

|-------------------|-----------------------------------------------------------------------------------|-----|-----|------|------|

| t <sub>cssc</sub> | Delay time, $\overline{CS}$ falling edge to first SCLK rising edge <sup>(1)</sup> | 100 |     |      | ns   |

| t <sub>sccs</sub> | Delay time, final SCLK falling edge to $\overline{\text{CS}}$ rising edge         | 100 |     |      | ns   |

| t <sub>CSH</sub>  | Pulse duration, $\overline{CS}$ high                                              | 200 |     |      | ns   |

| t <sub>SCLK</sub> | SCLK period                                                                       | 80  |     |      | ns   |

| t <sub>SPWH</sub> | Pulse duration, SCLK high                                                         | 100 |     |      | ns   |

|                   |                                                                                   | 100 |     |      | ns   |

| t <sub>SPWL</sub> | Pulse duration, SCLK low <sup>(2)</sup>                                           |     |     | 30.8 | ms   |

| t <sub>DIST</sub> | Setup time, DIN valid before SCLK falling edge                                    | 20  |     |      | ns   |

| t <sub>DIHD</sub> | Hold time, DIN valid after SCLK falling edge                                      |     | 700 | 800  | ns   |

| t <sub>DOHD</sub> | Hold time, SCLK rising edge to DOUT invalid                                       | 200 |     |      | ns   |

### Table 2. Serial Interface

(1)  $\overline{CS}$  can be tied low permanently in case the serial bus is not shared with any other device.

(2) Holding SCLK low longer than 30.8 ms resets the SPI interface.

### Figure 1. Serial Interface Timing

| Table 3 | . Switching | <b>Characteristics:</b> | Serial Interface |

|---------|-------------|-------------------------|------------------|

| 10010 0 | · omiconing | 01101001001001          |                  |

| Parameter          | Description                                                                | Test Conditions                            | Min | Тур | Мах | Unit |

|--------------------|----------------------------------------------------------------------------|--------------------------------------------|-----|-----|-----|------|

| tcsdod             | Propagation delay time, $\overline{CS}$ falling edge to DOUT driven        | DOUT load = 20 pF    100 k $\Omega$ to GND |     |     | 100 | ns   |

| tdopd              | Propagation delay time, SCLK rising edge to valid new DOUT                 | DOUT load = 20 pF    100 kΩ to GND         | 0   |     | 50  | ns   |

| t <sub>CSDOZ</sub> | Propagation delay time, $\overline{CS}$ rising edge to DOUT high impedance | DOUT load = 20 pF    100 kΩ to GND         |     |     | 100 | ns   |

(1) Parameters are provided by design simulation.

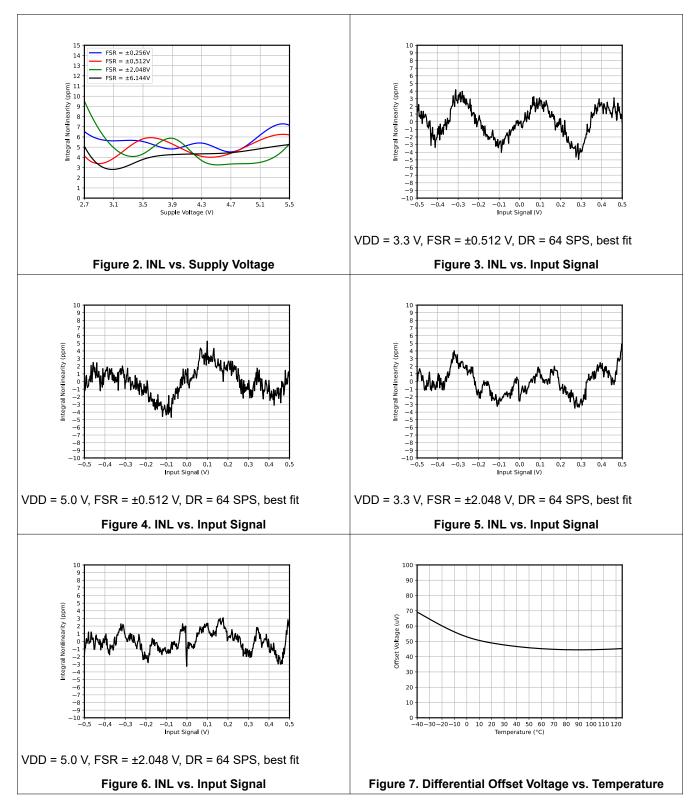

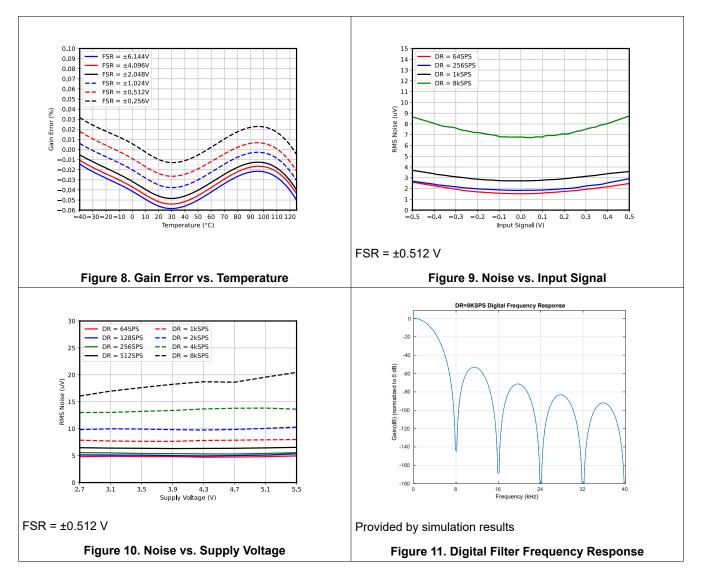

### **Typical Performance Characteristics**

All test conditions:  $T_A = 25^{\circ}C$ , VDD = 3.3 V, FSR =  $\pm 2.048$  V, DR = 64 SPS (unless otherwise noted).

(1)

(2)

# 16-Bit, 8 kSPS, 4-Channel Sigma-Delta ADC with Internal Reference and Temperature Sensor

### **Noise Performance**

The Sigma-Delta ( $\Sigma\Delta$ ) ADC architecture operates based on oversampling principles. In this approach, the input signal is sampled at a high frequency, known as the modulator frequency. The sampled signal is then processed through filtering and decimation in the digital domain, resulting in the final conversion output at a specified data rate. The oversampling ratio (OSR), which is the ratio between the modulator frequency and the output data rate, plays a crucial role. By increasing the OSR, and consequently lowering the output data rate, the ADC's noise performance can be optimized. This is achieved by averaging more samples of the internal modulator, thereby reducing input-referred noise. Additionally, increasing the gain proves beneficial for measuring low-level signals as it further contributes to the reduction of input-referred noise.

The following tables provide an overview of the device's noise performance, with data representative of typical noise characteristics at a temperature of 25°C and the inputs externally shorted together. Table 1 and table 2 display the input-referred noise in units of microvolts root mean square ( $\mu$ VRMS), with microvolts peak-to-peak ( $\mu$ VPP) values shown in parentheses. Table 4 and Table 5 present the corresponding data in terms of effective number of bits (ENOB), calculated from  $\mu$ VRMS values using Equation 1. The noise-free bits, determined from peak-to-peak noise values using Equation 2, are enclosed in parentheses.

ENOB = In(FSR/V<sub>RMS - Noise</sub>)/In(2) Noise - Free Bits = In(FSR/V<sub>PP - Noise</sub>)/In(2)

| Data Rate<br>(SPS) | FSR (V) |        |        |        |        |        |  |  |  |

|--------------------|---------|--------|--------|--------|--------|--------|--|--|--|

|                    | ±6.144  | ±4.096 | ±2.048 | ±1.024 | ±0.512 | ±0.256 |  |  |  |

| 64                 | 187.5   | 125    | 62.5   | 31.25  | 15.62  | 7.81   |  |  |  |

| 128                | 187.5   | 125    | 62.5   | 31.25  | 15.62  | 7.81   |  |  |  |

| 256                | 187.5   | 125    | 62.5   | 31.25  | 15.62  | 7.81   |  |  |  |

| 512                | 187.5   | 125    | 62.5   | 31.25  | 15.62  | 7.81   |  |  |  |

| 1024               | 187.5   | 125    | 62.5   | 31.25  | 15.62  | 7.81   |  |  |  |

| 2k                 | 187.5   | 125    | 62.5   | 31.25  | 15.62  | 7.81   |  |  |  |

| 4k                 | 187.5   | 125    | 62.5   | 31.25  | 15.62  | 7.81   |  |  |  |

| 8k                 | 187.5   | 125    | 62.5   | 31.25  | 15.62  | 7.81   |  |  |  |

#### Table 4. Noise in $\mu$ VRMS at VDD = 3.3 V

#### Table 5. Noise in $\mu$ VPP at VDD = 3.3 V

| Data Rate | e FSR (V) |        |        |        |        |        |  |  |

|-----------|-----------|--------|--------|--------|--------|--------|--|--|

| (SPS)     | ±6.144    | ±4.096 | ±2.048 | ±1.024 | ±0.512 | ±0.256 |  |  |

| 64        | 187.5     | 125    | 62.5   | 31.25  | 15.62  | 7.81   |  |  |

| 128       | 187.5     | 125    | 62.5   | 31.25  | 15.62  | 7.81   |  |  |

| 256       | 187.5     | 125    | 62.5   | 31.25  | 15.62  | 7.81   |  |  |

| 512       | 187.5     | 125    | 62.5   | 31.25  | 15.62  | 9.08   |  |  |

| 1024      | 187.5     | 125    | 62.5   | 31.25  | 15.62  | 11.52  |  |  |

| 2k        | 187.5     | 125    | 62.5   | 31.25  | 18.85  | 13.95  |  |  |

| 4k        | 226.19    | 146.29 | 75.74  | 40.42  | 24.64  | 18.98  |  |  |

| 8k        | 296.03    | 206.5  | 100.34 | 52.58  | 33.91  | 26.77  |  |  |

| Data Rate | FSR    |        |        |        |        |        |  |  |

|-----------|--------|--------|--------|--------|--------|--------|--|--|

| (SPS)     | ±6.144 | ±4.096 | ±2.048 | ±1.024 | ±0.512 | ±0.256 |  |  |

| 64        | 16     | 16     | 16     | 16     | 16     | 16     |  |  |

| 128       | 16     | 16     | 16     | 16     | 16     | 16     |  |  |

| 256       | 16     | 16     | 16     | 16     | 16     | 16     |  |  |

| 512       | 16     | 16     | 16     | 16     | 16     | 16     |  |  |

| 1024      | 16     | 16     | 16     | 16     | 16     | 16     |  |  |

| 2k        | 16     | 16     | 16     | 16     | 16     | 16     |  |  |

| 4k        | 16     | 16     | 16     | 16     | 16     | 16     |  |  |

| 8k        | 16     | 16     | 16     | 16     | 16     | 16     |  |  |

#### Table 6. ENOB from RMS Noise at VDD = 3.3 V

### Table 7. Noise-Free Bits from Peak-to-Peak Noise at VDD = 3.3 V

| Data Rate |        |        | F      | SR     |        |        |

|-----------|--------|--------|--------|--------|--------|--------|

| (SPS)     | ±6.144 | ±4.096 | ±2.048 | ±1.024 | ±0.512 | ±0.256 |

| 64        | 16     | 16     | 16     | 16     | 16     | 16     |

| 128       | 16     | 16     | 16     | 16     | 16     | 16     |

| 256       | 16     | 16     | 16     | 16     | 16     | 16     |

| 512       | 16     | 16     | 16     | 16     | 16     | 15.8   |

| 1024      | 16     | 16     | 16     | 16     | 16     | 15.4   |

| 2k        | 16     | 16     | 16     | 16     | 15.7   | 15.2   |

| 4k        | 15.7   | 15.8   | 15.7   | 15.6   | 15.3   | 14.7   |

| 8k        | 15.3   | 15.3   | 15.3   | 15.3   | 14.9   | 14.2   |

### **Detailed Description**

### Overview

The TPC6160S is a compact, low-power, 16-bit sigma-delta analog-to-digital converter (ADC) designed to minimize external circuitry and enhance performance. It incorporates a  $\Sigma\Delta$  ADC core with adjustable gain, an internal voltage reference, a clock oscillator, and an SPI interface. Additionally, it integrates a precise temperature sensor. The ADC core measures a differential signal, VIN, representing the difference between V(AINP) and V(AINN). The core features a differential, switched-capacitor  $\Sigma\Delta$  modulator followed by a digital filter, providing strong common-mode signal attenuation.

The device operates in single-shot or continuous-conversion modes, with single-shot mode saving power by performing one conversion upon request and entering a power-down state. In continuous-conversion mode, the ADC automatically initiates conversions, and data can be read at any time, reflecting the most recent completed conversion.

### Functional Block Diagram

(3)

# 16-Bit, 8 kSPS, 4-Channel Sigma-Delta ADC with Internal Reference and Temperature Sensor

### Feature Description

#### Multiplexer

The TPC6160S is integrated with an input multiplexer (mux). It allows the measurement of either four single-ended signals or two differential signals. Also, the AIN0, AIN1, and AIN2 inputs can be differentially measured against AIN3. The configuration of the multiplexer is controlled by the MUX[2:0] bits in the Config register. In cases where single-ended signals are being measured, the negative input of the ADC is internally connected to GND through a switch within the multiplexer.

When single-ended inputs are being measured, the TPC6160S does not produce negative codes. Negative codes are indicative of negative differential signals, where  $(V_{(AINP)} - V_{(AINN)}) < 0$ . Electrostatic discharge (ESD) diodes to VDD and GND serve to protect the ADC inputs. The TPC6160S is allowed to measure absolute negative input voltage down to -128 mV and still needs to prevent the ESD diodes from turning on, it is essential to maintain the absolute voltage on any input within the range specified in the following equation:

$GND - 0.3 V < V_{(AINx)} < VDD + 0.3 V$

If there is a possibility that the voltages on the input pins may violate these conditions, it is advisable to employ external Schottky diodes and series resistors. This helps to limit the input current to safe values. Additionally, overdriving one unused input on the TPC6160S may impact conversions occurring on other input pins at that time. In cases where overdriving unused inputs is a possibility, it is recommended to clamp the signal using external Schottky diodes.

#### Analog Inputs

The TPC6160S employs a switched-capacitor input stage, where capacitors undergo a continuous charging and discharging process to measure the voltage between  $AIN_P$  and  $AIN_N$ . The equivalent resistance is determined by the values of the capacitors and the frequency at which they are switched.

The common-mode input impedance is determined by applying a common-mode signal to the shorted  $AIN_P$  and  $AIN_N$  inputs and measuring the average current consumed by each pin. The common-mode input impedance may vary depending on the selected full-scale range. The common-mode input impedance is denoted as  $Z_{CM}$ .

The differential input impedance is measured by applying a differential signal to the AIN<sub>P</sub> and AIN<sub>N</sub> inputs. The average current flowing through the input pins represents the differential current and scales with the selected full-scale range. The symbol  $Z_{DIFF}$  represents the differential input impedance.

Note that this unbuffered input path provides a dynamic load to the driving source. Therefore, resistor/capacitor combinations on the input pins can cause DC gain errors, depending on the output impedance of the source that is driving the ADC input. The table below shows the allowable external resistance/capacitance values such that no gain error at the 16-bit level is introduced when the data rate is within 2 kSPS.

| R (Ω) | C (pF) |

|-------|--------|

| 20    | 1000   |

| 50    | 400    |

| 100   | 200    |

### Table 8. External R-C Combination for No 16-Bit Gain Error

#### Full-Scale Range (FSR) and LSB Size

The gain setting of PGA inside TPC6160S  $\Sigma\Delta$  ADC determines the input full-scale range (FSR). The full-scale range is configured by bits PGA[2:0] in the Config register, and can be set to ±6.144 V, ±4.096 V, ±2.048 V, ±1.024 V, ±0.512 V, or ±0.256 V.

The table below presents the Full-Scale Range (FSR) alongside the corresponding Least Significant Bit (LSB) size. The LSB size is calculated from the full-scale voltage using the formula in Equation 4. It is essential to ensure that the analog input voltage never exceeds the specified analog input voltage range limit provided in the Electrical Characteristics. If a VDD greater than 4 V is utilized, the  $\pm 6.144$ -V full-scale range allows input voltages to extend up to the supply voltage. It is important to note that in such cases or whenever the supply voltage is less than the full-scale range (e.g., VDD = 3.3 V and full-scale range =  $\pm 4.096$  V), a full-scale ADC output code cannot be achieved, resulting in a loss of dynamic range.

$$LSB = FSR/2^{16}$$

(4)

#### Table 9. Full-Scale Range and Corresponding LSB Size

| FSR                     | LSB Size  |  |  |

|-------------------------|-----------|--|--|

| ±6.144 V <sup>(1)</sup> | 187.5 μV  |  |  |

| ±4.096 V <sup>(1)</sup> | 125 µV    |  |  |

| ±2.048 V                | 62.5 μV   |  |  |

| ±1.024 V                | 31.25 μV  |  |  |

| ±0.512 V                | 15.625 μV |  |  |

| ±0.256 V                | 7.8125 μV |  |  |

(1) This parameter expresses the full-scale range of the ADC scaling. Do not apply more than VDD + 0.3 V to this device.

#### Voltage Reference

The TPC6160S integrates an internal voltage reference, and the use of an external reference is not supported with this device. Any errors associated with the initial voltage reference accuracy and its drift with temperature are accounted for in the gain error and gain drift specifications provided in the specifications.

### Oscillator

The TPC6160S features an integrated oscillator, eliminating the need for an external clock to drive the device. It's important to note that the internal oscillator may exhibit drift over temperature and time. Additionally, the output data rate scales proportionally with the oscillator frequency.

### Temperature Sensor

The TPC6160S includes a precision temperature sensor, activated by setting TS\_MODE = 1 in the Config Register, which outputs a 14-bit left-justified result within a 16-bit conversion, with each LSB representing  $0.03125^{\circ}$ C and negative values in twos complement format.

| Temperature (°C) | Digital Output (Binary) | HEX  |

|------------------|-------------------------|------|

| 128              | 01 0000 0000 0000       | 1000 |

| 127.96875        | 00 1111 1111 1111       | OFFF |

| 100              | 00 1100 1000 0000       | 0C80 |

| 75               | 00 1001 0110 0000       | 0960 |

| 50               | 00 0110 0100 0000       | 0640 |

| 25               | 00 0011 0010 0000       | 0320 |

| 0.25             | 00 0000 0000 1000       | 0008 |

| 0.03125          | 00 0000 0000 0001       | 0001 |

| 0                | 00 0000 0000 0000       | 0000 |

| Temperature (°C) | Digital Output (Binary) | HEX  |

|------------------|-------------------------|------|

| -0.25            | 11 1111 1111 1000       | 3FF8 |

| -25              | 11 1100 1110 0000       | 3CE0 |

| -40              | 11 1011 0000 0000       | 3B00 |

#### **Converting from Temperature to Digital Codes**

For positive temperatures:

For positive temperature values, twos complement is not applied; instead, the number is directly converted to a 14-bit binary format, left-justified within the 16-bit result, with the MSB set to 0 to indicate a positive sign.

For negative temperatures:

To generate the two's complement of a negative number, first take the binary representation of its absolute value, complement all bits, add 1 to the result, and set the MSB to 1 to indicate the negative sign.

For positive temperature values, twos complement is not applied; instead, the number is directly converted to a 14-bit binary format, left-justified within the 16-bit result, with the MSB set to 0 to indicate a positive sign.

#### **Converting from Digital Codes to Temperature**

For positive temperatures:

For positive temperature values, twos complement is not applied; instead, the number is directly converted to a 14-bit binary format, left-justified within the 16-bit result, with the MSB set to 0 to indicate a positive sign.

For negative temperatures:

To generate the two's complement of a negative number, first take the binary representation of its absolute value, complement all bits, add 1 to the result, and set the MSB to 1 to indicate the negative sign.

For positive temperature values, twos complement is not applied; instead, the number is directly converted to a 14-bit binary format, left-justified within the 16-bit result, with the MSB set to 0 to indicate a positive sign.

### **Digital Interface**

#### Device Functional Modes Reset and Power-Up

When the TPC6160S powers up, the device undergoes a reset procedure that results in the configuration register (Config register) having all its bits set to their default values. In its default state, the device enters a power-down mode upon startup. During this mode, the device's interface and digital blocks remain active, but no data conversions take place. This initial power-down state is designed to prevent systems with stringent power-supply requirements from experiencing a surge during the power-up phase.

#### **Operating Modes**

The TPC6160S operates in one of two modes: continuous-conversion or single-shot. The operating mode is determined by the state of the MODE bit in the Config register.

#### Single-Shot Mode and Power-Down

When the MODE bit in the Config register is set to 1, indicating single-shot mode, the TPC6160S enters a power-down state. This power-down state is the default state when power is first applied. While in this state, the device remains responsive to commands. The device will stay in the power-down state until a 1 is written to the single-shot (SS) bit in the Config register. When the SS bit is set, the device powers up, resets the SS bit to 0, and initiates a single conversion. Once the conversion is completed, and the conversion data is ready, the device returns to the power-down state. Attempting to write a 1 to the SS bit while a conversion is already in progress will have no effect. To switch to continuous-conversion mode, it is necessary to write a 0 to the MODE bit in the Config register.

#### **Continuous-Conversion Mode**

In continuous-conversion mode, where the MODE bit is set to 0, the TPC6160S consistently conducts conversions. Once a conversion is finished, the result is stored in the Conversion register, and the device promptly initiates another conversion. To transition to single-shot mode, one can write a 1 to the MODE bit in the Config register or perform a device reset.

### Duty Cycling for Low Power

The noise performance of a  $\Sigma\Delta$  ADC typically improves at lower output data rates, as more samples of the internal modulator are averaged to produce a single conversion result. In scenarios where power consumption is critical consideration and enhanced noise performance at low data rates is not essential, the TPC6160S provides support for duty cycling. This feature enables significant power savings by periodically requesting high data-rate readings at an effectively lower data rate.

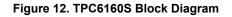

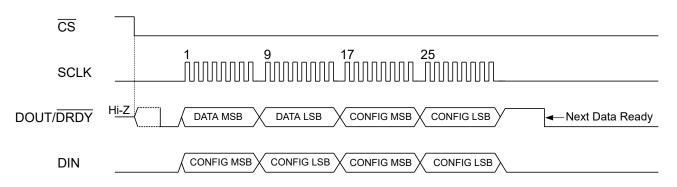

#### Programming Serial Interface

The SPI-compatible serial interface of the TPC6160S includes either four signals ( $\overline{CS}$ , SCLK, DIN, and DOUT/ $\overline{DRDY}$ ) or three signals (SCLK, DIN, and DOUT/ $\overline{DRDY}$  with  $\overline{CS}$  tied low). This interface facilitates tasks such as reading conversion data, accessing registers for reading and writing, and controlling the operation of the device.

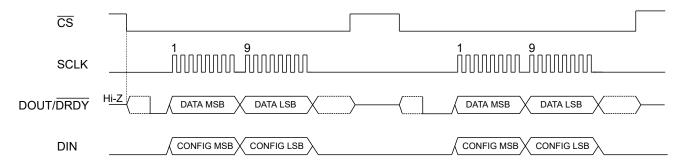

#### **Chip Select**

The chip select pin  $(\overline{CS})$  is utilized to select the TPC6160S for SPI communication, particularly beneficial in scenarios where multiple devices share the same serial bus. It is essential to keep  $\overline{CS}$  low throughout the serial communication process. When  $\overline{CS}$  is raised to a high state, the serial interface undergoes a reset, SCLK signals are disregarded, and DOUT/DRDY enters a high-impedance state, rendering it unable to provide data-ready indication. For situations involving multiple devices where DOUT/DRDY monitoring is necessary, periodically lowering  $\overline{CS}$  enables either an immediate high signal, indicating no new data, or an immediate low signal, indicating the availability of new data in the Conversion register. Data transfer can occur at any time without risking data corruption, as the current result is locked into the output shift register during transmission and remains unchanged until the communication concludes.

#### Serial Clock

The serial clock pin (SCLK) incorporates a Schmitt-triggered input and serves the purpose of clocking data into and out of the TPC6160S through the DIN and DOUT/DRDY pins. It is important to maintain a clean SCLK signal, despite the hysteresis present, to prevent glitches that can inadvertently shift the data. To initiate a reset of the serial interface, SCLK should be held low for 30.8 ms, and the subsequent SCLK pulse will commence a new communication cycle. This time-out feature can be utilized to recover communication in cases where a serial interface transmission is interrupted. During idle periods of the serial interface, SCLK should be held low.

#### Data Input

The data input pin (DIN) collaborates with SCLK to transmit data to the TPC6160S. Data is latched on the DIN pin at the falling edge of the SCLK signal. It's important to note that the device does not actively drive the DIN pin.

### Data Output and Data Ready

The data output and data ready pin (DOUT/DRDY) is employed, along with SCLK, for reading conversion and register data from the TPC6160S. Data present on DOUT/DRDY are shifted out on the rising edge of the SCLK signal. Additionally, DOUT/DRDY serves as an indicator of the completion of a conversion, signaling that new data is ready for retrieval. The pin transitions low when new data is available. DOUT/DRDY can also be utilized to trigger a microcontroller to initiate the reading of data from the TPC6160S. In continuous-conversion mode, DOUT/DRDY returns high again 8 µs before the subsequent data ready signal (DOUT/DRDY low) if no data is retrieved from the device. It is essential to complete the data transfer before DOUT/DRDY returns high.

In single-shot mode, once the  $\overline{\text{DRDY}}$  is low for signaling data ready, the new SPI command should be sent 8 µs after the  $\overline{\text{DRDY}}$  low.

(1)  $\overline{\text{CS}}$  can be held low if the TPC6160S does not share the serial bus with another device. If  $\overline{\text{CS}}$  is low, DOUT/ $\overline{\text{DRDY}}$  asserts low indicating new data is available.

#### Figure 13. DOUT/DRDY Behavior Without Data Retrieval in Continuous-Conversion Mode

When the chip select ( $\overline{CS}$ ) pin is in a high state, the data output and data ready pin (DOUT/ $\overline{DRDY}$ ) is automatically configured with a weak internal pullup resistor as a default setting. This configuration minimizes the chance of DOUT/ $\overline{DRDY}$  floating near the mid-supply voltage and causing leakage current in the master device. To deactivate this pullup resistor and place the device into a high-impedance state, set the PULL\_UP\_EN bit to 0 in the Config register.

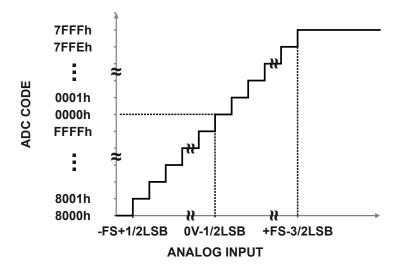

#### Data Format

The TPC6160S outputs data in a 16-bit binary two's complement format. For a positive full-scale (+FS) input, the output code is 7FFFFh, while a negative full-scale (-FS) input results in an output code of 800000h. The output codes clip at these values for signals that exceed the full-scale range. The table below provides a summary of the ideal output codes corresponding to different input signals.

| Input Signal, VIN (AIN <sub>P</sub> – AIN <sub>N</sub> ) | Ideal Output Code <sup>(1)</sup> |

|----------------------------------------------------------|----------------------------------|

| ≥ FS (2 <sup>15</sup> – 1) / 2 <sup>15</sup>             | 7FFFh                            |

| FS / 2 <sup>15</sup>                                     | 0001h                            |

| 0                                                        | 0000h                            |

| -FS / 2 <sup>15</sup>                                    | FFFFh                            |

| ≤ -FS                                                    | 8000h                            |

(1) Excludes the effects of noise, INL, offset, and gain errors.

Figure 14. Code Transition Diagram

#### Data Retrieval

Data is written to and read from the TPC6160S in the same manner for both single-shot and continuous conversion modes, without the need to issue specific commands. The operating mode for the device is determined by the MODE bit in the Config register.

To set the device in continuous-conversion mode, set the MODE bit to 0. In this mode, the device consistently initiates new conversions, even when the  $\overline{CS}$  is high.

To activate single-shot mode, set the MODE bit to 1. In this mode, a new conversion begins only when the SS bit is written with a value of 1.

The conversion data is continuously buffered and remains unchanged until new conversion data replaces it. Reading the data can be done at any time without the risk of corruption. When DOUT/DRDY goes low, indicating the availability of new conversion data, the data can be read by shifting it out on DOUT/DRDY. The most significant bit (MSB), bit 23, is clocked out on the first rising edge of SCLK. Simultaneously, new data for the Config register is latched on DIN during the falling edge of SCLK.

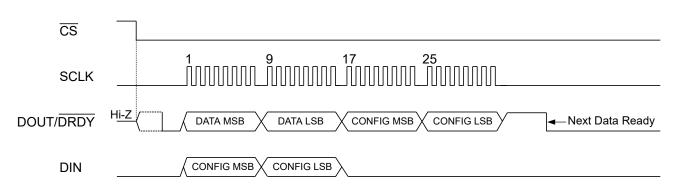

The TPC6160S provides an option for direct readback of the Config register settings within the same data transmission cycle. A complete data transmission cycle is either 48 bits (when Config register readback is employed) or 16 bits (used only when the  $\overline{CS}$  line is controllable and not permanently tied low).

#### 32-Bit Data Transmission Cycle

The data in a 32-bit data transmission cycle consists of six bytes: three bytes for the conversion result, and an additional three bytes for the Config register readback. The device always reads the MSB first.

During a single transmission cycle, write the same Config register setting twice, as illustrated in the figure below. For convenience, user can write the Config register setting once during the first half of the transmission cycle. Subsequently, maintain the DIN pin either low or high during the second half of the cycle. If there is no need to update the Config register, keep the DIN pin either low or high throughout the entire transmission cycle, while keeping the DIN pin high only in single-shot mode. The Config register setting written in the first three bytes of a 32-bit transmission cycle is read back in the last three bytes of the same cycle.

When utilizing a continuous SCLK for the entire 32-bit data transfer, ensure that the SCLK frequency remains below 1 MHz. In case an SCLK frequency exceeding 1 MHz is employed, introduce a delay between the transmission of the first 16 bits and the second 16 bits. This delay is necessary to allow for the complete decoding of the Config register write before initiating the readback of the Config register. Select a delay that ensures the time between the SCLK rising edge of the first bit and the SCLK rising edge of the 17th bit exceeds 16 µs.

(1)  $\overline{\text{CS}}$  can be held low if the TPC6160S does not share the serial bus with another device. If  $\overline{\text{CS}}$  is low, DOUT/ $\overline{\text{DRDY}}$  asserts low indicating new data is available.

#### Figure 15. 32-Bit Data Transmission Cycle with Config Register Readback

(1)  $\overline{\text{CS}}$  can be held low if the TPC6160S does not share the serial bus with another device. If  $\overline{\text{CS}}$  is low, DOUT/ $\overline{\text{DRDY}}$  asserts low indicating new data is available.

#### Figure 16. 32-Bit Data Transmission Cycle: DIN Held Low

#### 16-Bit Data Transmission Cycle

If there is no need to read back Config register data, the conversion data from the TPC6160S can be clocked out in a concise 16-bit data transmission cycle, as depicted in the figure below. After the 16th SCLK cycle, set  $\overline{CS}$  high to reset the SPI interface. Upon the subsequent lowering of  $\overline{CS}$ , data transmission initiates, starting with the currently buffered conversion result on the first SCLK rising edge. If DOUT/ $\overline{DRDY}$  is low at the beginning of data retrieval, the conversion buffer is already updated with a new result. Conversely, if DOUT/ $\overline{DRDY}$  is high, the same result from the preceding data transmission cycle is read.

If there is no need to update the Config register, keep the DIN pin either low or high throughout the entire transmission cycle in continuous-conversion mode, while keeping the DIN pin high only in single-shot mode.

(1)  $\overline{\text{CS}}$  can be held low if the TPC6160S does not share the serial bus with another device. If  $\overline{\text{CS}}$  is low, DOUT/ $\overline{\text{DRDY}}$  asserts low indicating new data is available.

#### Figure 17. 16-Bit Data Transmission Cycle

### **Register Summary**

The TPC6160S features two accessible registers via SPI. The Conversion register is the result of the most recent conversion, while the Config register sets operating modes and inquiries about the device's status.

#### Conversion Register [reset = 0000h]

The 16-bit Conversion register stores the results of the latest conversion in binary twos complement format. After power-up, the register is reset to 0 and retains this value until the initial conversion is finished. Refer to the table below for the register format.

#### Table 11. Conversion Register

| 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    |

|------|------|------|------|------|------|------|------|

| D15  | D14  | D13  | D12  | D11  | D10  | D9   | D8   |

| R-0h |

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

| R-0h |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 12. Conversion Register Field Descriptions

| Bit  | Field   | Туре | Reset | Description              |

|------|---------|------|-------|--------------------------|

| 15:0 | D[15:0] | R    | 0000h | 16-bit conversion result |

#### Config Register [reset = 058Bh]

The 24-bit Config register can be configured to set the TPC6160S operating mode, input selection, data rate, full-scale range, temperature sensor mode, and global chop mode. The register format is shown in the table below.

#### Table 13. Config Register

| 15      | 14 | 13       | 12      | 11         | 10       | 9    | 8        |

|---------|----|----------|---------|------------|----------|------|----------|

| SS      |    | MUX[2:0] |         |            | MODE     |      |          |

| R/W-0h  |    | R/W-0h   |         |            | R/W-1h   |      |          |

| 7       | 6  | 5        | 4       | 3          | 2 1      |      | 0        |

| DR[2:0] |    |          | TS_MODE | PULL_UP_EN | NOP[1:0] |      | Reserved |

| R/W-4h  |    |          | R/W-0h  | R/W-1h     | R/W      | R-1h |          |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

| Bit   | Field    | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|----------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15    | SS       | R/W  | Oh    | Single-shot conversion start<br>This bit is used to start a single conversion. SS can only be written<br>when in power-down state and has no effect when a conversion is<br>ongoing.<br>When writing:<br>0 = No effect<br>1 = Start a single conversion (when in power-down state)<br>Always read back as 0 (default).                                                                                                                                                                                                                                     |

| 14:12 | MUX[2:0] | R/W  | Oh    | Input multiplexer configurationThese bits configure the input multiplexer. $000 = AIN_P$ is AIN0 and AIN <sub>N</sub> is AIN1 (default) $001 = AIN_P$ is AIN0 and AIN <sub>N</sub> is AIN3 $010 = AIN_P$ is AIN1 and AIN <sub>N</sub> is AIN3 $011 = AIN_P$ is AIN2 and AIN <sub>N</sub> is AIN3 $011 = AIN_P$ is AIN2 and AIN <sub>N</sub> is GND $101 = AIN_P$ is AIN1 and AIN <sub>N</sub> is GND $101 = AIN_P$ is AIN2 and AIN <sub>N</sub> is GND $110 = AIN_P$ is AIN2 and AIN <sub>N</sub> is GND $111 = AIN_P$ is AIN3 and AIN <sub>N</sub> is GND |

| 11:9  | PGA[2:0] | R/W  | 2h    | Programmable gain amplifier configuration<br>These bits configure the programmable gain amplifier.<br>$000 = FSR \text{ is } \pm 6.144 \text{ V}^{(1)}$<br>$001 = FSR \text{ is } \pm 4.096 \text{ V}^{(1)}$<br>$010 = FSR \text{ is } \pm 2.048 \text{ V} (default)$<br>$011 = FSR \text{ is } \pm 1.024 \text{ V}$<br>$100 = FSR \text{ is } \pm 0.512 \text{ V}$<br>$101 = FSR \text{ is } \pm 0.256 \text{ V}$<br>$110 = FSR \text{ is } \pm 0.256 \text{ V}$<br>$111 = FSR \text{ is } \pm 0.256 \text{ V}$                                           |

| 8     | MODE     | R/W  | 1h    | <ul> <li>Device operating mode</li> <li>This bit controls the TPC6160S operating mode.</li> <li>0 = Continuous-conversion mode</li> <li>1 = Power-down and single-shot mode (default)</li> </ul>                                                                                                                                                                                                                                                                                                                                                           |

| 7:5   | DR[2:0]  | R/W  | 4h    | Data rate<br>These bits control the data-rate setting.<br>000 = 64 SPS<br>001 = 128 SPS<br>010 = 256 SPS<br>011 = 512 SPS<br>100 = 1024 SPS (default)<br>101 = 2 kSPS<br>110 = 4 kSPS<br>111 = 8 kSPS                                                                                                                                                                                                                                                                                                                                                      |

| 4     | TS_MODE  | R/W  | 0h    | Temperature sensor mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Bit | Field      | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |            |      |       | This bit configures the ADC to convert temperature or input signals.<br>0 = ADC mode (default<br>1 = Temperature sensor mod                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3   | PULL_UP_EN | R/W  | 1h    | Pullup enable         This bit enables a weak internal pullup resistor on the DOUT/DRDY         pin only when CS is high. When enabled, an internal resistor         connects the bus line to supply. When disabled, the DOUT/DRDY         pin floats.         0 = Pullup resistor disabled on DOUT/DRDY         1 = Pullup resistor enabled on DOUT/DRDY pin                                                                                                                                                                                                                                                           |

| 2:1 | NOP[1:0]   | R/W  | 1h    | No operation<br>The NOP[1:0] bits control whether data are written to the Config<br>register or not. For data to be written to the Config register, the<br>NOP[1:0] bits must be 01. Any other value results in a NOP<br>command. DIN can be held high or low during SCLK pulses without<br>data being written to the Config register.<br>00 = Invalid data; do not update the contents of the Config register<br>01 = Valid data; update the Config register (default)<br>10 = Invalid data; do not update the contents of the Config register<br>11 = Invalid data; do not update the contents of the Config register |

| 0   | Reserved   | R    | 1h    | <b>Reserved</b><br>Writing either 0 or 1 to this bit has no effect.<br>Always read back 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

(1) This parameter expresses the full-scale range of the ADC scaling. Do not apply more than VDD + 0.3 V to this device.

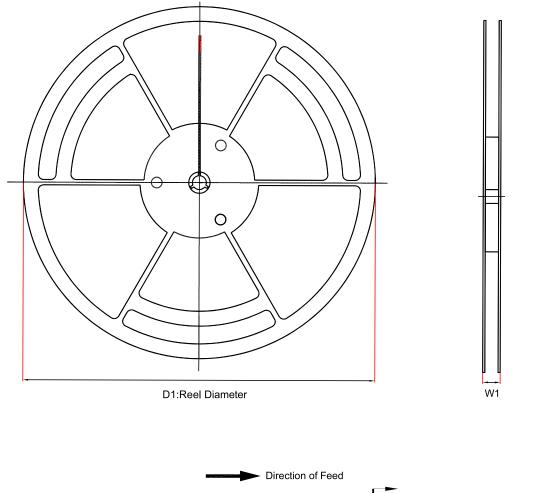

### **Tape and Reel Information**

| Order Number  | Package | D1 (mm) | W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P0 (mm) | W0 (mm) | Pin1<br>Quadrant |

|---------------|---------|---------|---------|---------|---------|---------|---------|---------|------------------|

| TPC6160S-VS2R | MSOP10  | 330     | 17.6    | 5.3     | 3.4     | 1.4     | 8       | 12      | Q1               |

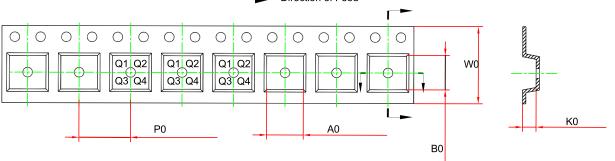

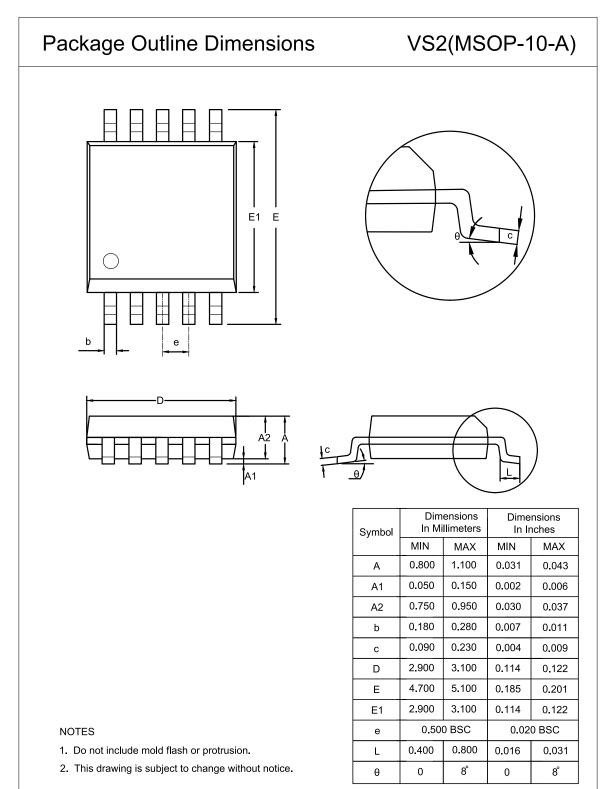

### **Package Outline Dimensions**

### MSOP10

### **Order Information**

| Order Number  | Operating Temperature<br>Range | Package | Marking Information | MSL | Transport Media, Quantity | Eco Plan |

|---------------|--------------------------------|---------|---------------------|-----|---------------------------|----------|

| TPC6160S-VS2R | −40 to 125°C                   | MSOP10  | 6160S               | 2   | T&R, 3000                 | Green    |

**Green**: 3PEAK defines "Green" to mean RoHS compatible and free of halogen substances.

**TPC6160S**

### 16-Bit, 8 kSPS, 4-Channel Sigma-Delta ADC with Internal Reference and Temperature Sensor

### IMPORTANT NOTICE AND DISCLAIMER

Copyright<sup>©</sup> 3PEAK 2012-2025. All rights reserved.

**Trademarks.** Any of the 思瑞浦 or 3PEAK trade names, trademarks, graphic marks, and domain names contained in this document /material are the property of 3PEAK. You may NOT reproduce, modify, publish, transmit or distribute any Trademark without the prior written consent of 3PEAK.

**Performance Information.** Performance tests or performance range contained in this document/material are either results of design simulation or actual tests conducted under designated testing environment. Any variation in testing environment or simulation environment, including but not limited to testing method, testing process or testing temperature, may affect actual performance of the product.

**Disclaimer.** 3PEAK provides technical and reliability data (including data sheets), design resources (including reference designs), application or other design recommendations, networking tools, security information and other resources "As Is". 3PEAK makes no warranty as to the absence of defects, and makes no warranties of any kind, express or implied, including without limitation, implied warranties as to merchantability, fitness for a particular purpose or non-infringement of any third-party's intellectual property rights. Unless otherwise specified in writing, products supplied by 3PEAK are not designed to be used in any life-threatening scenarios, including critical medical applications, automotive safety-critical systems, aviation, aerospace, or any situations where failure could result in bodily harm, loss of life, or significant property damage. 3PEAK disclaims all liability for any such unauthorized use.