## Features

- Multi-channel SAR ADC Product Family

- 16-bit Resolution with No Missing Code

- 8-channel Multiplexed Inputs

- Flexible Input Types

- Unipolar Single-ended

- Unipolar Differential Pairs

- Unipolar Differential (GND sense)

- Bipolar Differential Pairs

- Bipolar Differential (COM = V<sub>REF</sub>/2)

- Throuput: 1 MSPS

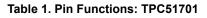

- High Linearity

- DNL: ±0.55 LSB typical

- INL: ±1.5 LSB typical

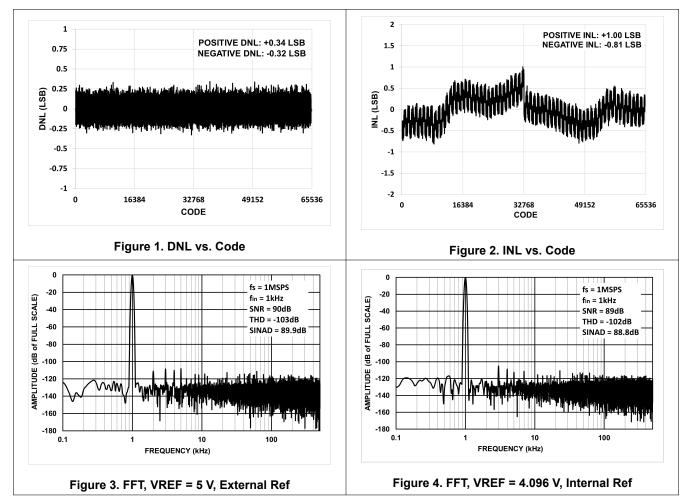

- High Dynamic Performance

- SNR: 89.4 dB typical

- SINAD: 89.2 dB typical

- THD: −103 dB typical

- Analog Input Range: 0 V to  $V_{REF}$  with  $V_{REF}$  up to VDD

- Multiple Reference Types

- Internal 4.096 V

- External Buffered (up to 4.096 V)

- External (up to VDD)

- Integrated Function

- Internal Temperature Sensor

- Channel Senquencer

- Configurable One-pole Filter

- Busy Indicator

- Single 5 V Supply Operation

- 1.8-V to 5-V Logic Interface

- Serial Interface Compatible with SPI

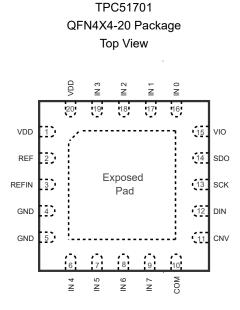

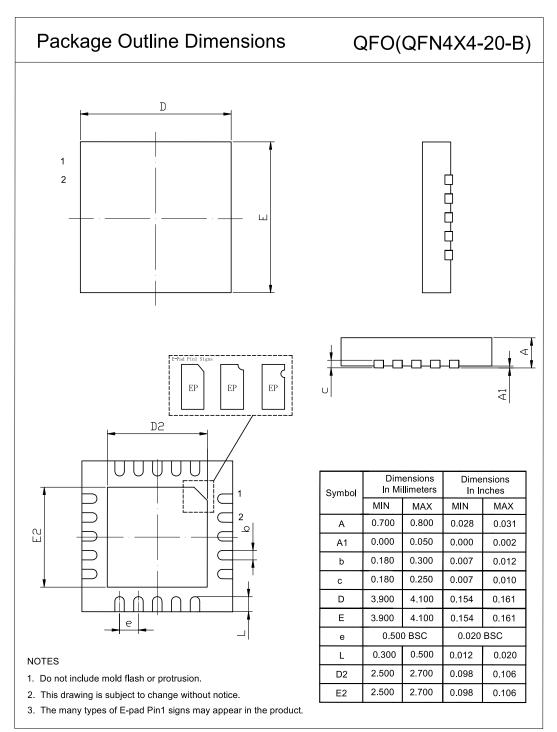

- Package: QFN 20-pin 4 mm x 4 mm

- Wide Operating Temperature Range

- −40°C to +125°C

### Applications

- Data Acquisitions

- Industry Automation

- Instrumentation

- Medical Equipment

- Power Line Monitoring

## Description

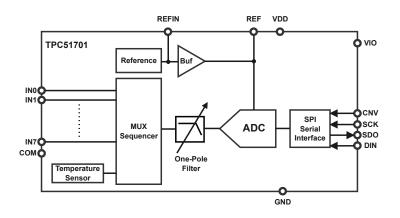

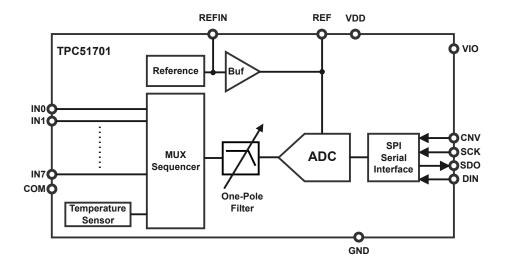

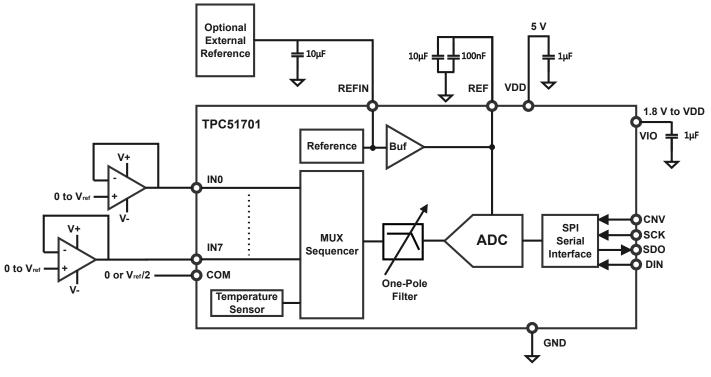

The TPC51701 is a 8-channel, 16-bit analog-to-digital converter (ADC) operating with a single power supply VDD.

The TPC51701 is high intergrated with 16-bit SAR ADC, 8channel multiplexer with a flexible sequencer, configurable one-pole filter, low drift internal buffered reference and a temperature sensor. Multiple input types is supported including unipolar and bipolar single-ended or differential.

The TPC51701 offers a serial port interface (SPI) for resigter and conversion results writing or reading. The interface is supplied with VIO that ranged from 1.8 V to 5 V.

The TPC51701 is available in compact 20-lead QFN 4 mm x 4 mm pacakge and operating from  $-40^{\circ}$ C to  $+125^{\circ}$ C.

TPC517xx is a product family covering different resultion, throughput and number of channels.

## **Block Diagram**

## **Table of Contents**

| Applications   1     Description   1     Block Diagram   1     Product Family Table   3     Revision History   3     Pin Configuration and Functions   4     Specifications   4     Specifications   6     Absolute Maximum Ratings (1)   6     ESD, Electrostatic Discharge Protection   6     Recommended Operating Conditions   6     Thermal Information   6     Electrical Characteristics   7     Timing Requirements (1)   9     Typical Performance Characteristics   10     Detailed Description   11     Overview   11     Functional Block Diagram   11     Feature Description   20     Typical Application   20     Typical Application   22     Package Outline Dimensions   23     QFN4X4-20   23     Order Information   24                                                                                         | Features                                | 1  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----|

| Block Diagram   1     Product Family Table   3     Revision History   3     Pin Configuration and Functions   4     Specifications   4     Absolute Maximum Ratings (1)   6     ESD, Electrostatic Discharge Protection   6     Recommended Operating Conditions   6     Thermal Information   6     Electrical Characteristics   7     Timing Requirements (1)   9     Typical Performance Characteristics   10     Detailed Description   11     Overview   11     Functional Block Diagram   12     Application and Implementation   20     Typical Application   20     Typical Application   21     Application and Implementation   22     Package Outline Dimensions   23     QFN4X4-20   23                                                                                                                                 | Applications                            | 1  |

| Product Family Table.   3     Revision History.   3     Pin Configuration and Functions.   4     Specifications.   4     Absolute Maximum Ratings <sup>(1)</sup> 6     ESD, Electrostatic Discharge Protection   6     Recommended Operating Conditions.   6     Thermal Information.   6     Electrical Characteristics.   7     Timing Requirements <sup>(1)</sup> 9     Typical Performance Characteristics.   10     Detailed Description.   11     Overview.   11     Functional Block Diagram.   11     Feature Description.   20     Typical Application   20     Typical Application.   20     Typical Application.   20     Typical Application.   21     Apple and Reel Information.   22     Package Outline Dimensions.   23     QFN4X4-20.   23                                                                        | Description                             | 1  |

| Revision History.   3     Pin Configuration and Functions.   4     Specifications.   6     Absolute Maximum Ratings <sup>(1)</sup> 6     ESD, Electrostatic Discharge Protection.   6     Recommended Operating Conditions.   6     Thermal Information.   6     Electrical Characteristics.   7     Timing Requirements <sup>(1)</sup> .   9     Typical Performance Characteristics.   10     Detailed Description.   11     Overview.   11     Functional Block Diagram.   11     Feature Description.   12     Application and Implementation.   20     Typical Application.   20     Typical Application.   21     Application and Implementation.   22     Package Outline Dimensions.   23     QFN4X4-20.   23                                                                                                               | Block Diagram                           | 1  |

| Pin Configuration and Functions.   4     Specifications.   6     Absolute Maximum Ratings <sup>(1)</sup> 6     ESD, Electrostatic Discharge Protection.   6     Recommended Operating Conditions.   6     Thermal Information.   6     Electrical Characteristics.   7     Timing Requirements <sup>(1)</sup> .   9     Typical Performance Characteristics.   10     Detailed Description.   11     Overview.   11     Functional Block Diagram.   11     Feature Description.   12     Application and Implementation.   20     Typical Application.   20     Tape and Reel Information.   20     Tape and Reel Information.   23     QFN4X4-20.   23                       | Product Family Table                    | 3  |

| Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Revision History                        | 3  |

| Absolute Maximum Ratings <sup>(1)</sup> 6     ESD, Electrostatic Discharge Protection   6     Recommended Operating Conditions   6     Thermal Information   6     Electrical Characteristics   7     Timing Requirements <sup>(1)</sup> 9     Typical Performance Characteristics   10     Detailed Description   11     Overview   11     Functional Block Diagram   11     Feature Description   12     Application and Implementation   20     Typical Application   20     Tape and Reel Information   23     QFN4X4-20   23 | Pin Configuration and Functions         | 4  |

| ESD, Electrostatic Discharge Protection   6     Recommended Operating Conditions   6     Thermal Information   6     Electrical Characteristics   7     Timing Requirements <sup>(1)</sup> 9     Typical Performance Characteristics   10     Detailed Description   11     Overview   11     Functional Block Diagram   11     Feature Description   12     Application and Implementation   20     Typical Application   20     Tape and Reel Information   20     Package Outline Dimensions   23     QFN4X4-20   23           | Specifications                          | 6  |

| Recommended Operating Conditions   6     Thermal Information   6     Electrical Characteristics   7     Timing Requirements <sup>(1)</sup> 9     Typical Performance Characteristics   10     Detailed Description   11     Overview   11     Functional Block Diagram   11     Feature Description   12     Application and Implementation   20     Typical Application   20     Tape and Reel Information   22     Package Outline Dimensions   23     QFN4X4-20   23                                                                                                                                                                                                                                                                                                                                                             | Absolute Maximum Ratings <sup>(1)</sup> | 6  |

| Thermal Information   66     Electrical Characteristics   7     Timing Requirements <sup>(1)</sup> 9     Typical Performance Characteristics   10     Detailed Description   11     Overview   11     Functional Block Diagram   11     Feature Description   12     Application and Implementation   20     Typical Application   20     Tape and Reel Information   22     Package Outline Dimensions   23     QFN4X4-20   23                                                                                                                                                                                                                                                                                                                                                                                                     | ESD, Electrostatic Discharge Protection | 6  |

| Electrical Characteristics.   7     Timing Requirements <sup>(1)</sup> 9     Typical Performance Characteristics.   10     Detailed Description.   11     Overview.   11     Functional Block Diagram.   11     Feature Description.   12     Application and Implementation.   20     Typical Application.   20     Tape and Reel Information.   22     Package Outline Dimensions.   23     QFN4X4-20.   23                                                                                                                                                                                                                                                                                                                                                                                                                       | Recommended Operating Conditions        | 6  |

| Timing Requirements <sup>(1)</sup> 9     Typical Performance Characteristics   10     Detailed Description   11     Overview   11     Functional Block Diagram   11     Feature Description   12     Application and Implementation   20     Typical Application   20     Tape and Reel Information   20     QFN4X4-20   23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Thermal Information                     | 6  |

| Typical Performance Characteristics.   10     Detailed Description.   11     Overview.   11     Functional Block Diagram.   11     Feature Description.   12     Application and Implementation.   20     Typical Application.   20     Tape and Reel Information.   20     Package Outline Dimensions.   23     QFN4X4-20.   23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Electrical Characteristics              | 7  |

| Detailed Description.   11     Overview.   11     Functional Block Diagram.   11     Feature Description.   12     Application and Implementation.   20     Typical Application.   20     Tape and Reel Information.   22     Package Outline Dimensions.   23     QFN4X4-20.   23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Timing Requirements <sup>(1)</sup>      | 9  |

| Overview.   11     Functional Block Diagram.   11     Feature Description.   12     Application and Implementation.   20     Typical Application.   20     Tape and Reel Information.   20     Package Outline Dimensions.   23     QFN4X4-20.   23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Typical Performance Characteristics     | 10 |

| Functional Block Diagram.   11     Feature Description.   12     Application and Implementation.   20     Typical Application.   20     Tape and Reel Information.   20     Package Outline Dimensions.   23     QFN4X4-20.   23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Detailed Description                    | 11 |

| Feature Description.   12     Application and Implementation.   20     Typical Application.   20     Tape and Reel Information.   20     Package Outline Dimensions.   23     QFN4X4-20.   23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Overview                                | 11 |

| Application and Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Functional Block Diagram                | 11 |

| Typical Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Feature Description                     | 12 |

| Tape and Reel Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Application and Implementation          | 20 |

| Package Outline Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Typical Application                     | 20 |

| QFN4X4-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Tape and Reel Information               | 22 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Package Outline Dimensions              | 23 |

| Order Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | QFN4X4-20                               | 23 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Order Information                       | 24 |

| IMPORTANT NOTICE AND DISCLAIMER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IMPORTANT NOTICE AND DISCLAIMER         | 25 |

# Product Family Table

| Order Number  | Order Number Channels |        | Channels Resolution Throughput |           | Package |

|---------------|-----------------------|--------|--------------------------------|-----------|---------|

| TPC51701-QFOR | 8                     | 16 bit | 1MSPS                          | QFN4X4-20 |         |

| TPC51707-QFOR | 8                     | 18 bit | 800kSPS                        | QFN4X4-20 |         |

# **Revision History**

| Date       | Revision | Notes            |

|------------|----------|------------------|

| 2023-12-01 | Rev.A.0  | Initial release. |

# Pin Configuration and Functions

| Pin              |                      | Turne | Description                                                                                                                                                                                                   |

|------------------|----------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.              | No. Name Type        |       | Description                                                                                                                                                                                                   |

| 1, 20            | VDD                  | Ρ     | Power supply. Typically 4.5 V to 5.5 V and decoupled with 10 $\mu F$ and 100 nF capacitors.                                                                                                                   |

| 2                | REF                  | AI/O  | Reference Input/Output.                                                                                                                                                                                       |

| 3                | REFIN                | AI/O  | Internal Reference Output/Reference Buffer Input.                                                                                                                                                             |

| 4, 5             | GND                  | Р     | Power Supply Ground.                                                                                                                                                                                          |

| 6, 7<br>8, 9     | IN4, IN5<br>IN6, IN7 | AI    | Analog Input Channel 4, Analog Input Channel 5, Analog Input Channel 6, and Analog Input Channel 7.                                                                                                           |

| 10               | СОМ                  | AI    | Common Channel Input. All input channels, IN[7:0], can be referenced to a common-mode point of 0 V or $V_{\text{REF}}/2$ V.                                                                                   |

| 11               | CNV                  | DI    | Conversion Input. On the rising edge, CNV initiates the conversion. During conversion, if CNV is held high, the busy indictor is enabled.                                                                     |

| 12               | DIN                  | DI    | Data input for writing the 14-bit configuration register. The configuration register can be written to during and after conversion.                                                                           |

| 13               | SCK                  | DI    | Serial Data Clock Input. This input clocks out the data on SDO and clock in data on DIN with MSB first.                                                                                                       |

| 14               | SDO                  | DO    | Serial Data Output. The conversion result is output on this pin and synchronized to SCK. In unipolar modes, conversion results are straight binary; in bipolar modes, conversion results are twos complement. |

| 15               | VIO                  | Р     | Input/Output Interface Digital Power.                                                                                                                                                                         |

| 16, 17<br>18, 19 | IN0, IN1<br>IN2, IN3 | AI    | Analog Input Channel 0, Analog Input Channel 1, Analog Input Channel 2, and Analog Input Channel 3.                                                                                                           |

| Pin Type   No. Name   21 (EPAD) Exposed | Turne          | Description |                                                                                                   |  |

|-----------------------------------------|----------------|-------------|---------------------------------------------------------------------------------------------------|--|

| No.                                     | Name           | туре        | Description                                                                                       |  |

| 21 (EPAD)                               | Exposed<br>Pad | Р           | The exposed paddle is not connected internally. Recommended that the pad be connected to the GND. |  |

# **Specifications**

### Absolute Maximum Ratings (1)

|                      | Parameter                    | Min       | Max       | Unit |

|----------------------|------------------------------|-----------|-----------|------|

| Analog Voltage       | INx, COM                     | GND - 0.3 | VDD + 0.3 | V    |

| Analog Voltage       | REF, REFIN                   | GND - 0.3 | VDD + 0.3 | V    |

|                      | DIN, CNV, SCK to GND         | GND - 0.3 | VIO + 0.3 | V    |

| Digital Voltage      | SDO to GND                   | GND - 0.3 | VIO + 0.3 | V    |

| Our makes V (alta ma | VDD, VIO to GND              | - 0.3     | 7         | V    |

| Supply Voltage       | VDD to VIO                   | - 7       | 7         | V    |

| TJ                   | Maximum Junction Temperature |           | 150       | °C   |

| T <sub>A</sub>       | Operating Temperature Range  | -40       | 125       | °C   |

| T <sub>STG</sub>     | Storage Temperature Range    | -65       | 150       | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

### ESD, Electrostatic Discharge Protection

| Symbol | Parameter                | Condition                             | Minimum Level | Unit |

|--------|--------------------------|---------------------------------------|---------------|------|

| HBM    | Human Body Model ESD     | ANSI/ESDA/JEDEC JS-001 (1)            | ±4            | kV   |

| CDM    | Charged Device Model ESD | ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ±1.5          | kV   |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **Recommended Operating Conditions**

| Parameter        | Min | Тур | Мах | Unit |

|------------------|-----|-----|-----|------|

| VDD              | 4.5 | 5   | 5.5 | V    |

| V <sub>REF</sub> | 2   | 5   | VDD | V    |

| VIO              | 1.8 |     | VDD | V    |

### **Thermal Information**

| Package Type | θ <sub>JA</sub> | θ」c θ」B |      | Unit |  |

|--------------|-----------------|---------|------|------|--|

| QFN4X4-20    | 51.0            | 25.1    | 21.6 | °C/W |  |

### **Electrical Characteristics**

All test conditions is at VDD = 5 V,  $V_{REF}$  = 5 V, VIO = 5 V,  $T_A$  = -40 °C to +125 °C, unless otherwise noted.

| Parameter                                  | Test Conditions                                                  | Min                       | Тур                 | Max                       | Unit   |

|--------------------------------------------|------------------------------------------------------------------|---------------------------|---------------------|---------------------------|--------|

| AC Accuracy                                |                                                                  |                           |                     |                           |        |

|                                            | f <sub>in</sub> = 1 kHz, V <sub>REF</sub> = 5 V external REF     | 84.7                      | 89.4                |                           | dB     |

| SNR                                        | f <sub>in</sub> = 1 kHz, V <sub>REF</sub> = 4.096 V internal REF | 83.5                      | 88.2                |                           | dB     |

|                                            | f <sub>in</sub> = 1 kHz, V <sub>REF</sub> = 5 V external REF     | 84.1                      | 89.2                |                           | dB     |

| SINAD                                      | f <sub>in</sub> = 1 kHz, V <sub>REF</sub> = 4.096 V internal REF | 83                        | 88.1                |                           | dB     |

| Dynamic Range                              | f <sub>in</sub> = 1 kHz                                          |                           | 90.2                |                           | dB     |

| THD                                        | f <sub>in</sub> = 1 kHz                                          |                           | -103                |                           | dB     |

| SFDR                                       | f <sub>in</sub> = 1 kHz                                          |                           | -105                |                           | dB     |

| DC Accuracy                                |                                                                  |                           |                     |                           |        |

| Resolution                                 | NO MISSING CODE                                                  | 16                        |                     |                           | Bits   |

| DNL                                        | V <sub>REF</sub> = 5 V external REF                              | -0.99                     | ±0.55               | 1.1                       | LSB    |

| INL                                        | V <sub>REF</sub> = 5 V external REF                              | -3.3                      | ±1.5                | 2.3                       | LSB    |

| Gain Error                                 |                                                                  | -14                       | ±3                  | 29                        | LSB    |

| Gain Error Match                           |                                                                  |                           | ±3.8                |                           | LSB    |

| Gain Error<br>Temperature Drift            |                                                                  |                           | ±0.8                |                           | ppm/°C |

| Offset Error                               |                                                                  | -14                       | <u>+</u> 9          | 14                        | LSB    |

| Offset Error Match                         |                                                                  |                           | ±2.6                |                           |        |

| Offset Error<br>Temperature Drift          |                                                                  |                           | ±0.3                |                           | ppm/°C |

| Power Supply Sensitivity                   | AVDD +/-5%                                                       |                           | 0.8                 |                           | LSB    |

| Analog Input                               |                                                                  | <u> </u>                  |                     |                           | 1      |

|                                            | Unipolar Mode                                                    | 0                         |                     | +V <sub>REF</sub>         | V      |

| Voltage Range                              | Bipolar Mode                                                     | -V <sub>REF</sub> /2      |                     | +V <sub>REF</sub> /2      | V      |

|                                            | Positive input, unipolar and bipolar modes                       | - 0.1                     |                     | V <sub>REF</sub> + 0.1    | V      |

| Absolute Input Voltage                     | Negative or COM input, unipolar mode                             | - 0.1                     |                     | + 0.1                     | V      |

|                                            | Negative or COM input, bipolar mode                              | V <sub>REF</sub> /2 - 0.1 | V <sub>REF</sub> /2 | V <sub>REF</sub> /2 + 0.1 | V      |

| Analog Input CMRR                          | f <sub>in</sub> = 1 kHz                                          |                           | 75                  |                           | dB     |

| Leakage Current at 25°C<br>Input Impedance | Acquisition phase                                                |                           | 1                   |                           | nA     |

| Input Capacitance                          | ADC sampling capacitor                                           |                           | 35                  |                           | pF     |

| Throughput                                 | ·                                                                | · · · ·                   |                     |                           | 1      |

|                                            | Full Bandwidth                                                   |                           |                     | 1000                      | kSPS   |

| Conversion Rate                            |                                                                  |                           |                     |                           | kSPS   |

| Parameter                         | Test Conditions                                         | Min             | Тур             | Max           | Unit   |

|-----------------------------------|---------------------------------------------------------|-----------------|-----------------|---------------|--------|

| REF Output Voltage                |                                                         | 4.086           | 4.096           | 4.106         | V      |

| REFIN Output Voltage              |                                                         |                 | 4.096           |               | V      |

| REF Output Current                |                                                         |                 | ±300            |               | μA     |

| Temperature Drift                 |                                                         |                 | ±10             |               | ppm/°C |

| Line Regulation                   | VDD = 5 V ± 5%                                          |                 | ±10             |               | ppm/V  |

| Turn-On Settling Time             | CREF = 10 µF                                            |                 | 2               |               | ms     |

| External Reference <sup>(1)</sup> |                                                         |                 |                 |               |        |

|                                   | REF input                                               | 2               |                 | VDD           | V      |

| Voltage Range                     | REFIN input (buffered)                                  | 2               |                 | VDD-0.3       | V      |

| Current Drain                     | 1 MSPS, REF = 5 V                                       |                 | 300             |               | μA     |

| Temperature Sensor                |                                                         |                 |                 | -             |        |

| Output Voltage                    | At 25°C                                                 |                 | 755             |               | mV     |

| Temperature Sensitivity           |                                                         |                 | -1.67           |               | mV/°C  |

| Sampling Dynamics                 |                                                         |                 |                 |               |        |

|                                   | Full bandwidth                                          |                 | 14              |               | MHz    |

| –3 dB Input Bandwidth             | 1⁄4 bandwidth                                           |                 | 3.6             |               | MHz    |

| Aperture Delay                    | VDD = 5 V                                               |                 | 6               |               | ns     |

| Digital Input                     |                                                         |                 |                 |               |        |

| V <sub>IH</sub>                   |                                                         | 0.7 × VIO       |                 | VIO + 0.3     | V      |

| VIL                               |                                                         | -0.3            |                 | 0.3 × VIO     | V      |

| Ін                                | Input Current                                           |                 | ±2              |               | uA     |

| IIL                               | Input Current                                           |                 | ±2              |               | uA     |

| Digital Output                    |                                                         |                 |                 | -             |        |

|                                   | Unipolar mode                                           | Serial 16bit st | raight binary   |               |        |

| Data Format                       | Bipolar mode                                            | Serial 16-bit t | wos complem     | ent           |        |

| Dinalina Dalay                    |                                                         | Conversion re   | sults available | e immediately |        |

| Pipeline Delay                    |                                                         | after complete  | ed conversion   | 1             |        |

| Vон                               | Isource = -500 µA                                       | VIO - 0.2       |                 |               | V      |

| V <sub>OL</sub>                   | I <sub>SINK</sub> = +500 μA                             |                 |                 | 0.2           | V      |

| Power Supply                      |                                                         |                 |                 |               |        |

| VDD                               | Specified performance                                   | 4.5             |                 | 5.5           | V      |

| VIO                               | Specified performance                                   | 1.8             |                 | VDD + 0.3     | V      |

| Power Dissipation                 | VDD = 5 V, 1 MSPS throughput with<br>internal reference |                 | 38              |               | mW     |

| Temperature Range                 | Specified performance                                   | -40             |                 | +125          | °C     |

(1) Parameters are provided by lab bench test and design simulation.

# Timing Requirements <sup>(1)</sup>

All test conditions is at VDD= 5.0 V, VIO = 1.8 V to 5 V,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted.

|                    | Parameter                                               | Min                   | Тур | Мах | Unit |

|--------------------|---------------------------------------------------------|-----------------------|-----|-----|------|

| t <sub>CONV</sub>  | Conversion Time: CNV Rising Edge to Data Available      |                       |     | 668 | ns   |

| t <sub>ACQ</sub>   | Acquisition Time                                        | 332                   |     |     | ns   |

| tcyc               | Time Between Conversions                                | 1                     |     |     | μs   |

| t <sub>CNVH</sub>  | CNV Pulse Width                                         | 10                    |     |     | ns   |

| t <sub>DATA</sub>  | Data Write/Read During Conversion                       |                       |     | 263 | ns   |

| tscк               | SCK Period                                              | t <sub>DSDO</sub> + 2 |     |     | ns   |

| t <sub>SCKL</sub>  | SCK Low Time                                            | 8                     |     |     | ns   |

| t <sub>scкн</sub>  | SCK High Time                                           | 8                     |     |     | ns   |

| <b>t</b> HSDO      | SCK Falling Edge to Data Remains Valid                  | 5                     |     |     | ns   |

| t <sub>DSDO</sub>  | SCK Falling Edge to Data Valid Delay                    |                       |     |     |      |

|                    | VIO Above 4.5 V                                         |                       |     | 15  | ns   |

|                    | VIO Above 3 V                                           |                       |     | 15  | ns   |

|                    | VIO Above 2.7 V                                         |                       |     | 15  | ns   |

|                    | VIO Above 2.3 V                                         |                       |     | 15  | ns   |

|                    | VIO Above 1.8 V                                         |                       |     | 16  | ns   |

| t <sub>EN</sub>    | CNV Low to SDO D15 MSB Valid                            |                       |     |     |      |

|                    | VIO Above 4.5 V                                         |                       |     | 19  | ns   |

|                    | VIO Above 3 V                                           |                       |     | 20  | ns   |

|                    | VIO Above 2.7 V                                         |                       |     | 21  | ns   |

|                    | VIO Above 2.3 V                                         |                       |     | 21  | ns   |

|                    | VIO Above 1.8 V                                         |                       |     | 23  | ns   |

| t <sub>DIS</sub>   | CNV High or Last SCK Falling Edge to SDO High Impedance |                       |     | 32  | ns   |

| t <sub>CLSCK</sub> | CNV Low to SCK Rising Edge                              | 10                    |     |     | ns   |

|                    | Last SCK Falling Edge to CNV Rising Edge Delay          | 40                    |     |     | ns   |

| t <sub>SDIN</sub>  | DIN Valid Setup Time from SCK Rising Edge               | 5                     |     |     | ns   |

| t <sub>HDIN</sub>  | DIN Valid Hold Time from SCK Rising Edge                | 5                     |     |     | ns   |

(1) Parameters are provided by design simulation.

### **Typical Performance Characteristics**

All test conditions is at VDD = 5 V, V<sub>REF</sub> = 5 V, VIO = 5 V, unless otherwise noted.

# **TPC51701**

# 16-Bit 8-Channel 1-MSPS SAR ADC

## **Detailed Description**

### Overview

The TPC51701 is a 8-channel, 16-bit, 1-MSPS successive approximation register (SAR) ADC. It is a compact solution for multi-channel data acquisition with high resolution ADC, 8-channel high isolation multiplexer including flexible channel sequencer, internal reference and buffer, internal temperature sensor for monitoring and configurable analog low-pass filter. ADC communicates with host through simple SPI serial interface. There are several options to read/wirte ADC data, which are during conversion, after conversion and spanning conversion.

The TPC51701 is specified from 4.5 V to 5.5 V VDD supply and interface digital logic supply offers wide range from 1.8 V to 5 V to compatible with host. The device is in compact 20-lead, 4 mm x 4 mm QFN package and is also pin compitable with other TPC517xx family products.

### Functional Block Diagram

Figure 5. TPC51701 Block Diagram

### **Feature Description**

#### Analog Input Configurations

TPC51701 input is configurable through register (CFG[12:10]). Generally, the positive input range is 0 V to  $V_{REF}$  V. Negative input or COM input should be referenced to ground for unipolar input case, and be referenced to  $V_{REF}/2$  for bipolar input case. The following is detailed description of available input type configurations:

- 1. INx is single-ended input referenced to system ground; CFG[12:10] = 'b111.

- Bipolar differential with a common reference COM = V<sub>REF</sub>/2. INx is differential positive input and COM is common negative input; CFG[12:10] = 'b010.

- 3. Unipolar differential with a common reference COM connected to ground. INx is differential positive input and COM is common negative input; CFG[12:10] = 'b110.

- Bipolar differential pairs INx+ and INx- with INx- referenced to V<sub>REF</sub>/2; CFG[12:10] = 'b00X. INx+ is defined in channel configuration CFG[9:7].

- 5. Unipolar differential pairs INx+ and INx- with INx- referenced to ground; CFG[12:10] = 'b10X. INx+ is defined in channel configuration CFG[9:7].

- 6. Combinations of any above input types.

#### Sequencer

The TPC51701 incorpertes a highly flexible sequencer. The sequencer changes the input channel automatically configured in the register. Channels could be scanned as following modes, singles or pairs, with or without the temperature sensor (after the last channel is coverted).

The sequencer always starts with channel IN0 and ends up with the channel set in register CFG[9:7]. In input channel pairs mode, the last channel pair is set inCFG[9:7]. The channel pairs are paired as following way, IN (even) is the IN+ and IN (odd) is the IN-.

In order to enable the sequencer, the CFG[2:1] register is set to initialize the sequencer. After CFG[13:0] are updated, DIN must be held low while reading data out (at least for Bit 13), or the CFG register begins updating again.

While in a sequence operation, the CFG register can be changed by writing 01 to CFG[2:1]. If changing CFG11 (paired or single channel) or CFG[9:7], the sequence will reinitialize and convert IN0 (or IN1) after CFG is updated.

#### Voltage Reference Input/Output

The TPC51701 intergrates a high precision internal reference with buffer, and also supports external reference input.

The internal reference is 4.096 V output. If internal reference is enabled, the reference voltage is present on the REFIN pin.

The internal temperature sensor is active only when internal reference is enabled (internal reference buffer can be disabled). The internal temperature sensor output voltage is single-ended conversion, straight binary refers to the ADC GND pin

The external reference is optional only if high performance reference voltage is needed. The external reference is input through REFIN and internal reference buffer could be used.

#### ADC Transfer Function

For unipolar input configuration, that is single ended, differential with COM connected to ground, and diffrential pairs with INxreferenced to ground, the output data is in straight binary format.

For bipolar input configuration, that is differential with COM connected to  $V_{REF}/2$ , and diffrential pairs with INx- referenced to  $V_{REF}/2$ , the output data is in twos complement format.

| Description      | Unipolar Analog Input<br>V <sub>REF</sub> = 4.096 V | Digital Output Code<br>(Straight Binary Hex) | Bipolar Analog Input<br>V <sub>REF</sub> = 4.096 V | Digital Output Code<br>(Twos Complement<br>Hex) |  |

|------------------|-----------------------------------------------------|----------------------------------------------|----------------------------------------------------|-------------------------------------------------|--|

| FSR – 1 LSB      | 4.095938 V                                          | 0xFFFF                                       | 2.047938 V                                         | 0x7FFF                                          |  |

| Midscale + 1 LSB | 2.048063 V                                          | 0x8001                                       | 62.5 μV                                            | 0x0001                                          |  |

| Midscale         | 2.048 V                                             | 0x8000                                       | 0 V                                                | 0x0000                                          |  |

| Midscale - 1 LSB | 2.047938 V                                          | 0x7FFF                                       | −62.5 μV                                           | 0xFFFF                                          |  |

| -FSR + 1 LSB     | 62.5 μV                                             | 0x0001                                       | -2.047938 V                                        | 0x8001                                          |  |

| -FSR             | 0 V                                                 | 0x0000                                       | -2.048 V                                           | 0x8000                                          |  |

#### Digital Interface

The TPC51701 offers a simple 4-wire serial interface that is compatible with SPI. The digital interface uses CNV, DIN, SCK and SDO for serial interface communication

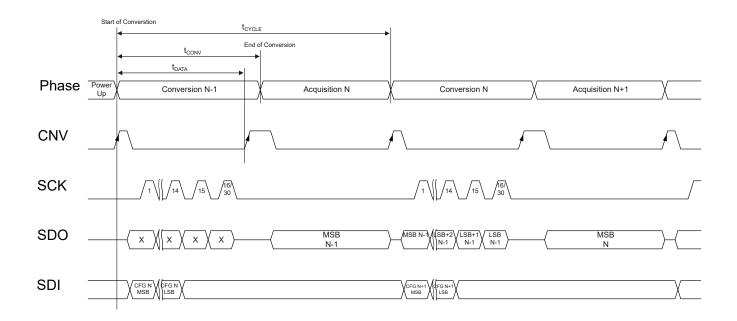

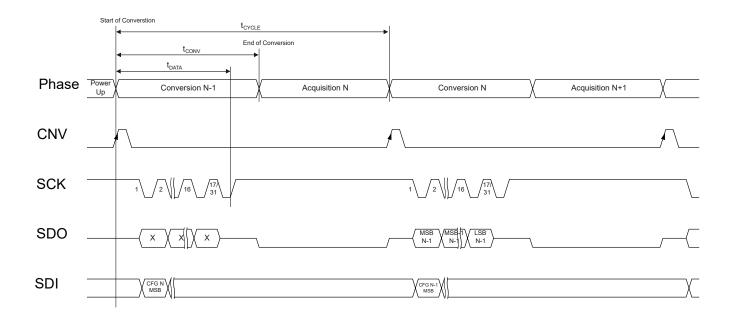

#### Reading/Writing during Conversion

Data reading and writing operation is completed within conversion phase. When reading/writing during conversion N, conversion results are for the previous N-1 conversion, and writing the CFG is for the next N+1 acquisition and conversion.

#### Reading/Writing during Conversion

Data reading and writing operation is completed within conversion phase. When reading/writing during conversion N, conversion results are for the previous N-1 conversion, and writing the CFG is for the next N+1 acquisition and conversion.

Initially, CNV is brought high to start conversion, and CNV must be brought low to enable reading/writing during conversion. It should be noticed that reading/writing must be finished within t<sub>DATA</sub>, thus the SCK frequency is limited by:

$$f_{SCK} \geq \frac{\text{Number of SCK edges}}{t_{DATA}}$$

(1)

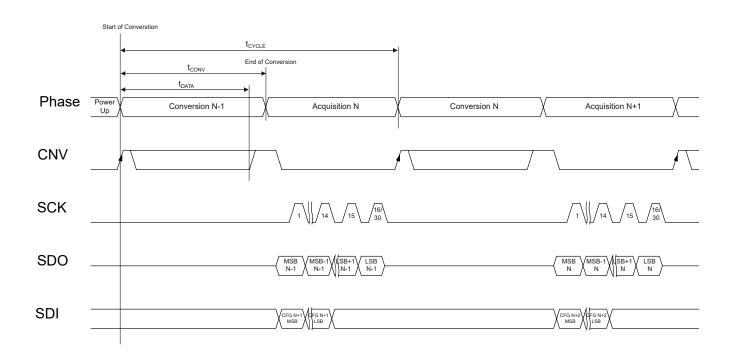

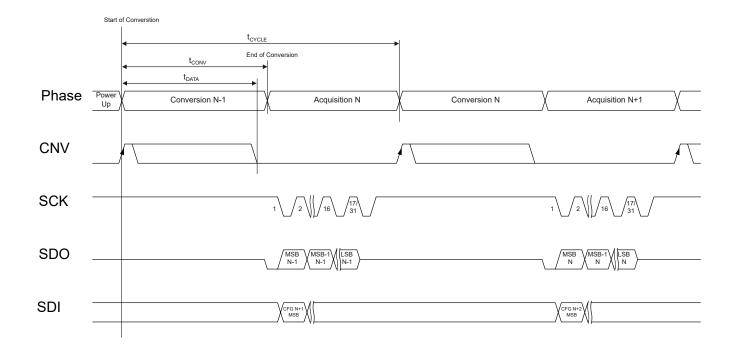

#### Reading/Writing after Conversion (During Acquisition)

Data reading and writing operation is completed within acquisition phase. When reading/writing during acquisition N, conversion results are for the previous N-1 conversion, and writing the CFG is for the next N+1 acquisition and conversion.

Maximum throughput is limited by finishing reading/writing within min t<sub>ACQ</sub>. There is no limit for slow throughput rate which is required by user. Further more, reading/writing still must be within acquisition phase.

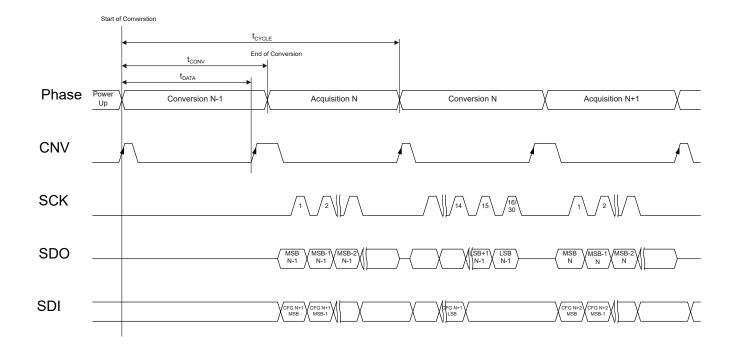

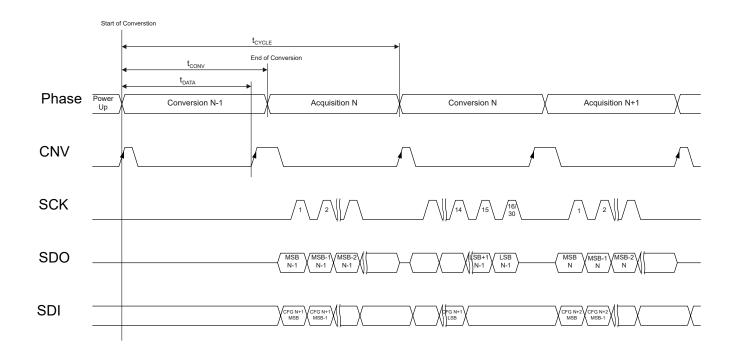

#### Reading/Writing Spanning Conversion

Data reading and writing operation is across acquisition and conversion phase. The data access starts at the current acquisition N and spans into the conversion N. Conversion results are for the previous N-1 conversion, and writing the CFG register is for the next N+1 acquisition and conversion.

Similarly, reading/writing must be within  $t_{DATA}$  in converstion phase and maximum throughput is limited by min  $t_{ACQ}$  time in acquisition phase. On the whole, the total time limit for maximum throughput is min  $t_{ACQ}$  time +  $t_{DATA}$  time.

The host can run at any low throughput rateand reading/writing should be taken place druing acquisition phase with additional time into the conversion.

Spanning conversion requires CNV pulled high to start conversion, and data access is not allowed when CNV is high.

#### Reigister Configuration, CFG

There is a 14-bit configuration register CFG[13:0] in the device. The CFG register is latched (MSB first) on DIN with 14 SCK rising edges. CFG update is edge dependent, allowing for asynchronous or synchronous hosts. The register can be written to during conversion, during acquisition, or spanning acquisition/conversion and is updated at the end of conversion, tCONV (maximum). It should be noticed that at power-up, the CFG register is undefined and two dummy conversions are required

to update the register. The CFG word is updated on the first 14 SCK rising edges. If the CFG readback is enabled, an additional 14 SCK falling edges are required to output the CFG word associated with the conversion results, with the CFG MSB following the LSB of the conversion result.

| Bit(s)  | Name | Description                                         |                     |           |                                                                                                                                                                 |  |  |  |  |

|---------|------|-----------------------------------------------------|---------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| [13]    | CFG  |                                                     | p curre             | nt config | uration settings.                                                                                                                                               |  |  |  |  |

|         |      | Input ch                                            | annel c             | onfigura  | of register.<br>tion. Selection of pseudobipolar, pseudodifferential, pairs, single-ended, or                                                                   |  |  |  |  |

|         |      | temperature sensor.   Bit 12 Bit 11 Bit 10 Function |                     |           |                                                                                                                                                                 |  |  |  |  |

|         |      | 0                                                   | 0                   | X         | Bipolar differential pairs; INx- referenced to VREF/2 ± 0.1 V.                                                                                                  |  |  |  |  |

| [10,10] | INCC | 0                                                   | 1                   | 0         | Bipolar; INx referenced to COM = VREF/2 $\pm$ 0.1 V.                                                                                                            |  |  |  |  |

| [12:10] | INCC | 0                                                   | 1                   | 1         | Temperature sensor.                                                                                                                                             |  |  |  |  |

|         |      | 1                                                   | 0                   | X         | Unipolar differential pairs; $INx-$ referenced to GND ± 0.1 V.                                                                                                  |  |  |  |  |

|         |      | 1                                                   | 1                   | 0         | Unipolar, IN0 to IN7 referenced to COM = $GND \pm 0.1 V$ (GND sense).                                                                                           |  |  |  |  |

|         |      | 1                                                   | 1                   | 1         | Unipolar, IN0 to IN7 referenced to GND.                                                                                                                         |  |  |  |  |

|         |      | Input ch                                            | annel s             | election  | in binary fashion.                                                                                                                                              |  |  |  |  |

|         |      | Bit 9                                               | Bit 8               | Bit 7     | Channel                                                                                                                                                         |  |  |  |  |

|         |      | 0                                                   | 0                   | 0         | INO                                                                                                                                                             |  |  |  |  |

| [9:7]   | INx  | 0                                                   | 0                   | 1         | IN1                                                                                                                                                             |  |  |  |  |

|         |      |                                                     |                     |           |                                                                                                                                                                 |  |  |  |  |

|         |      | 1                                                   | 1                   | 1         | IN7                                                                                                                                                             |  |  |  |  |

| [6]     | BW   | 0 = ¼ of                                            | f BW, u<br>so be re |           | v-pass filter. Refer to the Selectable Low-Pass Filter section.<br>dditional series resistor to further bandwidth limit the noise. Maximum throughput<br>0.1/4. |  |  |  |  |

|         |      |                                                     |                     |           | on. Selection of internal, external, and external buffered references, and enabling<br>ure sensor. Refer to the Voltage Reference Output/Input section.         |  |  |  |  |

|         |      | Bit 5                                               | Bit 4               | Bit 3     | Function                                                                                                                                                        |  |  |  |  |

|         |      | 0                                                   | 0                   | 0         | Do not use.                                                                                                                                                     |  |  |  |  |

|         |      | 0                                                   | 0                   | 1         | Internal reference and temperature sensor enabled. REF = 4.096 V buffered output.                                                                               |  |  |  |  |

| [5:3]   | REF  | 0                                                   | 1                   | 0         | Use external reference. Temperature sensor enabled. Internal buffer disabled.                                                                                   |  |  |  |  |

|         |      | 0                                                   | 1                   | 1         | Use external reference. Internal buffer and temperature sensor enabled.                                                                                         |  |  |  |  |

|         |      | 1                                                   | 0                   | 0         | Do not use.                                                                                                                                                     |  |  |  |  |

|         |      | 1                                                   | 0                   | 1         | Do not use.                                                                                                                                                     |  |  |  |  |

|         |      | 1                                                   | 1                   | 0         | Use external reference. Internal reference, internal buffer and temperature sensor disabled.                                                                    |  |  |  |  |

#### Table 2. Register Description

| Bit(s) | Name |                                                     | Description                                                                                              |         |                                                                                                      |  |  |  |  |  |  |

|--------|------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------|------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|        |      | 1                                                   | 1                                                                                                        | 1       | Use external reference. Internal buffer enabled. Internal reference and temperature sensor disabled. |  |  |  |  |  |  |

|        |      | Channe                                              | Channel sequencer. Allows scanning channels in an IN0 to IN[7:0] fashion. Refer to the Sequencersection. |         |                                                                                                      |  |  |  |  |  |  |

|        |      | Bit 2                                               | Bit 1                                                                                                    | Functio | ion                                                                                                  |  |  |  |  |  |  |

| [2:4]  | SEQ  |                                                     | 0                                                                                                        | Disable | Disable sequencer.                                                                                   |  |  |  |  |  |  |

| [2:1]  | SEQ  | 0                                                   | 1                                                                                                        | Update  | configuration during sequence.                                                                       |  |  |  |  |  |  |

|        |      | 1                                                   | 0                                                                                                        | Scan IN | an IN0 to IN[7:0] (set in CFG[9:7]), then temperature.                                               |  |  |  |  |  |  |

|        |      | 1                                                   | 1                                                                                                        | Scan IN | 0 to IN[7:0] (set in CFG[9:7]).                                                                      |  |  |  |  |  |  |

|        |      | Read back the CFG register.                         |                                                                                                          |         |                                                                                                      |  |  |  |  |  |  |

| 0      | RB   | 0 = Read back current configuration at end of data. |                                                                                                          |         |                                                                                                      |  |  |  |  |  |  |

|        |      | 1 = Do i                                            | 1 = Do not read back contents of configuration.                                                          |         |                                                                                                      |  |  |  |  |  |  |

#### General Timing without a Busy Indicator

Following figures illustrate the general timing without a busy indication for reading/writing during conversion, after conversion and spanning conversion mode. The busy indicator is disabled if CNV is high at the end of conversions.

A CNV rising edge starts a conversion, forces SDO to high impedance and ignores SDI data input. Once conversion is initiated, it it continues until completion irrespective of the state of CNV. However, CNV should be returned to high before safe data time t<sub>DATA</sub> and hold high until conversion period is completed, in oder to disable busy indicator.

After the conversion phase, the ADC starts acquisition. Once CNV is brought low after EOC (End of Conversion), SDO is driven from high impedance to the MSB. The MSB of CFG should be also be presented on SDI if necessary for CFG update. When CNV is low, both CFG configuration and data readback operation is available. The first 14 SCK rising edges update the CFG, and the first 15 SCK falling edges trigger out the conversion results starting with MSB – 1. Data access is limited within safe data reading/writing time, t<sub>DATA</sub>. If the full configuration 14 bits of CFG[13:0] word was not written to before EOC, it is discarded and the current configuration remains. If the 16 bits conversion result is not read out fully within t<sub>DATA</sub>prior to end of conversions, it is lost as the ADC updates SDO with the MSB of the current conversion and falling SCK edges clock out bits starting with MSB–1.

The SDO data is available for both SCK edges. After the 16th or 30th (plus 14 bits CFG readback) SCK falling edge, or when CNV goes high (whichever occurs first), SDO returns to high impedance.

If CFG readback is enabled, the CFG is read back MSB first following the LSB of the conversion result. A total of 30 SCK falling edges is required to return SDO to high impedance if this is enabled.

#### Figure 6. General Interface Timing for Read/Write during Conversion without a Busy Indicator

#### Figure 7. General Interface Timing for Read/Write after Conversion without a Busy Indicator

# **TPC51701**

# 16-Bit 8-Channel 1-MSPS SAR ADC

#### Figure 8. General Interface Timing for Read/Write Spanning Conversion without a Busy Indicator

#### General Timing with a Busy Indicator

Following figures illustrate the general timing with a busy indicatior for reading/writing during conversion, after conversion and spanning conversion mode. The busy indicator is enabled if CNV is low at the end of conversions. SDO should be returned to high impedance to generate busy indicator properly.

A CNV rising edge starts a conversion, forces SDO to high impedance and ignores SDI data input. Once conversion is initiated, it it continues until completion irrespective of the state of CNV. However, CNV should be returned to low before safe data time t<sub>DATA</sub> and hold low until conversion period is completed, in oder to enable busy indicator. When the conversion is finished, SDO changes from high impedance to low, if SDO is pulled-up to VIO, a falling edge on SDO acting as a busy indicator interrupt host to start data transfer.

After the conversion phase, the ADC starts acquisition. Once CNV is low after EOC (End of Conversion), the MSB of CFG should be also be presented on SDI if necessary for CFG update. When CNV is low, both CFG configuration and data readback operation is available. The first 14 SCK rising edges update the CFG, and the first 16 SCK falling edges trigger out the conversion results starting with MSB. Data access is limited within safe data reading/writing time, t<sub>DATA</sub>. If the full configuration 14 bits of CFG[13:0] word was not written to before EOC, it is discarded and the current configuration remains. If the 16 bits conversion result is not read out fully within t<sub>DATA</sub> prior to end of conversions, it is lost.

The SDO data is available for both SCK edges. Only after the 17th SCK falling edge, SDO returns to high impedance. It should be noted that if optional 17th (or 31th) SCK falling edge is not used, the busy feature cannot be detected if the LSB for the conversion is just low.

If CFG readback is enabled, the CFG is read back MSB first following the LSB of the conversion result. A total of 31 SCK falling edges is required to return SDO to high impedance if this is enabled.

#### Figure 9. General Interface Timing for Read/Write during Conversion with a Busy Indicator

# **TPC51701**

# 16-Bit 8-Channel 1-MSPS SAR ADC

#### Figure 10. General Interface Timing for Read/Write after Conversion with a Busy Indicator

#### Figure 11. General Interface Timing for Read/Write Spanning Conversion with a Busy Indicator

## **Application and Implementation**

Note

Information in the following application sections is not part of the 3PEAK's component specification and 3PEAK does not warrant its accuracy or completeness. 3PEAK's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### **Typical Application**

Figure 12. Typical Application Diagram

| Table 3. Recommended 3PEAK ADC Dri | ver Amplifiers |

|------------------------------------|----------------|

|------------------------------------|----------------|

| Part<br>Number | СН | VDD<br>(V) | GBWP<br>(MHz) | Slew Rate<br>(V/µs) | eN@1kHz<br>(nV/√Hz) | IBIAS<br>(pA) | VOS (max)<br>(mV) | VOS TC<br>(μV/°C) | Package           |  |

|----------------|----|------------|---------------|---------------------|---------------------|---------------|-------------------|-------------------|-------------------|--|

| TPA2681        | 1  | 8~36       | 20            | 10                  | 10                  | 100000        | 3                 | 2                 | SOT23-5           |  |

| TPA2682        | 2  | 8~36       | 20            | 10                  | 10                  | 100000        | 3                 | 2                 | SOP8,MSOP8        |  |

| TPA1881        | 1  | 4.5~36     | 12            | 10                  | 6                   | 500           | 0.02              | 0.05              | SOT23-5,SOP8      |  |

| TPA1882        | 2  | 4.5~36     | 12            | 10                  | 6                   | 500           | 0.02              | 0.05              | SOP8,MSOP8        |  |

| TPA2671        | 1  | 4~36       | 10            | 15                  | 38                  | 50            | 3                 | 0.5               | SOT23-5,SOT353    |  |

| TPA2672        | 2  | 4~36       | 10            | 15                  | 38                  | 50            | 3                 | 0.5               | MSOP8,TSSOP8,SOP8 |  |

| TPA2674        | 4  | 4~36       | 10            | 15                  | 38                  | 50            | 3                 | 0.5               | SOP14,TSSOP14     |  |

#### Table 4. Recommended 3PEAK Voltage References

| Part<br>Number | Vin (min)<br>(V) | Vin (max)<br>(V) | Accuracy<br>(max) | TC (-40 to 125 °C)<br>(ppm/°C) | Output Voltage Noise<br>0.1 to 10 Hz (μVpp) | Package     |

|----------------|------------------|------------------|-------------------|--------------------------------|---------------------------------------------|-------------|

| TPR70          | max (Ver+0.2, 3) | 15               | 0.05%             | 3                              | 2.5                                         | SOP8        |

| TPR50          | max (Ver+0.2, 3) | 15               | 0.05%             | 6                              | 7.5                                         | MSOP8, SOP8 |

# **TPC51701**

## 16-Bit 8-Channel 1-MSPS SAR ADC

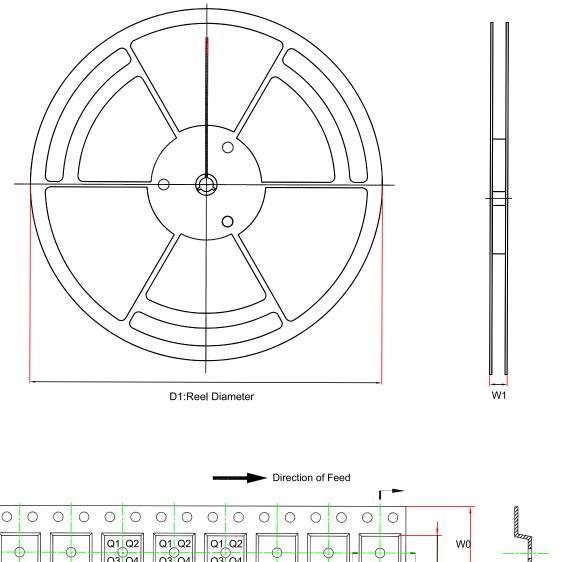

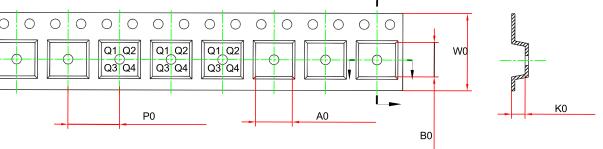

# **Tape and Reel Information**

| Order Number  | Package   | D1 (mm) | W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P0 (mm) | W0 (mm) | Pin1<br>Quadrant |

|---------------|-----------|---------|---------|---------|---------|---------|---------|---------|------------------|

| TPC51701-QFOR | QFN4X4-20 | 330     | 17.6    | 4.3     | 4.3     | 1.1     | 8.0     | 12.0    | Q2               |

### **Package Outline Dimensions**

### QFN4X4-20

### **Order Information**

| Order Number  | Operating Temperature<br>Range | Package   | Marking Information | MSL | Transport Media, Quantity | Eco Plan |

|---------------|--------------------------------|-----------|---------------------|-----|---------------------------|----------|

| TPC51701-QFOR | −40 to 125°C                   | QFN4X4-20 | 51701               | 3   | Tape and Reel, 3000       | Green    |

(1) For future products, contact the 3PEAK factory for more information and sample.

Green: 3PEAK defines "Green" to mean RoHS compatible and free of halogen substances.