#### **Features**

- 16-bit Resolution and Monotonicity

- Output Ports being UIO Compatible, Terminals Tolerant to ±50 V with Diodes

- Current Output Ranges: 4 mA to 20 mA, 0 mA to 20 mA, or 0 mA to 24 mA

- Typical ±0.05% FSR Total Unadjusted Error (TUE)

- Leakage Compensation in Current Mode

- HART Connectivity

- Voltage Output Ranges: 0 V to 5 V, 0 V to 10 V, ±5 V, or +10 V

- Typical ±0.06% FSR Total Unadjusted Error (TUE)

- 20% Over-range Available

- Support Four-wire Voltage in Voltage Mode

- 12-bit ADC for Readback Output Voltage & Current & AVDD

- On-chip Output Fault Detection

- CRC Check

- Watchdog Timer

- Current Output Open Circuit Alarm & Negative Voltage Alarm

- Voltage Output Overcurrent with Direction

- Independent AVDD UVLO

- Over Temperature

- Temperature Range: -40°C to +125°C

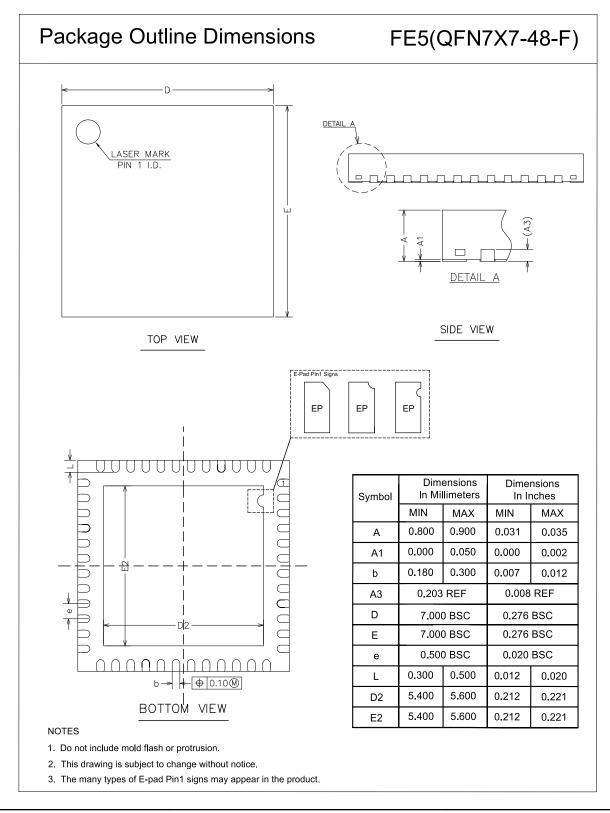

- QFN7×7-48 Packages

### **Applications**

- Industrial Automation

- Process Control

- HART Network Connectivity

- PLC and DCS

### **Description**

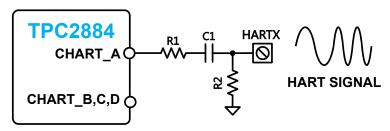

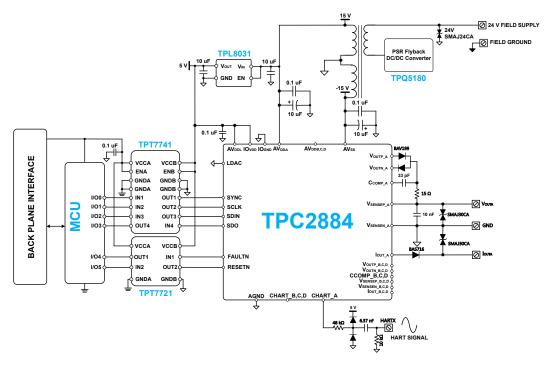

The TPC2884 is a quad-channel voltage and current output digital-to-analog converter (DAC) that operates with a power supply range from -27 V to +50 V. The AV<sub>DD</sub> pin for each channel provides an independent positive power supply with a range of 7 V to 50 V, which can be used with an external adaptive power supply to reduce chip heating, and External resistance can also be connected in series with the AV<sub>DD</sub> to achieve a switchable HART impedance in LOOP\_POWER current input mode. In the current output mode, each channel has an independent HART injection PIN to transmit HART.

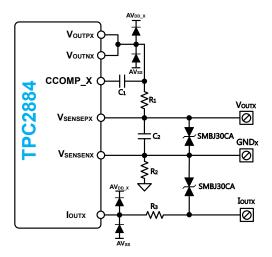

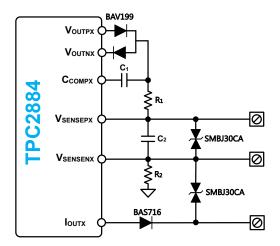

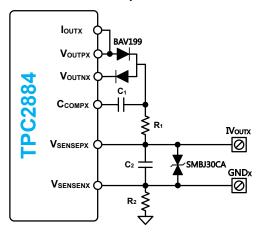

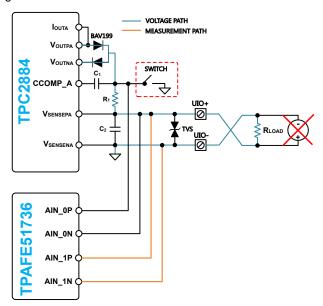

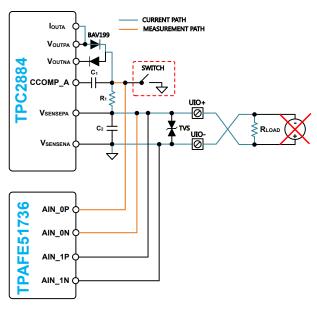

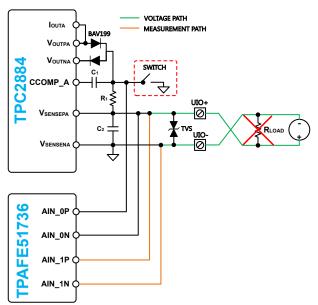

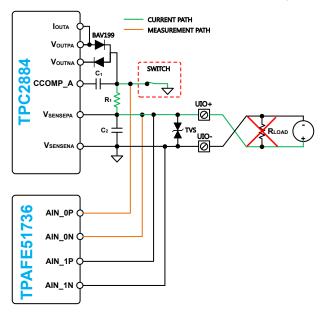

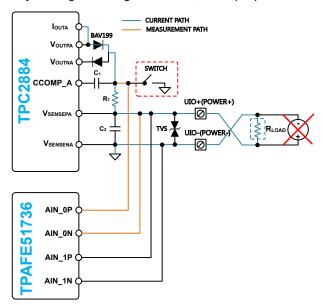

The device in voltage output mode provides a five-wire output with the addition of an external diode to prevent backfill and high withstand voltage over the rail, as well as to compensate for voltage drops in traces and ports. In the current output mode, there is an output open-loop detection, and in order to reduce the leakage error of the (UIO) mode and the ADC input, the output impedance compensation is built in, and there is also a negative voltage detection to identify wiring faults. The device is UIO mode compatible, the voltage output PIN can be combined with the current output PIN, and for analog input compatibility, it can be used with external diodes to achieve port withstand voltage beyond the power rail, and the withstand voltage can reach ±50 V (± 15 V power supply).

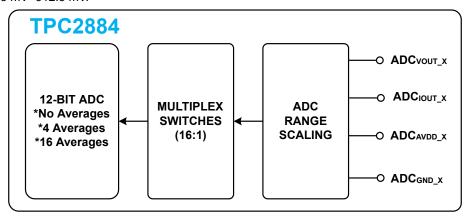

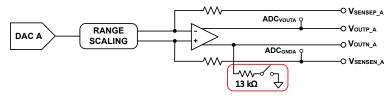

The device has complete diagnosis, including built-in fault detection and a 12-bit ADC for port voltage readback. Built-in fault detection includes overcurrent direction of voltage output, current output loop break and negative voltage, power supply and output status, over-temperature protection, CRC calibration, SPI watchdog, etc. The built-in ADC reads back the voltage and current of each channel and the positive supply voltage, providing more flexible output monitoring.

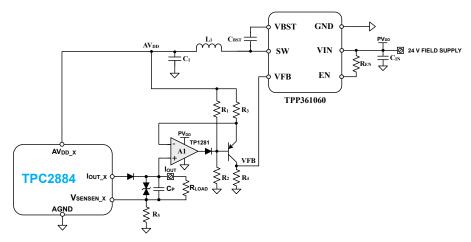

### **Typical Application Circuit**

www.3peak.com 2 / 80 BA20250401A0

### **Table of Contents**

| Features                                | 1  |

|-----------------------------------------|----|

| Applications                            | 1  |

| Description                             | 1  |

| Typical Application Circuit             | 2  |

| Product Family Table                    | 4  |

| Revision History                        | 4  |

| Pin Configuration and Functions         | 5  |

| Specifications                          | 8  |

| Absolute Maximum Ratings <sup>(1)</sup> | 8  |

| ESD, Electrostatic Discharge Protection | 8  |

| Recommended Operating Conditions        | 9  |

| Thermal Information                     | 9  |

| Electrical Characteristics              | 10 |

| Timing Requirements                     | 16 |

| Timing Diagrams                         | 17 |

| Typical Performance Characteristics     | 19 |

| Detailed Description                    | 29 |

| Overview                                | 29 |

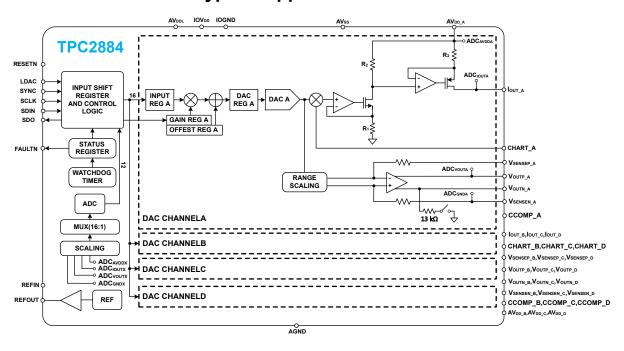

| Functional Block Diagram                | 29 |

| Feature Description                     | 29 |

| Functional Modes                        | 54 |

| Application and Implementation          | 65 |

| Application Information                 | 65 |

| Typical Application                     | 65 |

| Layout                                  | 75 |

| Layout Guideline                        | 75 |

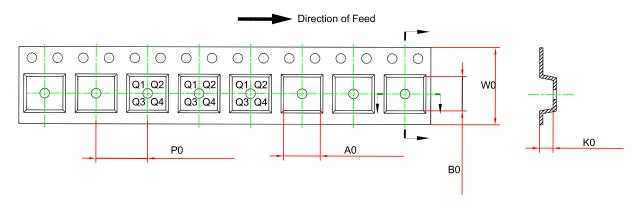

| Tape and Reel Information               | 76 |

| Package Outline Dimensions              | 77 |

| QFN7X7-48-F                             | 77 |

| Order Information                       | 78 |

| IMPORTANT NOTICE AND DISCI AIMER        | 79 |

### **Product Family Table**

| Order Number | Resolution | Output          | Package   |

|--------------|------------|-----------------|-----------|

| TPC2884-FE6R | 16         | Current/Voltage | QFN7X7-48 |

### **Revision History**

| Date       | Revision | Notes                     |

|------------|----------|---------------------------|

| 2025-10-23 | Rev.A.0  | Initial released version. |

www.3peak.com 4 / 80 BA20250401A0

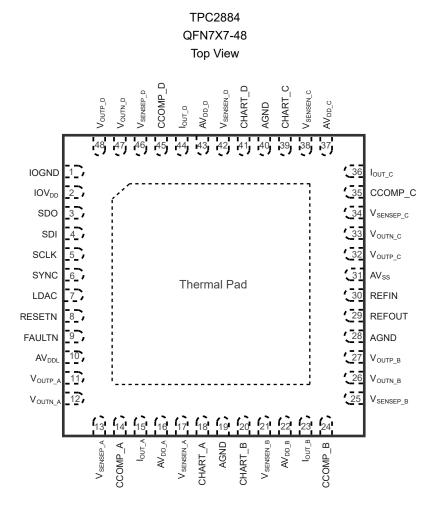

### **Pin Configuration and Functions**

**Table 1. Pin Function Descriptions**

| Pin No. | Pin Name | Description                                                                                                                                                                                                                                                                                                                    |

|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

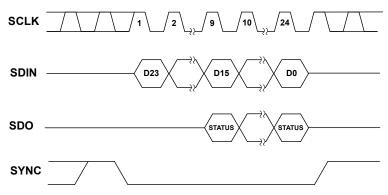

| 6       | SYNC     | Enable pin of the SPI bus, high-impedance input. As an enable signal on the SPI bus, SYNC pulls low, SDO transmits data, SYNC pulls up, the SDO port is high-impedance, and the SPI bus is idle. If the LDAC continues to pull low, the rising edge of the SYNC pin triggers the transfer of newly written data to the output. |

| 4       | SDI      | Data input pin of SPI bus, high impedance input. After the communication starts, enter the DAC data and configuration information.                                                                                                                                                                                             |

| 5       | SLCK     | Clock input pin of the SPI bus, high-impedance input. Provides a clock for SPI communication, updating SDO data on the rising edge of the clock and reading in SDI data on the falling edge of the clock.                                                                                                                      |

| 3       | SDO      | Data output pins on the SPI bus. When the SYNC is pulled down, data is transmitted, the SYNC is pulled up, and the SDO enters a high-impedance state.                                                                                                                                                                          |

www.3peak.com 5 / 80 BA20250401A0

| Pin No.    | Pin Name    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | IOGND       | Digital interface ground pins. For the ground of IOV <sub>DD</sub> and digital modules, it is recommended to connect with AGND at a single point on the circuit board to reduce the interference of digital current to AGND.                                                                                                                                                                                                                                                                                         |

| 2          | $IOV_DD$    | Digital interface power pins. For the power supply of the internal digital interface, a 100nF capacitor is recommended to connect the IOV <sub>DD</sub> to the IOGND.                                                                                                                                                                                                                                                                                                                                                |

| 7          | LDAC        | DAC update pin, high impedance input, low active. The LDAC changes from high to low, triggering all channel data to be updated synchronously to the DAC output. LDAC remains low and the rising edge of the SYNC pin triggers the transfer of newly written data to the output on the SPI bus.                                                                                                                                                                                                                       |

| 9          | FAULTN      | Chip reporting error pins, open-drain output, low validity. Errors include short circuit of output voltage, open circuit of output current, negative voltage of current output, overtemperature and protection, CRC, and Watch Dog. Built-in control registers with selectable output of error messages on the pin.                                                                                                                                                                                                  |

| 8          | RESETN      | On-chip reset pin, high-impedance input, active-low. The RESET pin has a minimum filtering time of 50uS to protect the safety of the function, and the chip can also be RESET through the software register, and the KEY is 0x0555. Performing RESET resets the chip to the power-up state, there is a special indicator bit in the main state register to record the RESET event, after RESET occurs, this bit becomes 1 and remains there, the state is cleared by writing to the 0x0358 in the software register. |

| 10         | $AV_DDL$    | Low-voltage power supply pins. For the internal analog and digital parts, this PIN pin needs to decouple the IOGND and AGND, and it is recommended to connect the 100nF decoupling capacitor to the connection point between the IOGND and AGND to achieve decoupling and interference isolation.                                                                                                                                                                                                                    |

| 29         | REFOUT      | Built-in reference output pin. The on-chip 4.096V reference output, the pin is connected to a 100nF capacitor to the AGND, and can be directly connected to the REFIN pin to input the reference voltage for the chip. There is no need for an internal reference, the pins can be floated                                                                                                                                                                                                                           |

| 30         | REFIN       | Reference input pin. A 4.096V reference is provided for the internal DAC and ADC, and this pin is a resistive input with an impedance of approximately 40K ohms. Using the built-in references, REFIN can be connected to REFOUT. With an external reference, an external reference voltage can be directly connected, and the recommended decoupling capacitance of the REFIN to AGND is 100nF.                                                                                                                     |

| 19,28,40   | AGND        | Chip ground pins. It provides a ground for the chip and is also a reference ground for the reference voltage and the ADC. The three AGND pins require a low-impedance connection to reduce signal cross-talk.                                                                                                                                                                                                                                                                                                        |

| 18,20,39,4 | CHART_(A-D) | HART injection pin for current output. The registers can be optionally turned on and off with the built-in switch, with the option to turn off the HART input and the switch off, which is connected to AGND. Select to turn on the HART input, the switch is on, the HART injection point is low impedance, and the injection current amplitude is set through the external resistor.                                                                                                                               |

| 31         | AVSS        | Negative high voltage power supply pin, shared by four channels, 0V to -26V range. In the case of bipolar voltage output, a negative voltage is provided to the voltage output amplifier, and a 100nF capacitor is recommended for the AGND. When the unipolar voltage output and current output are used, this pin can be connected to AGND.                                                                                                                                                                        |

www.3peak.com 6 / 80 BA20250401A0

| Pin No.         | Pin Name                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16,22,37,4      | AV <sub>DD_(A-D)</sub>  | High voltage power supply pins, four independent channels, power supply range 7-50V. In current output mode, load tracking can be used with an external power supply to reduce heat generation. In voltage output mode, a fixed voltage is recommended for this port. This pin also serves as an input to the internal ADC and is used to monitor changes in the voltage of each channel.                                                                        |

| 14,24,35,4<br>5 | CCOMP_(A-D)             | Voltage output stability compensation pin. When the voltage output load capacitance exceeds 10nF, additional stability compensation is required, and an external capacitor is connected between the voltage output and this pin.                                                                                                                                                                                                                                 |

| 17,21,38,4      | Vsensen_(A-D)           | Voltage and current outputs sense negative pins. This pin is also used as an input to the internal ADC to monitor the output current of the chip, and a resistor is required to be connected to the AGND, 10 ohms is recommended, no backflow current detection is required, and this resistor can be short-circuited.                                                                                                                                           |

| 13,25,34,4<br>6 | Vsensep_(A-D)           | The voltage output senses a positive pin. The difference between V <sub>SENSEP</sub> and V <sub>SENSEN</sub> is the true voltage output. This pin also acts as an input to the internal ADC and monitors the output voltage value when the voltage output is enabled. The pin to ground impedance is 1M ohms.                                                                                                                                                    |

| 12,26,33,4      | Voutn_(A-d)             | Voltage output pull-down pin. It is an open-drain output that can withstand positive and high voltages, and can be used with an external diode to achieve positive and negative high withstand voltages. This pin is connected to the V <sub>OUTP</sub> to form a voltage output stage, and there is a drop-down switch connected to the AGND to control the floating state of the voltage output port.                                                          |

| 11,27,32,4      | V <sub>OUTP_(A-D)</sub> | Voltage output pull-up pin. It is an open-drain output that can withstand negative high voltage, and can be used with an external diode to achieve high positive and negative voltage. This pin is connected to the V <sub>OUTN</sub> to form a voltage output stage, and it can also be combined with the I <sub>OUT</sub> .                                                                                                                                    |

| 15,23,36,4<br>4 | l <sub>out_(A-D</sub> ) | Current output pull-up pin. It is an open-drain output that can withstand negative high voltage, and can be used with an external diode to achieve high positive and negative voltage. The I <sub>OUT</sub> pin also acts as an ADC input to monitor the current output port voltage. The current output port has an impedance of 1M ohms to AGND, and the built-in current compensation function can handle the resistance leakage in the application scenario. |

| 49              | EPAD                    | A thermal pad, located at the bottom of the chip, is equipotential with AVSS . It is recommended that the pad be thermally connected to a copper plane for enhanced thermal performance.                                                                                                                                                                                                                                                                         |

www.3peak.com 7 / 80 BA20250401A0

### **Specifications**

### Absolute Maximum Ratings (1)

All test conditions: T<sub>A</sub> = 25°C, unless otherwise noted.

|                                      | Parameter                                 | Min                    | Max                    | Unit |

|--------------------------------------|-------------------------------------------|------------------------|------------------------|------|

| AV <sub>DD</sub> to AGND             |                                           | -0.3                   | 65                     | V    |

| AVss to AGND                         |                                           | -33                    | 0.3                    | V    |

| AV <sub>DD</sub> to AV <sub>SS</sub> |                                           | -0.3                   | 65                     | V    |

| AV <sub>DDL</sub> to AGND            |                                           | -0.3                   | 6                      | V    |

| IOV <sub>DD</sub> to IOGND           |                                           | -0.3                   | 6                      | V    |

| IOGND to AGND                        |                                           | -0.3                   | 0.3                    | V    |

| Vsensep_(A-D)                        |                                           | AGND -<br>65           | AV <sub>SS</sub> + 65  | V    |

| Vsensen_(A-D)                        |                                           | -0.3                   | 6                      | V    |

| V <sub>OUTP_(A-D)</sub>              |                                           | AV <sub>DD</sub> - 65  | AV <sub>DD</sub> + 0.3 | V    |

| V <sub>OUTN_(A-D)</sub>              |                                           | AV <sub>SS</sub> - 0.3 | AV <sub>SS</sub> + 65  | V    |

| Iout_(A-D)                           |                                           | AV <sub>DD</sub> - 65  | AV <sub>DD</sub> + 0.3 | V    |

| CCOMP_(A-D)                          |                                           | AV <sub>SS</sub> - 0.3 | AV <sub>DD</sub> + 0.3 | V    |

| REFIN,REFOUT,CHART_(A-D)             |                                           | -0.3                   | 6                      | V    |

| Digital Inputs to IOGND              |                                           | -0.3                   | 6                      | V    |

| Digital outputs to IOGND             |                                           | -0.3                   | IOV <sub>DD</sub>      | V    |

| Digital Input Current                |                                           | -10                    | 10                     | mA   |

| TA                                   | Operating Temperature Range               | -40                    | 125                    | °C   |

| T <sub>STG</sub>                     | Storage Temperature Range                 | -65                    | 150                    | °C   |

| TJ                                   | Junction Temperature (T <sub>J</sub> max) |                        | 150                    | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

### **ESD, Electrostatic Discharge Protection**

|     | Parameter                | Condition                  | Minimum Level | Unit |

|-----|--------------------------|----------------------------|---------------|------|

| НВМ | Human Body Model ESD     | ANSI/ESDA/JEDEC JS-001 (1) | ±2            | kV   |

| CDM | Charged Device Model ESD | ANSI/ESDA/JEDEC JS-002 (2) | ±1            | kV   |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

www.3peak.com 8 / 80 BA20250401A0

<sup>(2)</sup> Power dissipated on chip must be derated to keep the junction temperature below 150 °C.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **Recommended Operating Conditions**

Voltage to AGND, unless otherwise noted.

| Parameter                                                     | Min | Nom   | Max  | Unit |

|---------------------------------------------------------------|-----|-------|------|------|

| $AV_{DD_{-}(A-D)} (AV_{DD_{-}(A-D)} +  AV_{SS}  \le 50V)$     | 7   | 15    | 50   | V    |

| $ AV_{SS}(AV_{DD} +  AV_{SS}  \le 50V)$                       | -27 | -15   | 0    | V    |

| IOGND                                                         |     | 0     |      | V    |

| AV <sub>DDL</sub>                                             | 4.5 | 5     | 5.5  | V    |

| IOV <sub>DD</sub> to IOGND                                    | 2.7 | 5     | 5.5  | V    |

| REFIN                                                         |     | 4.096 |      | V    |

| Voltage Output Load Current                                   | -10 |       | 10   | mA   |

| Voltage Output Cap-load                                       | 0   | 1     | 2000 | nF   |

| AV <sub>DD</sub> to I <sub>OUT</sub> Voltage (Output = 24 mA) | 2.7 |       |      | V    |

| Specified Performance Temperature                             | -40 |       | 125  | °C   |

### **Thermal Information**

| Package Type | Reja | R <sub>0</sub> JC(top) | Rејв | ReJC(bot) | Unit |

|--------------|------|------------------------|------|-----------|------|

| QFN7x7-48    | 20   | 7                      | 3    | 2         | °C/W |

www.3peak.com 9 / 80 BA20250401A0

#### **Electrical Characteristics**

All test conditions:  $AV_{DD\_(A-D)} = 7$  V to 50 V,  $AV_{SS} = -27$  V to -2.5 V/0 V,  $AV_{DD\_(A-D)} + |AV_{SS}| \le 50$  V,  $AV_{DDL} = 4.5$  V to 5.5 V, AGND = 0 V, REFIN = 4.096 V external,  $IOV_{DD} = 2.7$  V to 5.5 V.  $V_{OUT}$ :  $R_{LOAD} = 1$  k $\Omega$ ,  $C_L = 200$  pF,  $I_{OUT}$ :  $R_{LOAD} = 250$   $\Omega$ ; all specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

| Parameter                       | Test Conditions                                                                                | Min   | Тур   | Max  | Unit       |

|---------------------------------|------------------------------------------------------------------------------------------------|-------|-------|------|------------|

| Voltage Output                  |                                                                                                |       |       |      |            |

|                                 |                                                                                                | 0     |       | 5    | V          |

|                                 |                                                                                                | 0     |       | 10   | V          |

|                                 | Ranges                                                                                         | -5    |       | 5    | V          |

| Outrot Valtaga Danga            |                                                                                                | -10   |       | 10   | V          |

| Output Voltage Ranges           |                                                                                                | 0     |       | 6    | V          |

|                                 | 0.42                                                                                           | 0     |       | 12   | V          |

|                                 | Overranges                                                                                     | -6    |       | 6    | V          |

|                                 |                                                                                                | -12   |       | 12   | V          |

| Resolution                      |                                                                                                | 16    |       |      | Bits       |

| Bipolar Supply                  | AV <sub>DD_(A-D)</sub> = 15 V, AV <sub>SS</sub> = -15 V, loaded and unloaded                   |       |       |      |            |

|                                 | T <sub>A</sub> = 25°C                                                                          | -0.05 | ±0.03 | 0.05 | %FSR       |

| Total Unadjusted Error (TUE)    | $T_A = -40^{\circ}C \text{ to } + 125^{\circ}C$                                                | -0.09 |       | 0.09 | %FSR       |

| Relative Accuracy (INL)         |                                                                                                | -0.01 |       | 0.01 | %FSR       |

| Differential Nonlinearity (DNL) |                                                                                                | -1    |       | 1.5  | LSB        |

| Zero-Scale Error                |                                                                                                | -0.05 | ±0.03 | 0.05 | %FSR       |

| Zero-Scale TC                   |                                                                                                |       | 0.83  |      | ppm FSR/°C |

| Full-Scale Error                |                                                                                                | -0.05 | ±0.03 | 0.05 | %FSR       |

| Full-Scale TC                   |                                                                                                |       | 0.82  |      | ppm FSR/°C |

| Offset Error                    |                                                                                                | -0.05 | ±0.03 | 0.05 | %FSR       |

| Offset TC                       |                                                                                                |       | 0.79  |      | ppm FSR/°C |

| Gain Error                      |                                                                                                | -0.06 | ±0.03 | 0.06 | %FSR       |

| Gain TC                         |                                                                                                |       | 0.92  |      | ppm FSR/°C |

| Unipolar Supply                 | AV <sub>DD_(A-D)</sub> = 15 V , AV <sub>SS</sub> = 0<br>V, On Unipolar Ranges,Code<br>from 256 |       |       |      |            |

| Total Unadjusted Error (TUE)    | T <sub>A</sub> = 25°C                                                                          | -0.05 | ±0.03 | 0.05 | %FSR       |

| Total Ollaujusteu Elloi (TOE)   | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                                           | -0.09 |       | 0.09 | %FSR       |

| Relative Accuracy (INL)         |                                                                                                | -0.01 |       | 0.01 | %FSR       |

| Differential Nonlinearity (DNL) |                                                                                                | -1.0  |       | 1.5  | LSB        |

www.3peak.com 10 / 80 BA20250401A0

| Parameter                           | Test Conditions                                                                                                                                  | Min    | Тур   | Max   | Unit       |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|-------|------------|

| Zero-Scale Error                    | Sink 1 mA from V <sub>OUTN_(A-D)</sub> ,<br>TA = 25°C                                                                                            | -0.22  | ±0.17 | 0.22  | %FSR       |

| Full-Scale Error                    |                                                                                                                                                  | -0.07  | ±0.03 | 0.07  | %FSR       |

| Offset Error                        |                                                                                                                                                  | -0.06  | ±0.03 | 0.06  | %FSR       |

| Gain Error                          |                                                                                                                                                  | -0.07  | ±0.04 | 0.07  | %FSR       |

| Output Characteristics              |                                                                                                                                                  |        | 1     |       |            |

| Headroom                            | Voutp                                                                                                                                            |        | 1.5   | 2     | V          |

| Footroom                            | V <sub>OUTN</sub>                                                                                                                                |        | 1.2   | 1.7   | V          |

| Short-Circuit Current               | Source and Sink                                                                                                                                  |        | ±20   |       | mA         |

| Load                                | T <sub>A</sub> = 25°C                                                                                                                            | 1.0    |       |       | kΩ         |

| V <sub>SENSEP_(A_D)</sub> Impedance | T <sub>A</sub> = 25°C                                                                                                                            |        | 1.0   |       | ΜΩ         |

|                                     | R <sub>LOAD</sub> = ∞                                                                                                                            |        |       | 10    | nF         |

|                                     | R <sub>LOAD</sub> = 1 kΩ                                                                                                                         |        |       | 100   | nF         |

| Capacitive Load Stability           | R <sub>LOAD</sub> = ∞<br>External compensation<br>capacitor of 47 pF<br>connected, and 30 ohm<br>resistor connected in series<br>with output pin |        |       | 2     | μF         |

| DC Output Impedance                 | T <sub>A</sub> = 25°C                                                                                                                            |        | 0.15  |       | Ω          |

| DC PSRR AV <sub>DD_(A-D)</sub>      | T <sub>A</sub> = 25°C                                                                                                                            |        | 1.4   |       | μV/V       |

| DC PSRR AV <sub>DDL</sub>           | T <sub>A</sub> = 25°C                                                                                                                            |        | 190   |       | μV/V       |

| DC PSRR AV <sub>SS</sub>            | T <sub>A</sub> = 25°C                                                                                                                            |        | 2.5   |       | μV/V       |

| DC Crosstalk                        | T <sub>A</sub> = 25°C                                                                                                                            |        | 10    |       | μV         |

| <b>Current Output</b>               |                                                                                                                                                  |        |       |       |            |

|                                     |                                                                                                                                                  | 0      |       | 24    | mA         |

| Output Current Ranges               |                                                                                                                                                  | 0      |       | 20    | mA         |

| Output Current Ranges               |                                                                                                                                                  | 4      |       | 20    | mA         |

|                                     | LOOP-POWER Input                                                                                                                                 | 24.6   | 25.0  |       | mA         |

| Resolution                          |                                                                                                                                                  | 16     |       |       | Bits       |

| <b>Current Accuracy</b>             | AV <sub>DD_(A-D)</sub> = 15 V, AVSS = 0                                                                                                          |        |       |       |            |

|                                     | T <sub>A</sub> = 25°C                                                                                                                            | -0.06  | ±0.04 | 0.06  | %FSR       |

| Total Unadjusted Error (TUE)        | $T_A = -40^{\circ}\text{C to} + 85^{\circ}\text{C}$                                                                                              | -0.1   |       | 0.1   | %FSR       |

|                                     | $T_A = -40^{\circ}\text{C to} + 125^{\circ}\text{C}$                                                                                             | -0.15  |       | 0.15  | %FSR       |

| Relative Accuracy (INL)             |                                                                                                                                                  | -0.015 |       | 0.015 | %FSR       |

| Differential Nonlinearity (DNL)     |                                                                                                                                                  | -1.0   |       | 1.5   | LSB        |

| Offset Error                        |                                                                                                                                                  | -0.055 | ±0.02 | 0.055 | %FSR       |

| Offset Error TC                     |                                                                                                                                                  |        | 1.28  |       | ppm FSR/°C |

www.3peak.com 11 / 80 BA20250401A0

| Parameter                             | Test Conditions                                                                                      | Min    | Тур   | Max   | Unit       |

|---------------------------------------|------------------------------------------------------------------------------------------------------|--------|-------|-------|------------|

| Gain Error                            |                                                                                                      | -0.15  | ±0.04 | 0.15  | %FSR       |

| Gain TC                               |                                                                                                      |        | 5.83  |       | ppm FSR/°C |

| Full-Scale Error                      |                                                                                                      | -0.15  | 0.04  | 0.15  | %FSR       |

| Full-Scale TC                         |                                                                                                      |        | 5.35  |       | ppm FSR/°C |

|                                       | T <sub>A</sub> = 25°C                                                                                | -0.18  |       | 0.18  | %FSR       |

| Zero-Scale Error                      | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                                                 | -0.2   |       | 0.2   | %FSR       |

| Current Output Characteristics        | AV <sub>DD_(A-D)</sub> = 15 V , AV <sub>SS</sub> = 0                                                 |        |       |       |            |

| Current Output Headroom               |                                                                                                      |        | 1.6   | 2.7   | V          |

| Resistive Load                        |                                                                                                      |        |       | 1000  | Ω          |

| I <sub>OUT_(A-D)</sub> Impedance      | I <sub>OUT_(A-D)</sub> to AGND, T <sub>A</sub> = 25°C                                                |        | 1     |       | МΩ         |

| Output Negative Voltage Detect Vth    | Fall Edge                                                                                            | -4     |       | -2.5  | V          |

| Output Negative Voltage<br>Detect Vth | Rise Edge                                                                                            | -3     |       | -2    | V          |

| DC PSRR AV <sub>DD</sub>              | T <sub>A</sub> = 25°C                                                                                |        | 0.05  |       | μΑ/V       |

| DC PSRR AV <sub>DDL</sub>             | T <sub>A</sub> = 25°C                                                                                |        | 0.3   |       | μA/V       |

| DC Crosstalk                          | T <sub>A</sub> = 25°C                                                                                |        | 0.063 |       | μA         |

| ADC                                   | Internal Reference                                                                                   |        |       |       |            |

|                                       | AV <sub>DD_(A-D)</sub> , I <sub>OUT_(A-D)</sub> Voltage<br>Range                                     | 0.0    |       | 37.5  | V          |

| Range                                 | V <sub>SENSEP_(A-D)</sub> Voltage Range                                                              | -12.5  |       | 12.5  | V          |

|                                       | Ground Current Voltage<br>Range                                                                      | -312.5 |       | 312.5 | mV         |

| Rin                                   | AV <sub>DD_(A-D)</sub> , I <sub>OUT_(A-D)</sub> Readback<br>Impedance to AGND, T <sub>A</sub> = 25°C |        | 2.0   |       | ΜΩ         |

|                                       | Ground Current Impedance,<br>T <sub>A</sub> = 25°C                                                   |        | 50.0  |       | kΩ         |

| Relative Accuracy (INL)               | T <sub>A</sub> = 25°C                                                                                |        | 0.2   |       | %FSR       |

| Total Unadjusted Error(TUE)           |                                                                                                      | -1     | ±0.5  | 1     | %FSR       |

| Data Rate                             | T <sub>A</sub> = 25°C                                                                                |        | 48    |       | KSPS       |

| Resolution                            |                                                                                                      |        | 12.0  |       | Bits       |

| Average Rate                          |                                                                                                      | 1.0    | 4.0   | 16.0  |            |

| Reference Input                       |                                                                                                      |        |       |       |            |

| Reference Input Voltage               |                                                                                                      |        | 4.096 |       | V          |

| DC Input Impedance                    |                                                                                                      |        | 40    |       | kΩ         |

| Reference Output                      |                                                                                                      |        |       |       |            |

| Output Voltage                        | T <sub>A</sub> = 25°C                                                                                | 4.094  | 4.096 | 4.098 | V          |

www.3peak.com 12 / 80 BA20250401A0

| Parameter                            | Test Conditions                                                 | Min                     | Тур  | Max  | Unit   |

|--------------------------------------|-----------------------------------------------------------------|-------------------------|------|------|--------|

| Reference TC                         |                                                                 | -10.0                   | ±5   | 10.0 | ppm/°C |

| Output Noise (0.1 Hz to 10 Hz)       | T <sub>A</sub> = 25°C                                           |                         | 7.6  |      | μVp-p  |

| Noise Spectral Density               | At 10 kHz                                                       |                         | 390  |      | nV/√Hz |

| Output Voltage Drift vs. Time        | Drift after 1000 hours, T <sub>A</sub> = 125°C                  |                         | 165  |      | ppm    |

| Capacitive Load                      | T <sub>A</sub> = 25°C                                           |                         | 100  |      | nF     |

| Load Current                         | T <sub>A</sub> = 25°C                                           |                         | 10   |      | mA     |

| Short-Circuit Current                | T <sub>A</sub> = 25°C                                           |                         | 20   |      | mA     |

| Line Regulation                      | T <sub>A</sub> = 25°C                                           |                         | 20   |      | ppm/V  |

| Load Regulation                      | T <sub>A</sub> = 25°C                                           |                         | 62   |      | ppm/mA |

| Digital Inputs                       |                                                                 |                         |      |      |        |

| Input High Voltage, V <sub>IH</sub>  | Rate of IOV <sub>DD</sub>                                       | 0.7                     |      |      |        |

| Input Low Voltage, V <sub>I</sub> ∟  | Rate of IOV <sub>DD</sub>                                       |                         |      | 0.3  |        |

| Input Current                        |                                                                 | -1                      |      | 1    | μA     |

| Hysteresis                           | IOV <sub>DD</sub> > 2.7 V                                       | 0.08                    |      |      | V      |

| Pin Capacitance                      |                                                                 |                         | 5.0  |      | pF     |

| Digital Outputs                      |                                                                 |                         |      |      |        |

| SDO                                  |                                                                 |                         |      |      |        |

| Output Low Voltage, V <sub>OL</sub>  | Sinking 200 μA                                                  |                         |      | 0.4  | V      |

| Output High Voltage, V <sub>OH</sub> | Sourcing 200 μA                                                 | IOV <sub>DD</sub> - 0.5 |      |      | V      |

| High Impedance Leakage<br>Current    |                                                                 | -1                      |      | 1    | μΑ     |

| High Impedance Output Capacitance    |                                                                 |                         | 5    |      | pF     |

| FAULTN                               |                                                                 |                         |      |      |        |

| Output Low Voltage, V <sub>OL</sub>  | 10 kΩ Pull-up Resistor to IOV <sub>DD</sub>                     |                         |      | 0.4  | V      |

| Output High Voltage, V <sub>OH</sub> | 10 kΩ Pull-up Resistor to IOV <sub>DD</sub>                     | IOV <sub>DD</sub> - 0.1 |      |      | V      |

| Power Requirements                   |                                                                 |                         |      |      | 1      |

| Power Range                          |                                                                 |                         |      |      |        |

| AV <sub>DD_(A-D)</sub>               | $\left  (AV_{DD_{-}(A-D)} +  AV_{SS}  \le 50 \text{ V} \right)$ | 7                       | 15   | 50   | V      |

| AVss                                 |                                                                 | -27                     | -15  | 0    | V      |

| IOV <sub>DD</sub>                    |                                                                 | 2.7                     | 5    | 5.5  | V      |

| AVDDL                                |                                                                 | 4.5                     | 5    | 5.5  | V      |

| Power UVLO                           |                                                                 |                         |      |      |        |

| AV <sub>DD_(A-D)</sub>               | Rise Threshold, T <sub>A</sub> = 25°C                           |                         | 6.05 |      | V      |

| AV <sub>DD_(A-D)</sub>               | Fall Threshold, T <sub>A</sub> = 25°C                           |                         | 5.35 |      | V      |

www.3peak.com 13 / 80 BA20250401A0

| Parameter                   | Test Conditions                                                         | Min                       | Тур   | Max   | Unit |

|-----------------------------|-------------------------------------------------------------------------|---------------------------|-------|-------|------|

| AV <sub>DDL</sub>           | Rise Threshold, T <sub>A</sub> = 25°C                                   |                           | 3.60  |       | V    |

| AV <sub>DDL</sub>           | Fall Threshold, T <sub>A</sub> = 25°C                                   |                           | 3.20  |       | V    |

| IOV <sub>DD</sub>           | Threshold, T <sub>A</sub> = 25°C                                        |                           | 1.78  |       | V    |

| <b>Current Requirements</b> |                                                                         |                           |       |       |      |

|                             | All Voltage Output Enable, non-loaded                                   |                           | 4.17  | 6.56  | mA   |

| $AV_{DD\_(A-D)}$            | All Current Output Enable                                               | All Current Output Enable |       | 3.94  | mA   |

|                             | All Output Disable                                                      | Output Disable            |       | 2.16  | mA   |

|                             | All Voltage Output Enable, non-loaded                                   | -4.64                     | 3.15  |       | mA   |

| AVss                        | All Current Output Enable                                               | -1.67                     | 0.99  |       | mA   |

|                             | All Output Disable                                                      | -1.67                     | 0.99  |       | mA   |

| AVDDL                       | All Channels Output Enable,<br>CODE=65535, No Load, &<br>ADC is Enabled |                           | 6.01  | 8.93  | mA   |

|                             | All Channels Output Disable & ADC is Disabled                           |                           | 1.84  | 3.47  | mA   |

| IOV <sub>DD</sub>           | All Channels Output Enable,<br>CODE=65535, No SPI Flip                  |                           | 0.005 | 0.017 | mA   |

www.3peak.com 14 / 80 BA20250401A0

All test conditions:  $AV_{DD\_(A-D)} = 15 \text{ V}$ ,  $AV_{SS} = -15 \text{ V}$ ,  $AV_{DDL} = 5 \text{ V}$ , AGND = 0 V, REFIN = 4.096 V external,  $IOV_{DD} = 2.7 \text{ V}$  to 5.5 V.  $V_{OUT}$ :  $R_{LOAD} = 2 \text{ k}\Omega$ ,  $C_L = 200 \text{ pF}$ ,  $I_{OUT}$ :  $R_{LOAD} = 250 \Omega$ ; all specifications  $T_A = 25^{\circ}C$ , unless otherwise noted.

**Table 2. AC Performance Characteristics**

| Parameter                                | Test Conditions                                                                      | Min | Тур  | Max    | Unit    |

|------------------------------------------|--------------------------------------------------------------------------------------|-----|------|--------|---------|

| Dynamic Performance                      |                                                                                      |     |      |        |         |

| Voltage Output                           |                                                                                      |     |      |        |         |

|                                          | 5 V Range, step to ±0.1 % FSR                                                        |     | 20   |        | μs      |

| Output Voltage Settling Time             | 10 V Range, step to ±0.1 % FSR                                                       |     | 27   |        | μs      |

| Time                                     | 20 V Range, step to ±0.1 % FSR                                                       |     | 65   |        | μs      |

| Output Noise (0.1 Hz to 10 Hz Bandwidth) | Midscale Output,0 V to 10 V Range                                                    |     | 0.1  |        | LSBp-p  |

| Output Noise Spectral Density            | Measured at 10 kHz, Midscale Output, 0 V to 10 V Range                               | 390 |      | nV/√Hz |         |

| Slew Rate                                | 10 V Range                                                                           |     | 0.87 |        | V/µs    |

| Power-On Glitch                          | Output unload                                                                        |     | 1    |        | mV      |

| Enable Glitch                            | 10 V Range, Code = 0x0000                                                            |     | 160  |        | mV      |

| Disable Glitch                           | 10 V Range, Code = 0x0000                                                            |     | 200  |        | mV      |

| Digital-to-Analog Glitch<br>Energy       | 10 V Range, Zero Output                                                              |     | 16   |        | nV-sec  |

| Digital Feedthrough                      | 10 V Range, Zero Output                                                              | 1.0 |      | nV-sec |         |

| AC PSRR AV <sub>DD</sub>                 | R AV <sub>DD</sub> 200 mV 50 Hz/60 Hz Sine-wave Superimposed on Power Supply Voltage |     | -74  |        | dB      |

| AC PSRR AV <sub>DDL</sub>                | 200 mV 50 Hz/60 Hz Sine-wave Superimposed on Power Supply Voltage                    |     | -78  |        | dB      |

| AC PSRR AV <sub>SS</sub>                 | 200 mV 50 Hz/60 Hz Sine-wave Superimposed on Power Supply Voltage                    |     | -76  |        | dB      |

| <b>Current Output</b>                    |                                                                                      |     |      |        |         |

| Output Current Settling Time             | step to ±0.1 % FSR (0 mA to 24 mA)                                                   |     | 48   |        | μs      |

| Output Noise (0.1 Hz to 10 Hz Bandwidth) | Midscale output, 0 mA to 24 mA range                                                 |     | 0.32 |        | LSB p-p |

| Output Noise Spectral Density            | Measured at 10 kHz, Midscale output, 0 mA to 24 mA range                             |     | 0.8  |        | nA/√Hz  |

| Power-On Glitch                          | R <sub>LOAD</sub> = 250 Ω                                                            |     | 3.2  |        | μA      |

| Enable Glitch                            | Code = 0x0000, 0 mA to 24 mA range                                                   |     | 1    |        | μA      |

| Disable Glitch                           | Code = 0x0000, 0 mA to 24 mA range                                                   |     | 60   |        | μA      |

| AC PSRR AVDD                             | 250 O Load, 200 mV 50 Hz/60 Hz Sine-wave                                             |     |      |        | dB      |

| AC PSRR AVDDL                            | 250 Ω Load, 200 mV 50 Hz/60 Hz Sine-wave<br>Superimposed on Power Supply Voltage     |     | -78  |        | dB      |

www.3peak.com 15 / 80 BA20250401A0

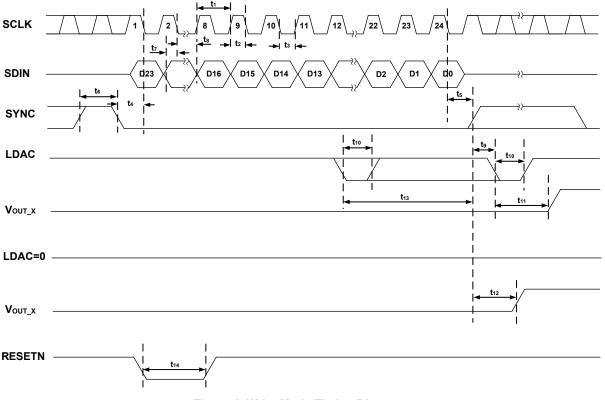

### **Timing Requirements**

$AV_{DD\_(A-D)}$  = 15 V,  $AV_{SS}$  = -15 V,  $AV_{DDL}$  = 5 V, AGND = 0 V, REFIN = 4.096 V external,  $IOV_{DD}$  = 2.7 V to 5.5 V.  $V_{OUT}$ :  $R_{LOAD}$  = 1  $k\Omega$ ,  $C_L$  = 200 pF,  $I_{OUT}$ :  $R_{LOAD}$  = 250  $\Omega$ , all specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

**Table 3. Timing Characteristics**

| Parameter (1) (2) | Description                                                                                            | Min   | Тур | Max | Unit |

|-------------------|--------------------------------------------------------------------------------------------------------|-------|-----|-----|------|

| t <sub>1</sub>    | SCLK cycle time                                                                                        | 50.0  |     |     | ns   |

| t <sub>2</sub>    | SCLK high time                                                                                         | 17.0  |     |     | ns   |

| t <sub>3</sub>    | SCLK low time                                                                                          | 17.0  |     |     | ns   |

| t <sub>4</sub>    | SYNC falling edge to SCLK falling edge setup time                                                      | 20.0  |     |     | ns   |

| t <sub>5</sub>    | Final SCLK falling edge to SYNC rising edge                                                            | 15.0  |     |     | ns   |

|                   | SYNC high time following a configuration write                                                         | 2.0   |     |     | μs   |

| $t_6$             | SYNC high time following a DAC update write                                                            | 5.0   |     |     | μs   |

| 16                | SYNC high time following a DAC update write (slew rate control enabled)                                | 20.0  |     |     | μs   |

| t <sub>7</sub>    | Data setup time                                                                                        | 15.0  |     |     | ns   |

| t <sub>8</sub>    | Data hold time                                                                                         | 10.0  |     |     | ns   |

|                   | SYNC rising edge to LDAC falling edge (applies to any channel with digital slew rate control enabled)  | 20.0  |     |     | μs   |

| t <sub>9</sub>    | SYNC rising edge to LDAC falling edge (applies to any channel with digital slew rate control disabled) | 5.0   |     |     | μs   |

| t <sub>10</sub>   | LDAC pulse width low                                                                                   | 10.0  |     |     | ns   |

| t <sub>11</sub>   | LDAC falling edge to DAC output response time                                                          |       |     | 2.0 | μs   |

| t <sub>12</sub>   | SYNC rising edge to DAC output response time with LDAC is 0                                            | 5.0   |     |     | μs   |

| t <sub>13</sub>   | LDAC falling edge to SYNC rising edge                                                                  | 500.0 |     |     | ns   |

| t <sub>14</sub>   | RESET pulse width                                                                                      | 50.0  |     |     | μs   |

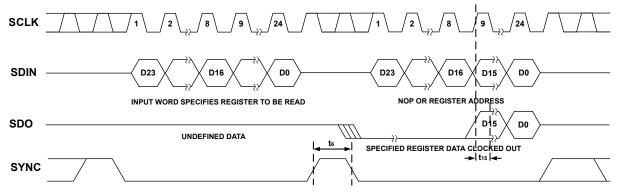

| t <sub>15</sub>   | SCLK rising edge to SDO valid                                                                          |       |     | 45  | ns   |

<sup>(1)</sup> Guaranteed by characterization; not production tested.

www.3peak.com 16 / 80 BA20250401A0

<sup>(2)</sup> CL SDO = 20 pF.

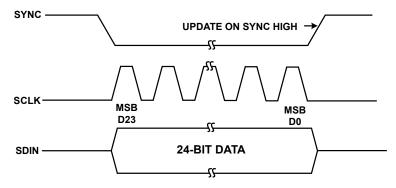

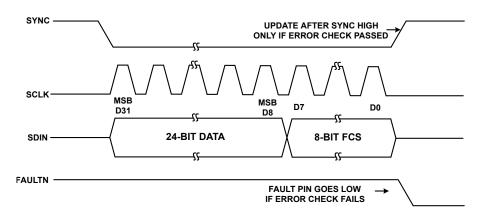

### **Timing Diagrams**

Figure 1. Write Mode Timing Diagram

Figure 2. Readback Mode Timing Diagram

www.3peak.com 17 / 80 BA20250401A0

Figure 3. Status Readback during Write

www.3peak.com 18 / 80 BA20250401A0

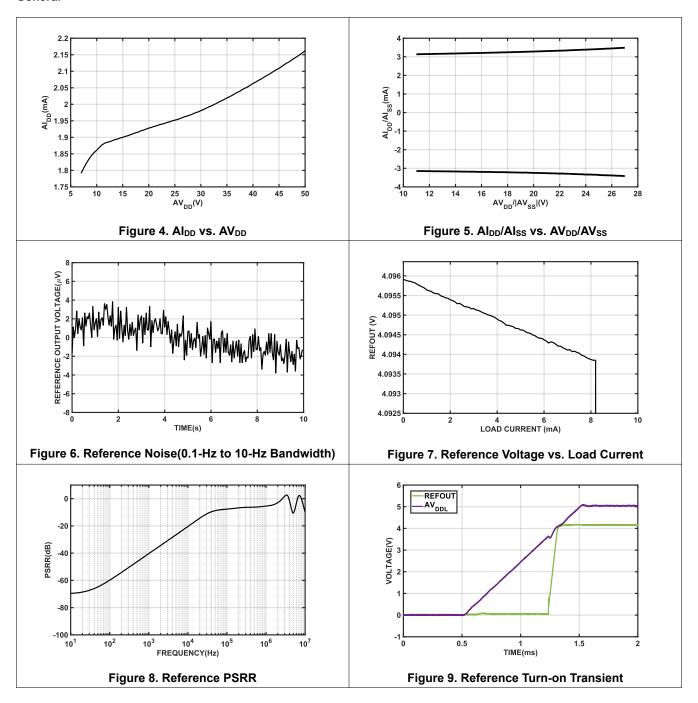

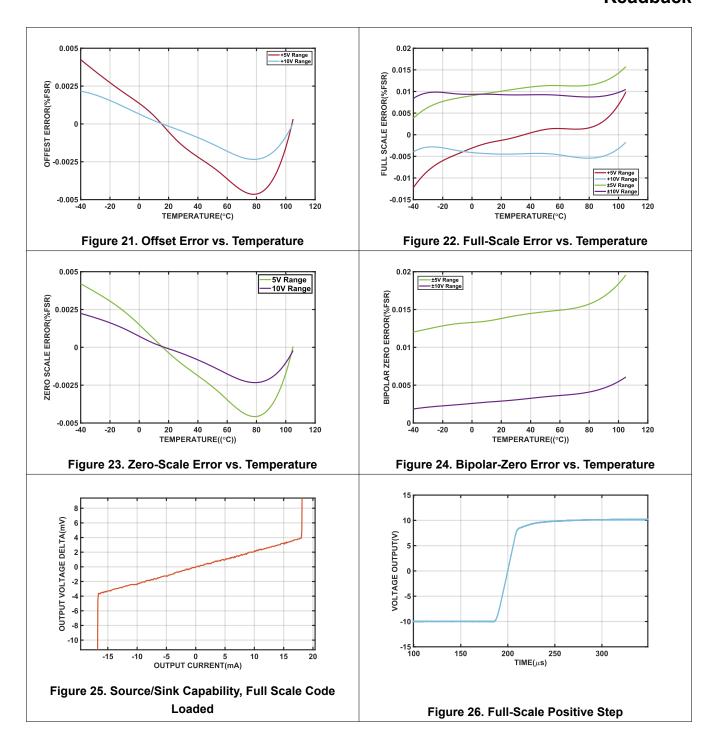

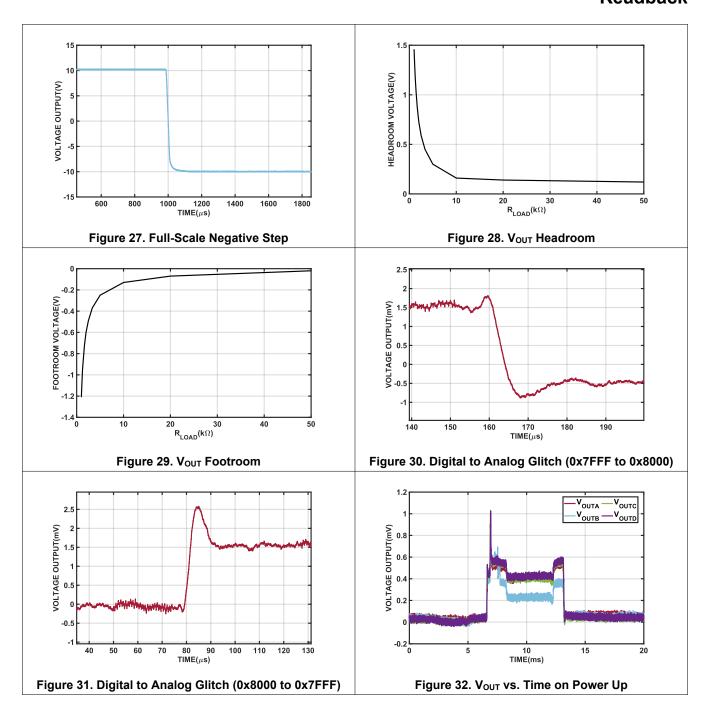

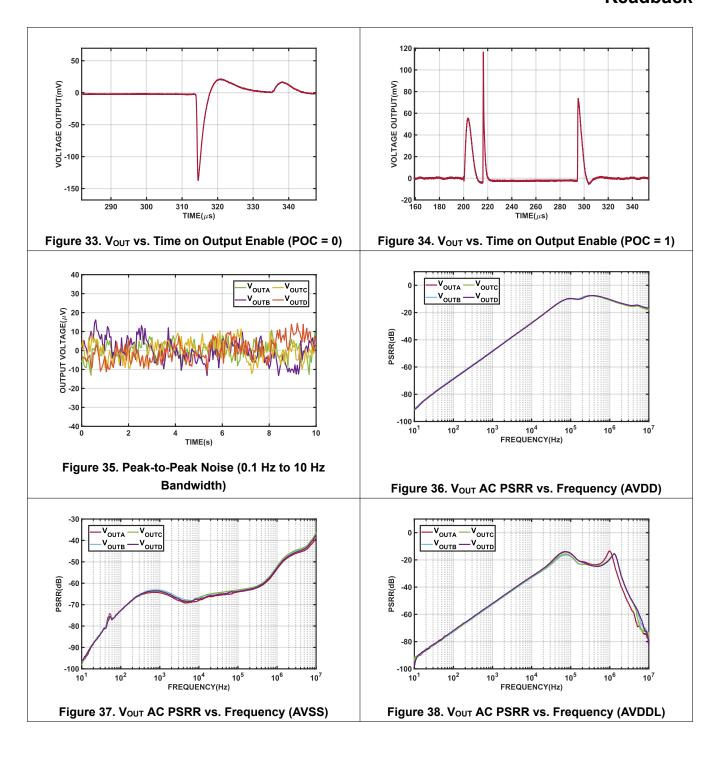

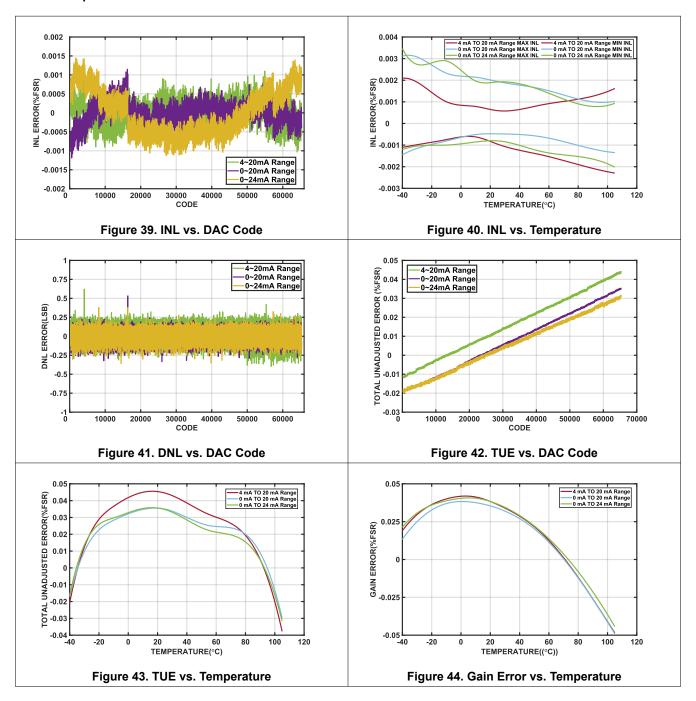

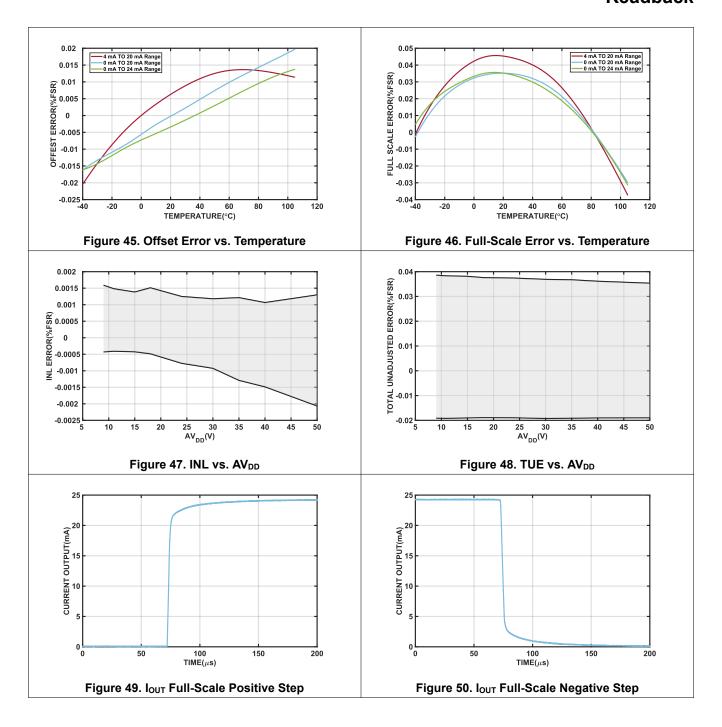

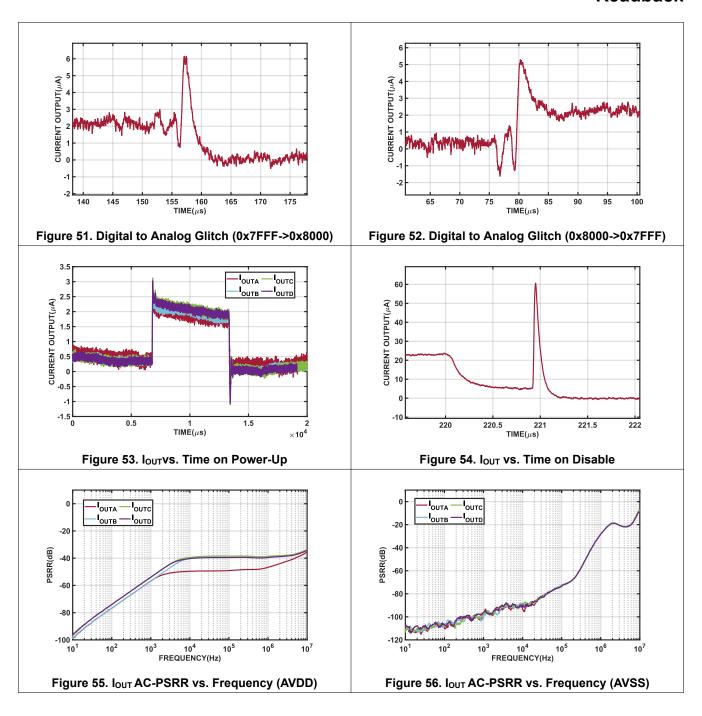

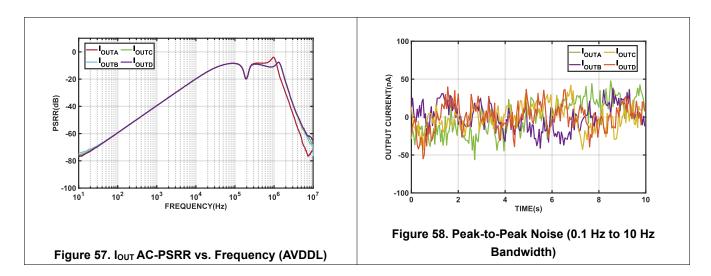

### **Typical Performance Characteristics**

#### General

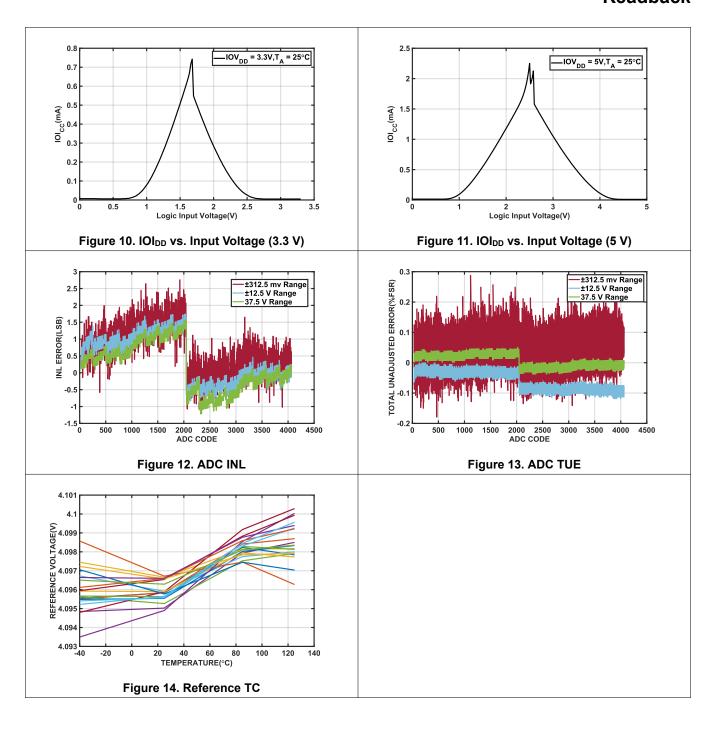

### **Voltage Output**

www.3peak.com 21 / 80 BA20250401A0

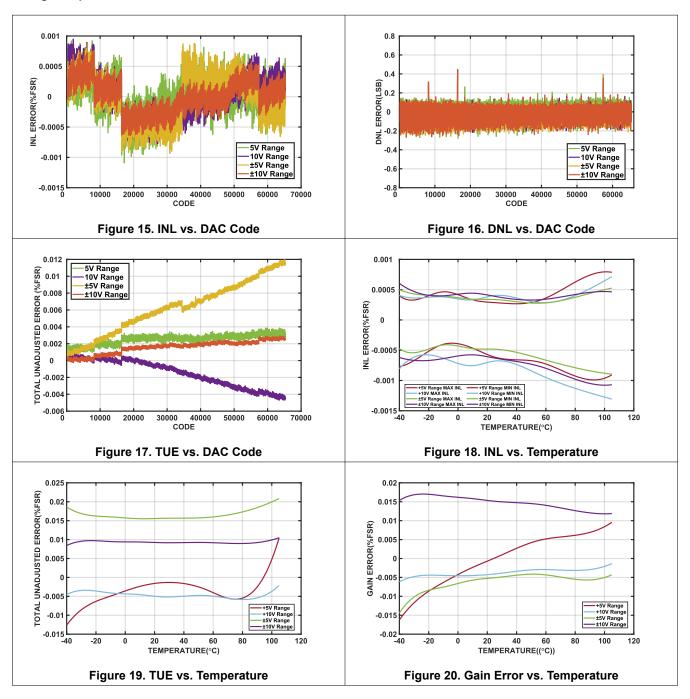

#### **Current Output**

www.3peak.com 27 / 80 BA20250401A0

www.3peak.com 28 / 80 BA20250401A0

### **Detailed Description**

#### Overview

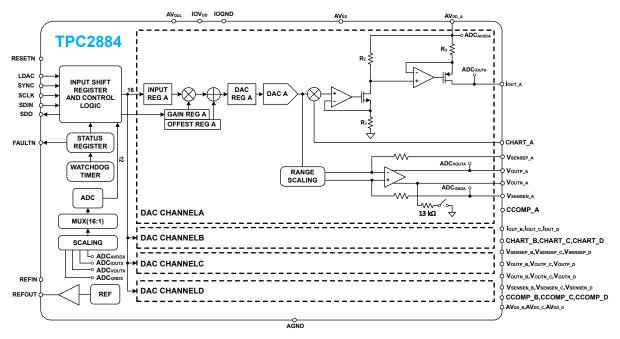

The TPC2884 is a series of high-precision, quad-channel digital-to-analog converters that offer a fully integrated, single-chip solution for industrial process control applications. These converters are capable of generating both current loop and unipolar/bipolar voltage outputs with exceptional precision. The available current ranges for these converters are 0 mA to 20 mA, 0 mA to 24 mA, and 4 mA to 20 mA. For voltage output, the options include 0 V to 5 V, ±5 V, 0 V to 10 V, and ±10 V, each with the capability of a 20% overrange. Both the current and voltage outputs are accessible via separate pins, it can be used with external diodes to achieve port withstand voltage beyond the power rail, and the withstand voltage can reach ±50 V (± 15 V power supply). The user can select the desired output configuration through the control register, ensuring that only one type of output is active at any given time. TPC2884 has complete on-chip diagnostics and an integrated 12-bit ADC for reading back voltages from four channels, including AV<sub>DD</sub>, V<sub>SENSEP</sub>, V<sub>SENSEP</sub>, I<sub>OUT</sub> pins.

#### **Functional Block Diagram**

Figure 59. Functional Block Diagram

#### **Feature Description**

The TPC2884 is a quad-channel voltage and current output digital-to-analog converter (DAC) that operates with a power supply range from -27 V to +50 V. The AV<sub>DD</sub> pin for each channel provides independent positive power supply with a range of 7 V to 50 V, which can be used with an external adaptive power supply to reduce chip heating, and External resistance can also be connected in series with the AV<sub>DD</sub> to achieve a switchable HART impedance in LOOP\_POWER current input mode. In the current output mode, each channel has an independent HART injection PIN to transmit HART.

www.3peak.com 29 / 80 BA20250401A0

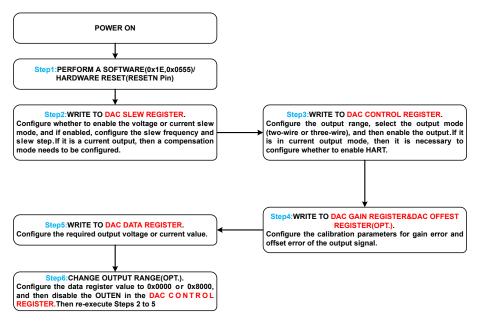

#### **Analog Power Supply**

After powering up, it is required that a hardware reset be issued using the RESETN pin. The reset event is recorded in the MAIN\_STATUS\_REG RESET\_NOTE\_STATUS, and clearing the reset record requires the 0x0358 to be written to the SOFTWARE\_REG.

The TPC2884 has a total of six analog power supply ports, namely  $AV_{DD\_A}$ ,  $AV_{DD\_B}$ ,  $AV_{DD\_D}$ ,  $AV_{SS}$ , and  $AV_{DDL}$ . Among them, the power supply range for  $AV_{DD\_A}$  to  $AV_{DD\_B}$  is 7 V to 50 V. The voltage range for  $AV_{SS}$  is -27 V to 0 V, and the voltage range for  $AV_{DDL}$  is 4.5 V to 5.5 V. Note that the sum of the absolute values of  $AV_{DD}$  and  $AV_{SS}$  must be less than 50 V. Recommended Operating Conditions shows the maximum and minimum allowable limits for all the power supplies when TPC2884 is powered using external power supplies.

#### **Digital Power Supply**

The TPC2884 has only one digital power supply port, which is IOV<sub>DD</sub>, with a voltage range of 2.7 V to 5.5 V.

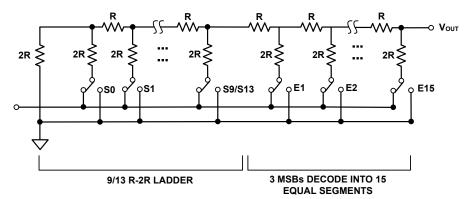

#### **DAC Ladder Structure**

The DAC core architecture of the TPC2884 is an R-2R DAC ladder shown below:

Figure 60. TPC2884 DAC Ladder Structure

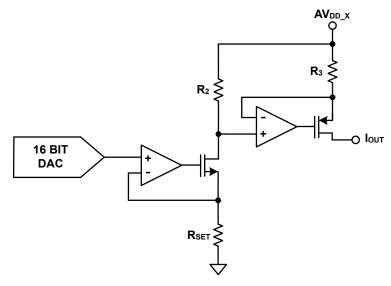

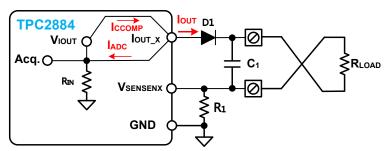

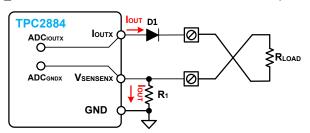

#### **Current Output Stage**

Each channel's current output stage consists of a pre-conditioner and a precision current source as shown in Figure 61. This stage provides a current output according to the DAC code. The output range can be programmed as 0 mA to 20 mA, 0 mA to 24 mA or 4 mA to 20 mA.

www.3peak.com 30 / 80 BA20250401A0

Figure 61. Voltage to Current Conversion Circuit

The 16 bit data can be written to TPC2884 using address 0x00,0x01,0x02,0x03.

For a 0-mA to 20-mA output range:

$$I_{OUT\_X} = 20 \text{ mA} \times \frac{\text{Code}}{2^N}$$

(1)

For a 0-mA to 24-mA output range:

$$I_{OUT\_X} = 24 \text{ mA} \times \frac{\text{Code}}{2^N}$$

(2)

For a 4-mA to 20-mA output range:

$$I_{OUT\_X} = 4 \text{ mA} + 16 \text{ mA} \times \frac{\text{Code}}{2^N}$$

(3)

#### Where:

- Code is the decimal equivalent of the code loaded to the DAC;

- N is the bits of resolution; 16.

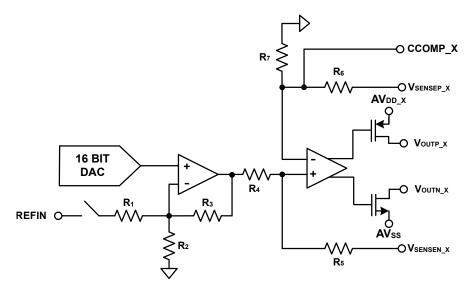

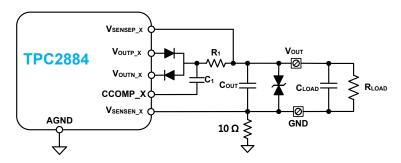

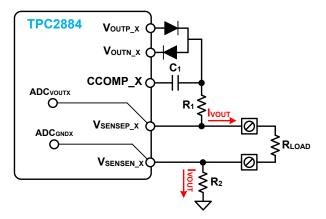

### **Voltage Output Stage**

The voltage output stage as conceptualized in Figure provides the voltage output according to the DAC code and the output range setting. The output range can be programmed as 0 V to +5 V or 0 V to +10 V for unipolar output mode, and ±5 V or ±10 V for bipolar output mode. In addition, an option is available to increase the output voltage range by 20%. The output current drive can be up to 10 mA. The output stage has short-circuit current protection that limits the output current to 20 mA.

The voltage output is designed to drive capacitive loads of up to 2  $\mu$ F. For loads greater than 10 nF, an external compensation capacitor can be connected between CCOMP\_X and  $V_{OUT_X}$  to keep the output voltage stable at the expense of reduced bandwidth and increased settling time. Note that, a step response (due to input code change) on the voltage output pin loaded with large capacitive load (> 20 nF) will trigger the short circuit limit circuit of the output stage. This will result in setting the short circuit alarm status bits. Therefore, it is recommended to use slew rate control for large step change, when the voltage output pin is loaded with high capacitive loads.

www.3peak.com 31 / 80 BA20250401A0

Figure 62. Voltage Output Circuit

The  $V_{\text{SENSEP}\_X}$  pin is provided to enable sensing of the load. Ideally, it is connected to  $V_{\text{OUT}\_X}$  at the terminals. Additionally, it can also be used to connect remotely to points electrically "nearer" to the load. This allows the internal output amplifier to ensure that the correct voltage is applied across the load as long as headroom is available on the power supply. However, if this line is cut, the amplifier loop would be broken. Therefore, an optional resistor can be used between  $V_{\text{OUT}\_X}$  and  $V_{\text{SENSEP}\_X}$  to prevent this.

The V<sub>SENSEN\_X</sub> pin can be used to sense the remote ground and offset the V<sub>OUT\_X</sub> pin accordingly.

The 16-bit data can be written to TPC2884 as shown in DAC data registers.

For unipolar output mode:

$$V_{OUT\_X} = VREFIN \times GAIN \times \frac{Code}{2^N}$$

(4)

For bipolar output mode:

$$V_{OUT\_X} = VREFIN \times GAIN \times \left(\frac{Code}{2^N} - 0.5\right)$$

(5)

#### Where:

- CODE is the decimal equivalent of the code loaded to the DAC.

- N is the bits of resolution: 16.

- VREFIN is the reference voltage; for internal reference, VREFIN = +4.096 V.

- GAIN is automatically selected for a desired voltage output range.

#### **Voltage Output Short Current Protection**

The voltage output buffer sources or sinks 10-mA current in normal mode. The maximum current of the buffer can output is 20 mA even if the buffer short-circuited to power or ground.

#### **Voltage Output Over-range**

The voltage output features an over-range capability. This functionality can be activated through the control register, which typically extends the chosen output range by approximately 20%.

www.3peak.com 32 / 80 BA20250401A0

#### **Voltage Output using Force and Sense**

The  $V_{SENSEP}$  and  $V_{SENSEN}$  terminals are designed to enable the remote monitoring of the load connected to the voltage output. By sensing the voltage at the load's end, especially if it's connected via a lengthy or high-impedance cable, the output amplifier can adjust accordingly. This adjustment ensures that the precise voltage is maintained across the load. The effectiveness of this feature is contingent upon the power supply's available headroom.

#### **DRIVING LARGE CAPACITIVE LOADS**

The voltage output amplifier is designed to handle substantial capacitive loads, with a capacity of up to 2  $\mu$ F, by incorporating a nonpolarized 47 pF compensation capacitor between the CCOMP and Vout terminals. In the absence of this compensation capacitor, the amplifier can still manage capacitive loads of up to 10 nF.

#### **Register Maps**

Table 4. TPC2884 Address Functions

| ADDRESS BYTE | FUNCTION                    | READ/WRITE | POWER-ON RESET<br>VALUE | Section  |

|--------------|-----------------------------|------------|-------------------------|----------|

| 0x00         | DAC_A_REG                   | READ+WRITE | 0x0000                  |          |

| 0x01         | DAC_B_REG                   | READ+WRITE | 0x0000                  | Table 5  |

| 0x02         | DAC_C_REG                   | READ+WRITE | 0x0000                  | Table 5  |

| 0x03         | DAC_D_REG READ+WRITE 0x0000 |            | 0x0000                  |          |

| 0x04         | GAIN_A_REG                  | READ+WRITE | 0x0000                  |          |

| 0x05         | GAIN_B_REG                  | READ+WRITE | 0x0000                  | Table 7  |

| 0x06         | GAIN_C_REG                  | READ+WRITE | 0x0000                  | Table 7  |

| 0x07         | GAIN_D_REG                  | READ+WRITE | 0x0000                  |          |

| 0x08         | OFFEST_A_REG                | READ+WRITE | 0x0000                  |          |

| 0x09         | OFFEST_B_REG                | READ+WRITE | 0x0000                  | Table 9  |

| 0x0A         | OFFEST_C_REG                | READ+WRITE | 0x0000                  | Table 9  |

| 0x0B         | OFFEST_D_REG                | READ+WRITE | 0x0000                  |          |

| 0x0C         | CLEAR_A_REG                 | READ+WRITE | 0x0000                  |          |

| 0x0D         | CLEAR_B_REG                 | READ+WRITE | 0x0000                  | Table 11 |

| 0x0E         | CLEAR_C_REG                 | READ+WRITE | 0x0000                  | Table 11 |

| 0x0F         | CLEAR_D_REG                 | READ+WRITE | 0x0000                  |          |

| 0x10         | SLEW_A_REG                  | READ+WRITE | 0x0000                  |          |

| 0x11         | SLEW_B_REG                  | READ+WRITE | 0x0000                  | Table 13 |

| 0x12         | SLEW_C_REG                  | READ+WRITE | 0x0000                  | Table 13 |

| 0x13         | SLEW_D_REG                  | READ+WRITE | 0x0000                  |          |

| 0x14         | DAC_CTRL_A_REG              | READ+WRITE | 0x0000                  |          |

| 0x15         | 0x15 DAC_CTRL_B_REG         |            | 0x0000                  | Table 15 |

| 0x16         | DAC_CTRL_C_REG              | READ+WRITE | 0x0000                  | Table 15 |

| 0x17         | DAC_CTRL_D_REG              | READ+WRITE | 0x0000                  |          |

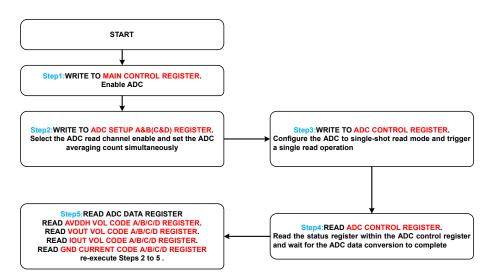

| 0x18         | ADC_SETUP_A&B_REG           | READ+WRITE | 0x0000                  | Table 17 |

www.3peak.com 33 / 80 BA20250401A0

| ADDRESS BYTE | FUNCTION                   | READ/WRITE | POWER-ON RESET<br>VALUE | Section  |

|--------------|----------------------------|------------|-------------------------|----------|

| 0x19         | ADC_SETUP_C&D_REG          | READ+WRITE | 0x0000                  | Table 19 |

| 0x1A         | NOP_REG                    | WRITE      | 0x0000                  | Table 21 |

| 0x1B         | Reserved                   | NA         | 0x0000                  |          |

| 0x1C         | ADC_CTRL_REG               | READ+WRITE | 0x0000                  | Table 23 |

| 0X1D         | MAIN_CTRL_REG              | READ+WRITE | 0x0000                  | Table 25 |

| 0x1E         | SOFTWARE_REG               | WRITE      | 0x0000                  | Table 27 |

| 0x1F         | FAULT_MASK_REG             | READ+WRITE | 0x0000                  | Table 29 |

| 0x20         | FAULT_CLEAR_REG            | WRITE      | 0x0000                  | Table 31 |

| 0x21         | FAULT_STORE_REG            | READ       | 0x0000                  | Table 33 |

| 0x22         | MAIN_STATUS_REG            | READ       | 0x0000                  | Table 35 |

| 0x23         | OUT_STATUS_REG             | READ       | 0x0000                  | Table 37 |

| 0x24         | AVDDH_VOL_CODE_A_RE<br>G   | READ       | 0x0000                  |          |

| 0x25         | AVDDH_VOL_CODE_B_RE<br>G   | READ       | 0x0000                  | Table 00 |

| 0x26         | AVDDH_VOL_CODE_C_RE<br>G   | READ       | 0x0000                  | Table 39 |

| 0x27         | AVDDH_VOL_CODE_D_RE<br>G   | READ       | 0x0000                  |          |

| 0x28         | VOUT_VOL_CODE_A_RE<br>G    | READ       | 0x0000                  |          |

| 0x29         | VOUT_VOL_CODE_B_RE<br>G    | READ       | 0x0000                  | T. 1. 44 |

| 0x2A         | VOUT_VOL_CODE_C_RE<br>G    | READ       | 0x0000                  | Table 41 |

| 0x2B         | VOUT_VOL_CODE_D_RE<br>G    | READ       | 0x0000                  |          |

| 0x2C         | IOUT_VOL_CODE_A_REG        | READ       | 0x0000                  |          |

| 0x2D         | IOUT_VOL_CODE_B_REG        | READ       | 0x0000                  | Table 40 |

| 0x2E         | IOUT_VOL_CODE_C_REG        | READ       | 0x0000                  | Table 43 |

| 0x2F         | IOUT_VOL_CODE_D_REG        | READ       | 0x0000                  |          |

| 0x30         | GND_CURRENT_CODE_A<br>_REG | READ       | 0x0000                  |          |

| 0x31         | GND_CURRENT_CODE_B<br>_REG | READ       | 0x0000                  | <b>-</b> |

| 0x32         | GND_CURRENT_CODE_C<br>_REG | READ       | 0x0000                  | Table 45 |

| 0x33         | GND_CURRENT_CODE_D<br>_REG | READ       | 0x0000                  |          |

www.3peak.com 34 / 80 BA20250401A0

| ADDRESS BYTE | FUNCTION          | READ/WRITE          | POWER-ON RESET<br>VALUE | Section                                                |

|--------------|-------------------|---------------------|-------------------------|--------------------------------------------------------|

| 0x34         | ID_REG            | READ                | 0x0B44                  | Table 47                                               |

| 0x35         | DAC_ALL_REG       | WRITE               | 0x0000                  | DAC_ALL_REG(addre<br>ss = 0x35) [reset =<br>0x0000]    |

| 0x36         | GAIN_ALL_REG      | WRITE               | 0x0000                  | GAIN_ALL_REG(addr<br>ess = 0x36) [reset =<br>0x0000]   |

| 0x37         | OFFSET_ALL_REG    | WRITE               | 0x0000                  | OFFEST_ALL_REG(a<br>ddress = 0x37) [reset =<br>0x0000] |

| 0x38         | CLEAR_ALL_REG     | CLEAR_ALL_REG WRITE |                         | CLEAR_ALL_REG(ad<br>dress = 0x38) [reset =<br>0x00000] |

| 0x39         | SLEW_ALL_REG      | WRITE               | 0x0000                  | SLEW_ALL_REG(addr<br>ess = 0x39) [reset =<br>0x0000]   |

| 0x3A         | DAC_CTRL_ALL_REG  | WRITE               | 0x0000                  | DAC_CTRL_ALL_RE G(address = 0x3A) [reset = 0x0000]     |

| 0x3B         | ADC_SETUP_ALL_REG | WRITE               | 0x0000                  | Table 49                                               |

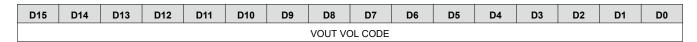

### $DAC\_A\_REG\sim DAC\_D\_REG(address = 0x00\sim 0x03)$ [reset = 0x0000]

### Table 5. DAC\_X\_REG Bit Map

| D15 | D14             | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|-----|-----------------|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

|     | 16-bit dac code |     |     |     |     |    |    |    |    |    |    |    |    |    |    |

### Table 6. DAC\_X\_REG Bit Descriptions

| Bit  | Field    | Туре | Reset  | Description                                                                                                 |

|------|----------|------|--------|-------------------------------------------------------------------------------------------------------------|

| 15:0 | DAC_CODE | R/W  | 0x0000 | DAC data , The data is in original code format, with a range of 0 to 65535 and a default value of 16'h0000. |

#### $GAIN\_A\_REG\sim GAIN\_D\_REG(address = 0x04\sim 0x07)$ [reset = 0x0000]

### Table 7. GAIN\_X\_REG Bit Map

| D15 | D14              | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|-----|------------------|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

|     | 16-bit gain code |     |     |     |     |    |    |    |    |    |    |    |    |    |    |

www.3peak.com 35 / 80 BA20250401A0

#### Table 8. GAIN\_X\_REG Bit Descriptions