### **Features**

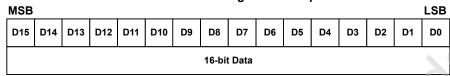

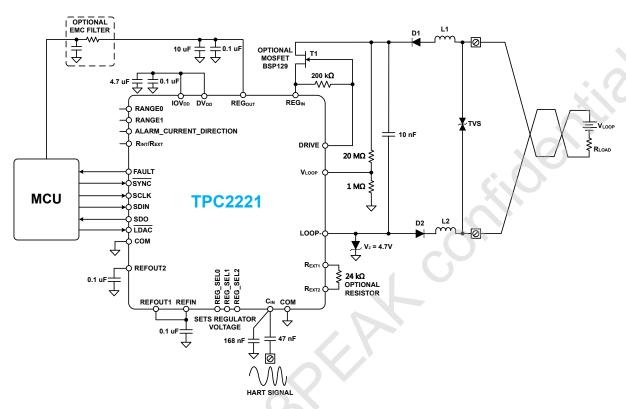

- 16-bit resolution and monotonicity

- Pin selectable NAMUR-compliant ranges

- 4 mA to 20 mA

- 3.8 mA to 21 mA

- 3.2 mA to 24 mA

- NAMUR-compliant alarm currents

- Downscale alarm current = 3.2 mA

- Upscale alarm current = 22.8 mA/24 mA

- Total unadjusted error (TUE): 0.133% maximum

- INL error: 0.004% FSR maximum

- · Output TC: 3 ppm/°C typical

- Quiescent current: 200 μA maximum

- Flexible SPI-compatible serial digital interface with Schmitt triggered inputs

- On-chip fault alerts via FAULT pin or alarm current Automatic readback of fault register on each write cycle

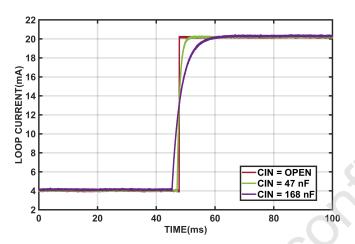

- · Slew rate control function

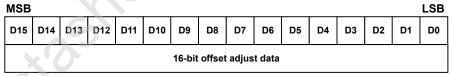

- · Gain and offset adjust registers

- On-chip reference TC: 4 ppm/°C Typ.

- Selectable regulated voltage output

- Loop voltage range: 5.5 V to 60 V

- Temperature range: -40°C to +125°C

- TSSOP packages

# **Applications**

- · Industrial process control

- 4 mA to 20 mA loop-powered transmitters

- Smart transmitters

- HART network connectivity

### **Description**

The TPC2221 is an all-in-one, loop-powered digital-toanalog converter (DAC) that is tailored to the requirements of intelligent sensor manufacturers within the industrial automation sector. This DAC offers a highly accurate, fully integrated, and cost-effective solution in a compact TSSOP package.

It features a built-in voltage regulator that not only powers the TPC2221 but also other components within the sensor, providing a stable output voltage between 1.8 V and 12 V.The TPC2221 also incorporates 1.915 V and 2.5 V reference voltages, which means there's no need for additional discrete regulators or voltage references.

It is fully compatible with the standard HART® FSK protocol used in remote sensor communication without any loss in performance. The device's high-speed serial interface operates at 30 MHz and supports easy integration with popular microprocessors and microcontrollers through a SPI-compatible, 3-wire interface.

The TPC2221 ensures monotonicity up to 16 bits and delivers exceptional performance with 0.0015% integral nonlinearity, 0.0012% offset error, and 0.0006% gain error under typical operating conditions.

Lastly, the TPC2221 is offered in a 28-lead TSSOP package and is designed to operate over an extended industrial temperature range from -40°C to +125°C.

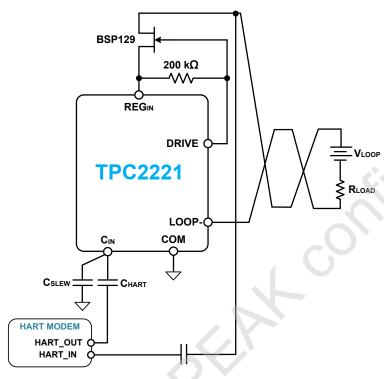

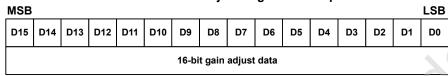

## **Typical Application Circuit**

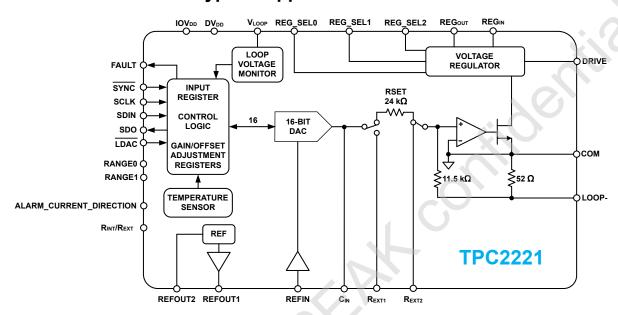

Figure 1. FUNCTIONAL BLOCK DIAGRAM

www.3peak.com 2 / 48 BA20240601A0

## **Table of Contents**

| Features                                |    |

|-----------------------------------------|----|

| Applications                            | 1  |

| Description                             |    |

| Typical Application Circuit             | 2  |

| Product Family Table                    | 4  |

| Revision History                        | 4  |

| Pin Configuration and Functions         | 5  |

| Specifications                          | 8  |

| Absolute Maximum Ratings (1)            | 8  |

| ESD, Electrostatic Discharge Protection | 8  |

| Recommended Operating Conditions        | 8  |

| Thermal Information                     | 9  |

| Electrical Characteristics              | 10 |

| Timing Requirements                     | 17 |

| Timing Diagrams                         | 19 |

| Typical Performance Characteristics     | 20 |

| Detailed Description                    | 28 |

| Overview                                | 28 |

| Functional Block Diagram                | 28 |

| Feature Description                     | 28 |

| Functional Modes                        | 28 |

| Application and Implementation          | 42 |

| Application Information                 | 42 |

| Typical Application                     | 42 |

| Layout                                  | 44 |

| Layout Guideline                        | 44 |

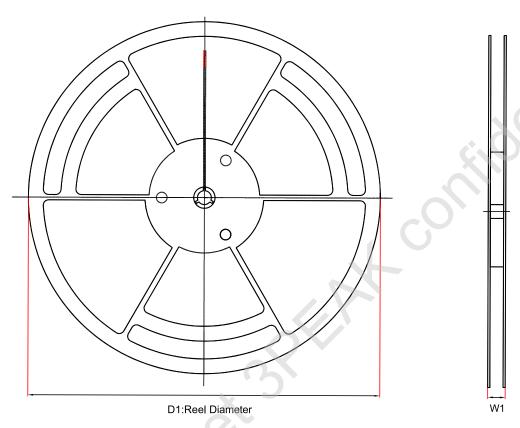

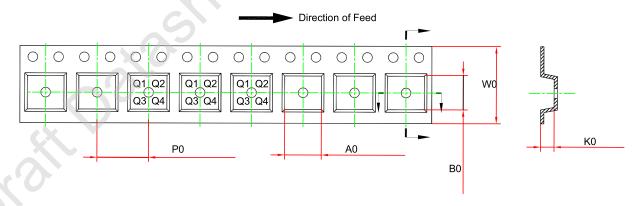

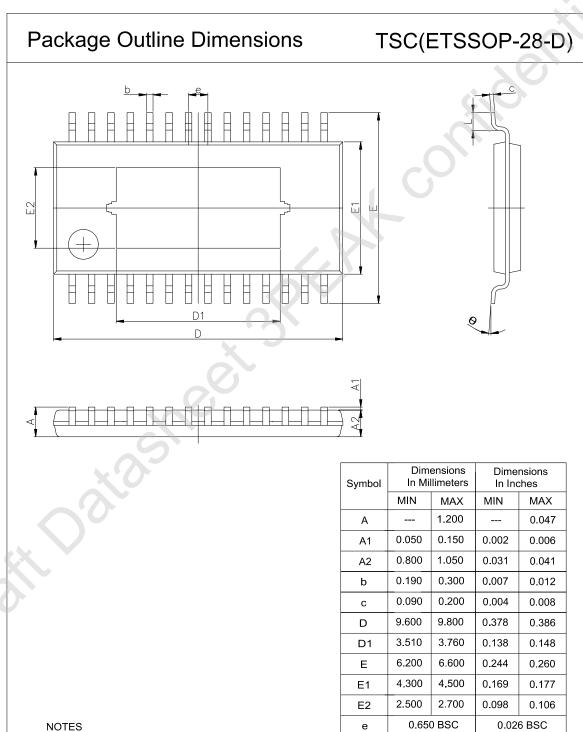

| Tape and Reel Information               | 45 |

| Package Outline Dimensions              | 46 |

| ETSSOP-28-D                             | 46 |

| Order Information                       | 47 |

| IMPORTANT NOTICE AND DISCLAIMER         | 48 |

## **Product Family Table**

| Order Number | Resolution | Output  | Package |

|--------------|------------|---------|---------|

| TPC2221-TSFR | 16         | Current | TSSOP28 |

### **Revision History**

| Date     | Revision  | Notes                |

|----------|-----------|----------------------|

| 2025-3-1 | Rev.Pre.0 | Preliminary Version. |

www.3peak.com 4 / 48 BA20240601A0

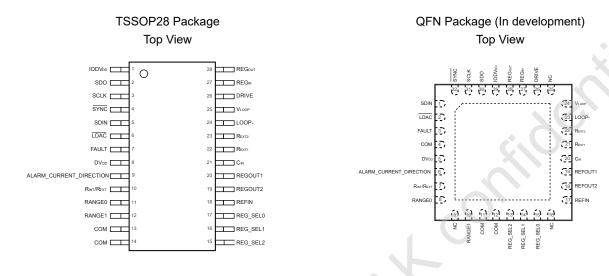

## **Pin Configuration and Functions**

**Table 1. Pin Function Descriptions**

| Pin No. |     |                             |                                                                                                                                                                                                                                                                                                                   |

|---------|-----|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSSOP   | QFN | Mnemonic                    | Description                                                                                                                                                                                                                                                                                                       |

| 1       | 29  | IODV <sub>DD</sub>          | Digital Interface Supply Pin. Digital thresholds are referenced to the voltage applied to this pin.                                                                                                                                                                                                               |

| 2       | 30  | SDO                         | Serial Data Output. Used to clock data from the input shift register.  Data is clocked out on the rising edge of SCLK and is valid on the falling edge of SCLK.                                                                                                                                                   |

| 3       | 31  | SCLK                        | Serial Clock Input. Data is clocked into the input shift register on the falling edge of SCLK.                                                                                                                                                                                                                    |

| 4       | 32  | SYNC                        | Frame Synchronization Input, Active Low. This is the frame synchronization signal for the serial interface. When \$\overline{SYNC}\$ is low, data is transferred on the falling edge of SCLK. The input shift register data is latched on the rising edge of \$\overline{SYNC}\$.                                 |

| 5       | 1   | SDIN                        | Serial Data Input. Data must be valid on the falling edge of SCLK.                                                                                                                                                                                                                                                |

| 6       | 2   | LDAC                        | Load DAC Input, Active Low. This pin is used to update the DAC register and, consequently, the output current. If $\overline{\text{LDAC}}$ is tied permanently low, the DAC register is updated on the rising edge of $\overline{\text{SYNC}}$ . The $\overline{\text{LDAC}}$ pin should not be left unconnected. |

| 7       | 3   | FAULT                       | Fault Alert Output Pin, Active High. This pin is asserted high when a fault is detected.                                                                                                                                                                                                                          |

| 8       | 5   | DV <sub>DD</sub>            | 3.3 V Digital Power Supply Output. This pin should be decoupled to COM with 100 nF and 4.7 µF capacitors                                                                                                                                                                                                          |

| 9       | 6   | ALARM_CURREN<br>T_DIRECTION | Alarm Current Direction Select. This pin is used to select whether the alarm current is upscale current (22.8 mA/24 mA) or downscale (3.2 mA). Connecting this pin to DV <sub>DD</sub> selects an upscale alarm current                                                                                           |

www.3peak.com 5 / 48 BA20240601A0

| Pin No.    |            |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|------------|------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TSSOP      | QFN        | Mnemonic                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|            |            |                                    | (22.8 mA/24 mA); connecting this pin to COM selects a downscale alarm current (3.2 mA).                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 10         | 7          | R <sub>INT</sub> /R <sub>EXT</sub> | Current Setting Resistor Select. When this pin is connected to $DV_DD$ , the internal current setting resistor is selected. When this pin is connected to COM, the external current setting resistor is selected. An external resistor can be connected between the $R_EXT1$ and $R_EXT2$ pins.                                                                                                                                                                                                                           |  |  |

| 44 40      | 0.40       | RANGE0                             | Divital land Diva Theoretical state has been supported by                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 11, 12     | 8, 10      | RANGE1                             | Digital Input Pins. These two pins select the loop current range.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 13, 14     | 4, 11, 12  | СОМ                                | Ground Reference Pin for the device. It is recommended that a 4.7 V Zener diode be placed between the LOOP- and COM pins.                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 15, 16, 17 | 13, 14, 15 | REG_SEL2,<br>REG_SEL1,<br>REG_SEL0 | These three pins together select the regulator output (REG $_{\text{OUT}}$ ) voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 18         | 17         | REFIN                              | Reference Voltage Input. V <sub>REFIN</sub> = 2.5 V for specified performance.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 19         | 18         | REFOUT2                            | Internal Reference Voltage Output 2. It is recommended to connect a 100 nF capacitor from this pin to COM.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 20         | 19         | REFOUT1                            | Internal Reference Voltage Output 1 (2.5V). It is recommended to connect a 100 nF capacitor from this pin to COM.                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 21         | 20         | C <sub>IN</sub>                    | External Capacitor Connection and HART FSK Input. An external capacitor connected from CIN to COM implements an output slew rate control function. HART FSK signaling can also be coupled through a capacitor to this pin.                                                                                                                                                                                                                                                                                                |  |  |

| 22, 23     | 21, 22     | REXT1, REXT2                       | Connection for External Current Setting Resistor. A precision 24 $k\Omega$ resistor can be connected between these pins for improved performance.                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 24         | 23         | LOOP-                              | Loop Current Return Pin. The COM and LOOP- pins can be used to sense the loop current across the internal 52 $\Omega$ resistor. Note that the voltage measured at LOOP- is be negative with respect to COM.                                                                                                                                                                                                                                                                                                               |  |  |

| 25         | 23         | V <sub>LOOP</sub>                  | Voltage Input Pin. Voltage input range is 0 V to 2.5 V. The voltage applied to this pin is digitized to eight bits, which are available in the fault register. This pin can be used for general-purpose voltage monitoring, but it is intended for monitoring of the loop supply voltage. Connecting the loop voltage to this pin via a 20:1 resistor divider allows the device to monitor and feedback the loop voltage. The device also generates an alert if the loop voltage is close to the minimum operating value. |  |  |

| 26         | 26         | DRIVE                              | Gate Connection for External Depletion Mode MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 27         | 27         | REG <sub>IN</sub>                  | Voltage Regulator Input. The loop voltage can be connected directly to this pin. Or to reduce on- chip power dissipation, an external pass transistor can be connected at this pin to stand off the loop voltage.                                                                                                                                                                                                                                                                                                         |  |  |

www.3peak.com 6 / 48 BA20240601A0

| Pin No. |           | Manager            | Bassintian                                                                                                                                                                                                                           |

|---------|-----------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSSOP   | QFN       | Mnemonic           | Description                                                                                                                                                                                                                          |

| 28      | 28        | REG <sub>out</sub> | Voltage Regulator Output. Pin selectable values are from 1.8 V to 12 V via the REG_SEL0, REG_SEL1, and REG_SEL2 pins. If REGOUT is driving a microconverter supply, this pin should be decoupled to COM with a >1 $\mu F$ capacitor. |

| N/A     | 9, 16, 25 | NC                 | No Connect. Do not connect to this pin.                                                                                                                                                                                              |

|         |           | EPAD               | Exposed Paddle. The exposed paddle should be connected to the same potential as the COM pin and to a copper plane for optimum thermal performance.                                                                                   |

www.3peak.com 7 / 48 BA20240601A0

## **Specifications**

### Absolute Maximum Ratings (1)

| Parameter                                                                                                                         | Rating                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| REG <sub>IN</sub> to COM                                                                                                          | -0.3 V to +70 V                                                 |

| REG <sub>OUT</sub> to COM                                                                                                         | -0.3 V to +20 V                                                 |

| Digital Inputs to COM, RANGE0, RANGE1, R <sub>INT</sub> /R <sub>EXT</sub> , ALARM_CURRENT_DIRECTION, REG_SEL0, REG_SEL1, REG_SEL2 | -0.3 V to DV <sub>DD</sub> +0.3 V or +7 V (whichever is less)   |

| Digital Inputs to COM, SCLK, SDIN, SYNC, LDAC                                                                                     | -0.3 V to IODV <sub>DD</sub> +0.3 V or +7 V (whichever is less) |

| Digital Outputs to COM, SDO, FAULT                                                                                                | -0.3 V to IODV <sub>DD</sub> +0.3 V or +7 V (whichever is less) |

| REFIN to COM                                                                                                                      | -0.3 V to +7 V                                                  |

| REFOUT1, REFOUT2                                                                                                                  | -0.3 V to +4.7 V                                                |

| V <sub>LOOP</sub> to COM                                                                                                          | -0.3 V to +70 V                                                 |

| LOOP - to COM                                                                                                                     | -5 V to +0.3 V                                                  |

| DV <sub>DD</sub> to COM                                                                                                           | -0.3 V to +7 V                                                  |

| IODV <sub>DD</sub> to COM                                                                                                         | -0.3 V to +7 V                                                  |

| R <sub>EXT1</sub> , C <sub>IN</sub> to COM                                                                                        | -0.3 V to +4.3 V                                                |

| R <sub>EXT2</sub> to COM                                                                                                          | -0.3 V to +0.3 V                                                |

| DRIVE to COM                                                                                                                      | -0.3 V to +11 V                                                 |

| Operating Temperature Range (T <sub>A</sub> )                                                                                     | -40°C to +125°C                                                 |

| Storage Temperature Range                                                                                                         | -65°C to +150°C                                                 |

| Power Dissipation                                                                                                                 | $(T_{J MAX} - T_{A})/\theta_{JA}$                               |

| Lead Temperature, Soldering (10 sec)                                                                                              | JEDEC Industry Standard J-STD-020                               |

<sup>&</sup>lt;sup>(1)</sup>Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

### **ESD, Electrostatic Discharge Protection**

|     | Parameter                | Condition                  | Minimum Level | Unit |

|-----|--------------------------|----------------------------|---------------|------|

| НВМ | Human Body Model ESD     | ANSI/ESDA/JEDEC JS-001 (1) | 2             | kV   |

| CDM | Charged Device Model ESD | ANSI/ESDA/JEDEC JS-002 (2) | 1             | kV   |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### **Recommended Operating Conditions**

| Parameter                   | MIN | NOM | MAX | UNIT |

|-----------------------------|-----|-----|-----|------|

| (REG <sub>IN</sub> - LOOP-) | 5.5 |     | 60  | V    |

www.3peak.com 8 / 48 BA20240601A0

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

| Parameter                         | MIN | NOM | MAX | UNIT |

|-----------------------------------|-----|-----|-----|------|

| (LOOP COM)                        | -5  |     | 0   | V    |

| IODV <sub>DD</sub> - COM          | 1.7 |     | 5.5 | V    |

| DV <sub>DD</sub> - COM            |     | 3.3 |     | V    |

| Specified performance temperature | -40 |     | 125 | °C   |

### **Thermal Information**

| THERMAL METRIC |                                           | QFN (In<br>Development) | TSSOP   | UNIT |

|----------------|-------------------------------------------|-------------------------|---------|------|

|                |                                           | 32 PINS                 | 28 PINS |      |

| $\theta_{JA}$  | Junction-to-ambient thermal resistance    | 40                      | 32      | °C/W |

| θυς            | Junction-to-case (top) thermal resistance | 7                       | 9       | °C/W |

www.3peak.com 9 / 48 BA20240601A0

### **Electrical Characteristics**

Loop voltage = 24 V; REFIN = 2.5 V external;  $R_L$  = 250  $\Omega$ ; external NMOS connected; all loop current ranges; all specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

| 24244                            |                                                  |        | 7.6   | 1111  | 1              |

|----------------------------------|--------------------------------------------------|--------|-------|-------|----------------|

| PARAMETER <sup>1</sup>           | TEST CONDITIONS                                  | MIN    | TYP   | MAX   | UNIT           |

| ACCURACY, INTERNA                | L Rset                                           |        |       |       |                |

| Resolution                       |                                                  | 16     |       |       | Bits           |

| Total Unadjusted                 | T <sub>A</sub> =-40°C to +125°C,                 | -0.18  |       | 0.18  | %FSR           |

| Error(TUE)                       | T <sub>A</sub> =25 °C                            | -0.163 |       | 0.163 | %FSR           |

| TUE Long-Term<br>Stability       | Drift after 1000 hours at T <sub>A</sub> = 125°C |        | TBD   |       | ppm FSR/<br>°C |

| Relative Accuracy (INL)          | T <sub>A</sub> =-40°C to +125°C,                 | -0.012 |       | 0.012 | %FSR           |

| Differential Nonlinearity (DNL)  | T <sub>A</sub> =-40°C to +125°C                  | -1     |       | 1     | LSB            |

| 0" 1"                            | T <sub>A</sub> =-40°C to +125°C                  | -0.056 |       | 0.056 | %FSR           |

| Offset Error                     | T <sub>A</sub> =25°C                             | -0.01  |       | 0.01  | %FSR           |

| Offset Error TC <sup>3</sup>     | 0)                                               |        | TBD   |       | ppm FSR/<br>°C |

| 0 : -                            | T <sub>A</sub> =-40°C to +125°C                  | -0.107 |       | 0.107 | %FSR           |

| Gain Error                       | T <sub>A</sub> = 25°C                            | -0.09  |       | 0.09  | %FSR           |

| Gain Error TC <sup>3</sup>       | V6                                               |        | TBD   |       | ppm FSR/<br>°C |

| - " O . I . F                    | T <sub>A</sub> =-40°C to +125°C                  | -0.126 |       | 0.126 | %FSR           |

| Full-Scale Error                 | T <sub>A</sub> = 25°C                            | -0.1   |       | 0.1   | %FSR           |

| Full-Scale Error TC <sup>3</sup> |                                                  |        | TBD   |       | ppm FSR/<br>℃  |

| Downscale Alarm<br>Current       |                                                  | 3.19   |       | 3.21  | mA             |

| Lineagle Alerm Current           | 4 mA to 20 mA and 3.8 mA to 21 mA ranges         | 22.77  |       | 22.83 | mA             |

| Upscale Alarm Current            | 3.2 mA to 24 mA range                            | 23.97  |       | 24.03 | mA             |

| ACCURACY, EXTERNA                | AL R <sub>SET</sub> (24 kΩ)                      |        |       |       |                |

| Resolution                       |                                                  | 16     |       |       | Bits           |

| Total Unadjusted Error           | T <sub>A</sub> =-40°C to +125°C                  | -0.08  |       | 0.08  | %FSR           |

| (TUE) <sup>2</sup>               | T <sub>A</sub> =25°C                             | -0.07  |       | 0.07  | %FSR           |

| TUE Long-Term<br>Stability       | Drift after 1000 hours at T <sub>A</sub> = 125°C |        | TBD   |       | ppm FSR/<br>℃  |

| Relative Accuracy (INL)          | T <sub>A</sub> =-40°C to +125°C                  | -0.012 | ±0.01 | 0.012 | %FSR           |

www.3peak.com 10 / 48 BA20240601A0

| PARAMETER1                                             | TEST CONDITIONS                                                                                   | MIN             | TYP   | MAX   | UNIT           |

|--------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------|-------|-------|----------------|

| Differential Nonlinearity (DNL)                        | Guaranteed monotonic                                                                              | -1              |       | 1     | LSB            |

| Officet France                                         | T <sub>A</sub> =-40°C to +125°C                                                                   | -0.03           |       | +0.03 | %FSR           |

| Offset Error                                           | T <sub>A</sub> =25°C                                                                              | -0.01           |       | +0.01 | %FSR           |

| Offset Error TC <sup>3</sup>                           |                                                                                                   |                 | TBD   |       | ppm FSR/<br>°C |

| Cain Fran                                              | T <sub>A</sub> =-40°C to +125°C                                                                   | -0.55           |       | 0.055 | %FSR           |

| Gain Error                                             | T <sub>A</sub> =25°C                                                                              | -0.046          |       | 0.046 | %FSR           |

| Gain Error TC <sup>3</sup>                             |                                                                                                   |                 | TBD   |       | ppm FSR/<br>°C |

| Full-Scale Error                                       | T <sub>A</sub> =-40°C to +125°C                                                                   | -0.08           |       | 0.08  | %FSR           |

| Full-Scale Error                                       | T <sub>A</sub> =25°C                                                                              | -0.057          |       | 0.057 | %FSR           |

| Full-Scale Error TC <sup>3</sup>                       |                                                                                                   |                 | TBD   |       | ppm FSR/<br>°C |

| Downscale Alarm<br>Current                             | Output unloaded                                                                                   | 3.08            | 3     | 3.21  | mA             |

| Upscale Alarm Current                                  | 4 mA to 20 mA and 3.8 mA to 21 mA ranges                                                          | 22.78           |       | 23    | mA             |

| Opscale Alaim Current                                  | 3.2 mA to 24 mA range                                                                             | 23.99           |       | 24.01 | mA             |

| OUTPUT CHARACTER                                       | RISTICS <sup>3</sup>                                                                              |                 |       |       |                |

| Loop Compliance                                        | REG <sub>OUT</sub> < 5.5 V, loop current = 24 mA                                                  | LOOP- + 5.5     |       |       | V              |

| Voltage <sup>4</sup>                                   | REG <sub>OUT</sub> = 12 V, loop current = 24 mA                                                   | LOOP- +<br>12.5 |       |       | V              |

| Loop Current Long-                                     | Drift after 1000 hours at T <sub>A</sub> = 125°C, loop current = 12 mA, internal R <sub>SET</sub> |                 | TBD   |       | ppm/FSR        |

| Term Stability                                         | Drift after 1000 hours at T <sub>A</sub> = 125°C, loop current = 12 mA, external R <sub>SET</sub> |                 | TBD   |       | ppm/FSR        |

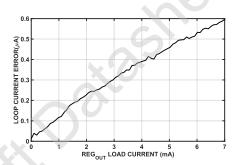

| Loop Current Error vs. REG <sub>OUT</sub> Load Current | Loop current = 12 mA, load current from REG <sub>OUT</sub> = 5 mA                                 |                 | 0.1   |       | μΑ/mA          |

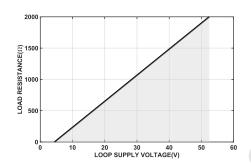

| Resistive Load                                         | See <b>Figure 19</b> for a load line graph                                                        | 0               |       | 2     | kΩ             |

| Inductive Load                                         | Stable operation                                                                                  |                 | 50    |       | mH             |

| Power Supply<br>Sensitivity                            | Loop current = 12 mA                                                                              |                 | 0.082 |       | μA/V           |

| Output Impedance                                       |                                                                                                   | 12              | 400   |       | ΜΩ             |

| 0.44.T0                                                | Loop current = 12 mA, internal R <sub>SET</sub>                                                   |                 | TBD   |       | ppm<br>FSR/°C  |

| Output TC                                              | Loop current = 12 mA, external R <sub>SET</sub>                                                   |                 | TBD   |       | ppm<br>FSR/°C  |

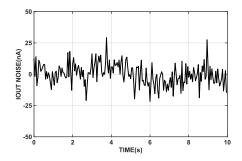

| Output Noise                                           |                                                                                                   |                 |       |       | •              |

| 0.1 Hz to 10 Hz                                        |                                                                                                   |                 | 50    |       | nAp-p          |

www.3peak.com 11 / 48 BA20240601A0

| PARAMETER <sup>1</sup>                       | TEST CONDITIONS                                                     | MIN   | TYP   | MAX   | UNIT   |

|----------------------------------------------|---------------------------------------------------------------------|-------|-------|-------|--------|

| 500 Hz to 10 kHz                             | HART bandwidth; measured across 500 $\Omega$ load                   |       | 0.28  |       | mV rms |

|                                              | At 1 kHz                                                            |       | 195   |       | nA/√Hz |

| Noise Spectral Density                       | At 10 kHz                                                           |       | 256   |       | nA/√Hz |

| REFERENCE INPUT (R                           | REFIN PIN) <sup>3</sup>                                             |       |       |       |        |

| Reference Input<br>Voltage <sup>5</sup>      | For specified performance                                           |       | 2.5   | 70    | V      |

| DC Input Impedance                           |                                                                     | 75    | 800   |       | ΜΩ     |

| REFERENCE OUTPUT                             |                                                                     |       |       |       |        |

| REFOUT1 Pin                                  |                                                                     |       |       |       |        |

| Output Voltage                               | T <sub>A</sub> = 25°C                                               | 2.495 | 2.5   | 2.505 | V      |

| Temperature<br>Coefficient                   |                                                                     |       | 4     |       | ppm/°C |

| Output Noise (0.1 Hz to 10 Hz) <sup>3</sup>  |                                                                     |       | 10    |       | μV p-p |

| Noise Spectral                               | At 1 kHz                                                            |       | 360   |       | nV/√Hz |

| Density <sup>3</sup>                         | At 10 kHz                                                           |       | 35    |       | nV/√Hz |

| Output Voltage Drift vs. Time <sup>3</sup>   | Drift after 1000 hours at T <sub>A</sub> = 125°C                    |       | TBD   |       | ppm    |

| Capacitive Load <sup>3</sup>                 | Recommended operation                                               |       | 100   |       | nF     |

| Load Current <sub>3, 6</sub>                 |                                                                     |       | 1     |       | mA     |

| Short-Circuit Current <sup>3</sup>           | Short circuit to COM                                                |       | 1.4   |       | mA     |

| Power Supply<br>Sensitivity <sup>3</sup>     | 5                                                                   |       | 7.2   | 12    | μV/V   |

| Th 3                                         | First temperature cycle                                             |       | TBD   |       | ppm    |

| Thermal Hysteresis <sup>3</sup>              | Second temperature cycle                                            |       | TBD   |       | ppm    |

| Load Regulation <sup>3</sup>                 | Measured at 0 mA and 1 mA loads                                     |       | 0.375 |       | mV/mA  |

| Output Impedance                             |                                                                     |       | 0.375 |       | Ω      |

| REFOUT2 Pin                                  |                                                                     |       |       |       |        |

| Output Voltage                               | T <sub>A</sub> = 25°C                                               |       | 2.45  |       | V      |

| Output Impedance                             |                                                                     |       | 72    |       | kΩ     |

| REG <sub>OUT</sub> OUTPUT                    | Voltage regulator output                                            |       |       |       |        |

| Output Voltage                               | See Table 5/Table 6                                                 | 1.8   | 0     | 20    | V      |

| Output Voltage TC <sup>3</sup>               |                                                                     |       | TBD   |       | ppm/°C |

| Output Voltage<br>Accuracy                   |                                                                     | -4    | ±2    | 4     | %      |

| Externally Available Current <sub>3, 6</sub> | Assuming 4 mA is flowing in the loop and during HART communications | 3.15  |       |       | mA     |

| Short-Circuit Current                        | Short to COM                                                        |       | 7.05  |       | mA     |

www.3peak.com 12 / 48 BA20240601A0

| PARAMETER <sup>1</sup>                       | TEST CONDITIONS                                                     | MIN                      | TYP                      | MAX                       | UNIT  |

|----------------------------------------------|---------------------------------------------------------------------|--------------------------|--------------------------|---------------------------|-------|

| 1. D 1.1. 3                                  | Internal NMOS                                                       |                          | 5                        |                           | μV/V  |

| Line Regulation <sup>3</sup>                 | External NMOS                                                       |                          | 2                        |                           | μV/V  |

| Inductive Load                               | Stable operation                                                    |                          | 50                       |                           | mH    |

| Capacitive Load                              | Recommended operation                                               | 2                        | 10                       |                           | μF    |

| ADC ACCURACY                                 |                                                                     |                          |                          |                           |       |

| Die Temperature                              |                                                                     |                          | ±5                       | 70                        | °C    |

| V <sub>LOOP</sub> Input                      |                                                                     |                          | 1                        | <b>\)</b>                 | %     |

| DV <sub>DD</sub> OUTPUT                      | Can be overdriven up to 5.5 V                                       |                          |                          |                           |       |

| Externally Available Current <sub>3, 6</sub> | Assuming 4 mA is flowing in the loop and during HART communications | 3.15                     |                          |                           | mA    |

| Short-Circuit Current                        |                                                                     |                          | 4.5                      |                           | mA    |

| Load Regulation                              | Measured at 0 mA and 2 mA loads                                     |                          | 4.5                      |                           | mV/mA |

| DIGITAL INPUTS <sup>3</sup>                  | SCLK, SYNC, SDIN, LDAC                                              |                          |                          |                           |       |

| Input High Voltage,<br>VIH                   |                                                                     | 0.7 × IODV <sub>DD</sub> |                          |                           | V     |

| Input Low Voltage, VIL                       |                                                                     |                          |                          | 0.25 × IODV <sub>DD</sub> | V     |

|                                              | IODV <sub>DD</sub> = 1.8 V                                          |                          | 0.21                     |                           | V     |

| Hysteresis                                   | IODV <sub>DD</sub> = 3.3 V                                          |                          | 0.63                     |                           | V     |

|                                              | IODV <sub>DD</sub> = 5.5 V                                          |                          | 1.46                     |                           | V     |

| Input Current                                | Per pin                                                             | -0.015                   |                          | 0.015                     | μA    |

| Pin Capacitance                              | Per pin                                                             |                          | 5                        |                           | pF    |

| DIGITAL OUTPUTS <sup>3</sup>                 |                                                                     |                          |                          |                           |       |

| SDO Pin                                      |                                                                     |                          |                          |                           |       |

| Output Low Voltage,<br>V <sub>OL</sub>       |                                                                     |                          |                          | 0.4                       | V     |

| Output High Voltage,<br>V <sub>OH</sub>      |                                                                     |                          | IODV <sub>DD</sub> - 0.5 |                           | V     |

| High Impedance<br>Leakage Current            |                                                                     | -0.01                    |                          | 0.01                      | μA    |

| High Impedance Output Capacitance            |                                                                     |                          | 5                        |                           | pF    |

| FAULT Pin                                    |                                                                     | 1                        |                          | 1                         |       |

| Output Low Voltage,<br>V <sub>OL</sub>       |                                                                     |                          |                          | 0.4                       | V     |

| Output Low Voltage,                          |                                                                     | IODV <sub>DD</sub> - 0.5 |                          |                           | V     |

| FAULT THRESHOLDS                             |                                                                     |                          |                          |                           |       |

www.3peak.com 13 / 48 BA20240601A0

| PARAMETER <sup>1</sup>  | TEST CONDITIONS                              | MIN | TYP                 | MAX | UNIT |

|-------------------------|----------------------------------------------|-----|---------------------|-----|------|

|                         |                                              |     | I <sub>LOOP</sub> – |     |      |

| I <sub>LOOP</sub> Under |                                              |     | 0.01%               |     | mA   |

|                         |                                              |     | FSR                 |     |      |

|                         |                                              |     | I <sub>LOOP</sub> + |     |      |

| I <sub>LOOP</sub> Over  |                                              |     | 0.01%               |     | mA   |

|                         |                                              |     | FSR                 |     |      |

| Temp 140°C              | Fault removed when temperature is ≤ 125°C    |     | 133                 |     | °C   |

| Temp 100°C              | Fault removed when temperature is ≤ 85°C     |     | 90                  |     | °C   |

| V <sub>LOOP</sub> 6V    | Fault removed when V <sub>LOOP</sub> ≥ 0.4 V |     | 0.3                 |     | V    |

| V <sub>LOOP</sub> 12V   | Fault removed when V <sub>LOOP</sub> ≥ 0.7 V |     | 0.6                 |     | V    |

#### Note:

www.3peak.com 14 / 48 BA20240601A0

<sup>&</sup>lt;sup>1</sup> Temperature range: −40°C to +125°C; typical at +25°C. System level total error can be reduced using the offset and gain registers.

<sup>&</sup>lt;sup>2</sup> Total unadjusted error is the total measured error (offset error + gain error + linearity error + output drift over temperature) after factory calibration of the TPC2221

<sup>&</sup>lt;sup>3</sup> Guaranteed by design and characterization; not production tested.

<sup>&</sup>lt;sup>4</sup> The voltage between LOOP- and REG<sub>IN</sub> must be 5.5 V or greater.

<sup>&</sup>lt;sup>5</sup> The TPC2221 is factory calibrated with an external 2.5 V reference connected to REFIN.

<sup>&</sup>lt;sup>6</sup>This is the current that the output is capable of sourcing. The load current originates from the loop and, therefore, contributes to the total current consumption figure.

Loop voltage = 24 V; REFIN = REFOUT1 (2.5 V internal reference);  $R_L$  = 250  $\Omega$ ; external NMOS connected; all loop current ranges; all specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

| PARAMETER <sup>1,2</sup> | TEST CONDITIONS                 | MIN    | TYP     | MAX   | UNIT          |

|--------------------------|---------------------------------|--------|---------|-------|---------------|

| ACCURACY, INTERNA        | L R <sub>SET</sub>              |        |         |       |               |

| Total Unadjusted Error   | T <sub>A</sub> =-40°C to +125°C | -0.157 |         | 0.157 | %FSR          |

| (TUE) <sup>3</sup>       | T <sub>A</sub> =25°C            | -0.141 |         | 0.141 | %FSR          |

| Relative Accuracy        | T <sub>A</sub> =-40°C to +125°C | -0.012 |         | 0.012 | %FSR          |

| (INL)                    | T <sub>A</sub> =25°C            | -0.01  |         | 0.01  | %FSR          |

| Officet Francis          | T <sub>A</sub> =-40°C to +125°C | -0.04  |         | 0.04  | %FSR          |

| Offset Error             | T <sub>A</sub> =25°C            | -0.025 | ±0.0025 | 0.025 | %FSR          |

| Offset Error TC          |                                 |        | TBD     |       | ppm FSR/      |

| O-i F                    | T <sub>A</sub> =-40°C to +125°C | -0.128 |         | 0.128 | %FSR          |

| Gain Error               | T <sub>A</sub> =25°C            | -0.11  |         | 0.11  | %FSR          |

| Gain Error TC            |                                 |        | TBD     |       | ppm<br>FSR/°C |

| Full Cools Eman          | T <sub>A</sub> =-40°C to +125°C | -0.157 |         | 0.157 | %FSR          |

| Full-Scale Error         | T <sub>A</sub> =25°C            | -0.134 |         | 0.134 | %FSR          |

| Full-Scale Error TC      | ×, ,                            |        | TBD     |       | ppm<br>FSR/°C |

| ACCURACY, EXTERNA        | AL R <sub>SET</sub> (24 kΩ)     |        |         | 1     |               |

| Total Unadjusted Error   | T <sub>A</sub> =-40°C to +125°C | -0.133 |         | 0.133 | %FSR          |

| (TUE) <sup>3</sup>       | T <sub>A</sub> =25°C            | -0.129 |         | 0.129 | %FSR          |

| Relative Accuracy        | T <sub>A</sub> =-40°C to +125°C | -0.012 |         | 0.012 | %FSR          |

| (INL)                    | T <sub>A</sub> = 25°C           | -0.011 |         | 0.011 | %FSR          |

| Offset Error             | T <sub>A</sub> =-40°C to +125°C | -0.029 |         | 0.029 | %FSR          |

| Oliset Error             | T <sub>A</sub> = 25°C           | -0.01  |         | 0.01  | %FSR          |

| Offset Error TC          |                                 |        | TBD     |       | ppm<br>FSR/°C |

| 0 : 5                    | T <sub>A</sub> =-40°C to +125°C | -0.106 |         | 0.106 | %FSR          |

| Gain Error               | T <sub>A</sub> = 25°C           | -0.097 |         | 0.097 | %FSR          |

| Gain Error TC            |                                 |        | TBD     |       | ppm<br>FSR/°C |

| Full Cools F             | T <sub>A</sub> =-40°C to +125°C | -0.133 |         | 0.133 | %FSR          |

| Full-Scale Error         | T <sub>A</sub> = 25°C           | -0.108 |         | 0.108 | %FSR          |

| Full-Scale Error TC      |                                 |        | TBD     |       | ppm<br>FSR/°C |

#### Note:

www.3peak.com 15 / 48 BA20240601A0

<sup>&</sup>lt;sup>1</sup> Temperature range: −40°C to +125°C; typical at +25°C.

www.3peak.com 16 / 48 BA20240601A0

<sup>&</sup>lt;sup>2</sup> Specifications guaranteed by design and characterization; not production tested.

<sup>&</sup>lt;sup>3</sup> Total unadjusted error is the total measured error (offset error + gain error + linearity error + output drift over temperature) after factory calibration of the TPC2221. System level total error can be reduced using the offset and gain registers.

#### **AC PERFORMANCE CHARACTERISTICS**

Loop voltage = 24 V; REFIN = 2.5 V external;  $R_L$  = 250  $\Omega$ ; all specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

| PARAMETER                        | TEST CONDITIONS                                   | MIN | TYP | MAX | UNIT  |  |  |

|----------------------------------|---------------------------------------------------|-----|-----|-----|-------|--|--|

| DYNAMIC PERFORMANCE <sup>1</sup> |                                                   |     |     |     |       |  |  |

| Loop Current Settling Time       | To 0.1% FSR, C <sub>IN</sub> = open circuit       |     | 30  |     | μs    |  |  |

| Loop Current Slew<br>Rate        | C <sub>IN</sub> = open circuit                    |     | 533 |     | μA/μs |  |  |

| AC Loop Voltage<br>Sensitivity   | 1200 Hz to 2200 Hz, 5 Vp-p, R <sub>L</sub> = 3 kΩ |     | 1.3 |     | μA/V  |  |  |

#### Note:

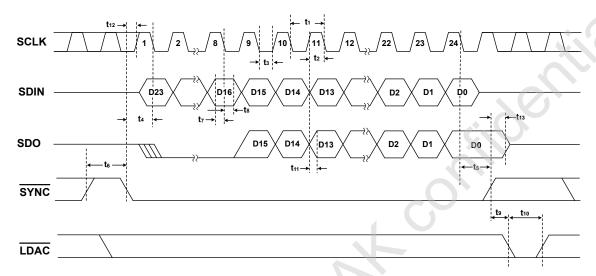

### **Timing Requirements**

Loop voltage = 24 V; REFIN = 2.5 V external;  $R_L$  = 250  $\Omega$ ; all specifications  $T_{MIN}$  to  $T_{MAX}$ ..

**Table 2. TIMING CHARACTERISTICS**

| Parameter <sup>1, 2, 3</sup> | Description                                                   | MIN | TYP | MAX | Unit |

|------------------------------|---------------------------------------------------------------|-----|-----|-----|------|

| t <sub>1</sub>               | SCLK cycle time                                               | 33  |     |     | ns   |

| t <sub>2</sub>               | SCLK high time                                                | 17  |     |     | ns   |

| t <sub>3</sub>               | SCLK low time                                                 | 17  |     |     | ns   |

| t <sub>4</sub>               | SYNC falling edge to SCLK falling edge setup time             | 17  |     |     | ns   |

| t <sub>5</sub>               | SCLK falling edge to SYNC rising edge                         | 10  |     |     | ns   |

| t <sub>6</sub>               | Minimum SYNC high time                                        | 25  |     |     | μs   |

| t <sub>7</sub>               | Data setup time                                               | 5   |     |     | ns   |

| t <sub>8</sub>               | Data hold time                                                | 5   |     |     | ns   |

| t <sub>9</sub>               | SYNC rising edge to LDAC falling edge                         | 25  |     |     | μs   |

| t <sub>10</sub>              | LDAC pulse width low                                          | 10  |     |     | ns   |

| t <sub>11</sub>              | SCLK rising edge to SDO valid (C <sub>L SDO</sub> = 30 pF)    | 70  |     |     | ns   |

| t <sub>12</sub>              | SYNC falling edge to SCLK rising edge setup time              | 0   |     |     | ns   |

| t <sub>13</sub>              | SYNC rising edge to SDO tristate (C <sub>L SDO</sub> = 30 pF) | 70  |     |     | ns   |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization; not production tested.

C<sub>L SDO</sub>= capacitive load on SDO output

Table 3. SPI Watchdog Timeout Periods<sup>1</sup>

| ТО | T1 | T2 | Min | Тур | Max | Unit |

|----|----|----|-----|-----|-----|------|

| 0  | 0  | 0  | 43  | 50  | 59  | ms   |

www.3peak.com 17 / 48 BA20240601A0

<sup>&</sup>lt;sup>1</sup> Temperature range: -40°C to +125°C; typical at +25°C.

$<sup>^2</sup>$ All input signals are specified with  $t_R$  =  $t_F$  = 5 ns (10% to 90% of DVDD) and timed from a voltage level of 1.2 V  $^2$

| ТО | T1 | T2 | Min  | Тур  | Max  | Unit |

|----|----|----|------|------|------|------|

| 0  | 0  | 1  | 87   | 100  | 117  | ms   |

| 0  | 1  | 0  | 436  | 500  | 582  | ms   |

| 0  | 1  | 1  | 873  | 1000 | 1163 | ms   |

| 1  | 0  | 0  | 1746 | 2000 | 2326 | ms   |

| 1  | 0  | 1  | 2619 | 3000 | 3489 | ms   |

| 1  | 1  | 0  | 3493 | 4000 | 4652 | ms   |

| 1  | 1  | 1  | 4366 | 5000 | 5814 | ms   |

#### Note

www.3peak.com 18 / 48 BA20240601A0

Specifications guaranteed by design and characterization; not production tested.

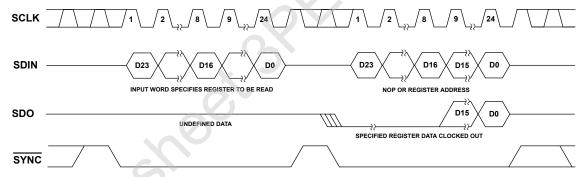

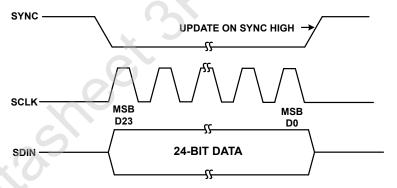

### **Timing Diagrams**

Figure 2. Write Mode Timing Diagram

Figure 3. Readback Mode Timing Diagram

Figure 4. SDO Load Diagram

www.3peak.com 19 / 48 BA20240601A0

### **Typical Performance Characteristics**

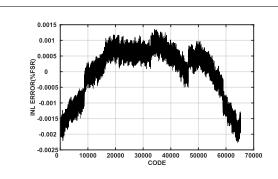

Figure 5. Integral Nonlinearity Error vs. Code

•  $V_{LOOP}$  = 24 V;EXT NMOS; $R_{LOAD}$  = 250  $\Omega$ ; $T_A$  = 25°C;4mA TO 20mA RANGE;EXT  $V_{REF}$ ;EXT  $R_{SET}$

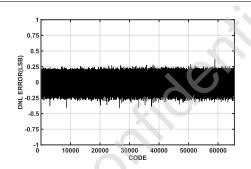

Figure 6. Differential Nonlinearity Error vs. Code

$V_{LOOP}$  = 24 V;EXT NMOS;R<sub>LOAD</sub> = 250  $\Omega$ ;T<sub>A</sub> = 25°C;4mA TO 20mA RANGE;EXT V<sub>REF</sub>;EXT R<sub>SET</sub>

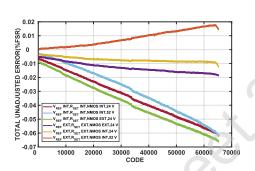

Figure 7. Total Unadjusted Error vs. Code

•  $V_{LOOP} = 24 \text{ V;EXT NMOS;R}_{LOAD} = 250 \Omega;T_A = 25^{\circ}\text{C}$

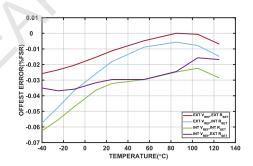

Figure 8. Offset Error vs. Temperature

$V_{LOOP}$ = 24 V;R<sub>LOAD</sub> = 250 Ω;4 mA to 20 mA Range;EXT NMOS

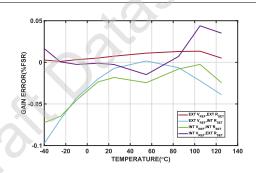

Figure 9. Gain Error vs. Temperature

$V_{LOOP}$  = 24 V;R<sub>LOAD</sub> = 250 Ω;4 mA to 20 mA Range;EXT NMOS

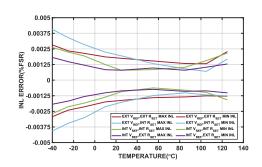

Figure 10. Integral Nonlinearity Error vs. Temperature

•  $V_{LOOP}$  = 24 V; $R_{LOAD}$  = 250  $\Omega$ ;4 mA to 20 mA Range;EXT NMOS

www.3peak.com 20 / 48 BA20240601A0

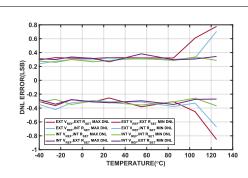

Figure 11. Differential Nonlinearity Error vs. Temperature

•  $V_{LOOP}$  = 24 V; $R_{LOAD}$  = 250  $\Omega$ ;4 mA to 20 mA Range;EXT NMOS

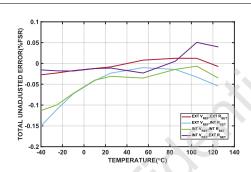

Figure 12. Total Unadjusted Error vs. Temperature

$V_{LOOP}$  = 24 V; $R_{LOAD}$  = 250  $\Omega$ ;4 mA to 20 mA Range;EXT NMOS

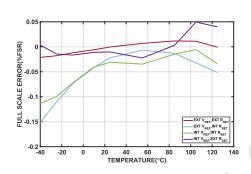

Figure 13. Full-Scale Error vs. Temperature

V<sub>LOOP</sub> = 24 V;R<sub>LOAD</sub> = 250 Ω;4 mA to 20 mA Range;EXT NMOS

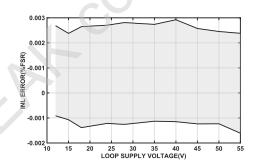

Figure 14. Integral Nonlinearity Error vs. Loop Supply Voltage

EXT NMOS; $R_{LOAD}$  = 250  $\Omega$ ; $T_A$  = 25°C;EXT  $R_{SET}$ ;EXT  $V_{REF}$ ;3.8 mA TO 21 mA Range

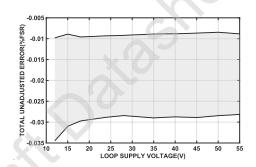

Figure 15. Total Unadjusted Error vs. Loop Supply Voltage

EXT NMOS;R<sub>LOAD</sub> = 250  $\Omega$ ;T<sub>A</sub> = 25°C;EXT R<sub>SET</sub>;EXT V<sub>REF</sub>;3.8 mA TO 21 mA Range

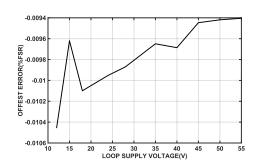

Figure 16. Offset Error vs. Loop Supply Voltage

EXT NMOS; $R_{LOAD}$  = 250 $\Omega$ ; $T_A$  = 25°C;EXT  $R_{SET}$ ;EXT  $V_{REF}$ ;3.8 mA TO 21 mA Range

www.3peak.com 21 / 48 BA20240601A0

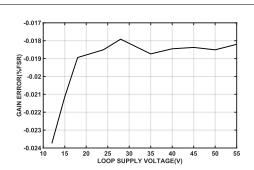

Figure 17. Gain Error vs. Loop Supply Voltage

EXT NMOS;R<sub>LOAD</sub> = 250Ω;T<sub>A</sub> = 25°C;EXT R<sub>SET</sub>;EXT V<sub>REF</sub>;3.8 mA TO 21 mA Range

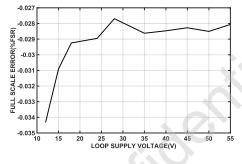

Figure 18. Full-Scale Error vs. Loop Supply Voltage

EXT NMOS;R<sub>LOAD</sub> = 250Ω;T<sub>A</sub> = 25°C;EXT R<sub>SET</sub>;EXT V<sub>REF</sub>;3.8 mA TO 21 mA Range

Figure 19. Load Resistance Load Line vs. Loop Supply Voltage (Voltage Between LOOP- and REG<sub>IN</sub>)

$T_A = 25^{\circ}C; I_{LOOP} = 24 \text{ mA;EXT } V_{REF}; EXT R_{SET}$

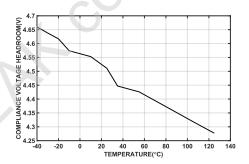

Figure 20. Compliance Voltage Headroom vs.

Temperature

$R_{LOAD} = 250 \Omega; T_A = 25^{\circ}C; I_{LOOP} = 24mA; EXT V_{REF}$

Figure 21. Loop Current Error vs. REGOUT Load Current

•  $V_{LOOP}$  = 24V;EXT NMOS;R<sub>LOAD</sub> = 250  $\Omega$ ;T<sub>A</sub> = 25°C;I<sub>LOOP</sub> = 20mA;EXT V<sub>REF</sub>

Figure 22. Loop Current Noise, 0.1 Hz to 10 Hz

Bandwidth

$V_{LOOP}$  = 24 V;EXT NMOS;EXT  $V_{REF}$ ; $T_A$  = 25°C ; $I_{LOOP}$  = 4 mA

www.3peak.com 22 / 48 BA20240601A0

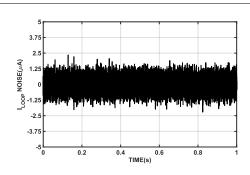

Figure 23. Loop Current Noise, 100 Hz to 10 kHz

Bandwidth

•  $V_{LOOP} = 24 \text{ V;EXT NMOS;EXT } V_{REF}; I_{LOOP} = 4 \text{ mA;} T_A = 25^{\circ}\text{C}$

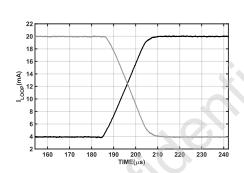

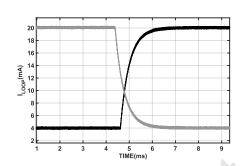

Figure 24. Full-Scale Loop Current Step

•  $V_{LOOP}$  = 24V;EXT NMOS; $R_{LOAD}$  = 250  $\Omega$ ; $T_A$  = 25°C; $C_{IN}$  = OPEN CIRCUIT

Figure 25. Full-Scale Loop Current Step, C<sub>IN</sub> = 22 nF

•  $V_{LOOP}$  = 24V;EXT NMOS;R<sub>LOAD</sub> = 250  $\Omega$ ;T<sub>A</sub> = 25°C;C<sub>IN</sub> = 22 nF

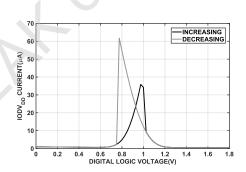

Figure 26. IODV<sub>DD</sub> Current vs. Digital Logic Voltage, Increasing and Decreasing, IODV<sub>DD</sub> = 1.8 V

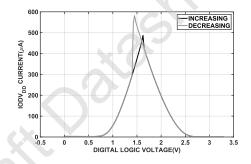

Figure 27. IODV<sub>DD</sub> Current vs. Digital Logic Voltage, Increasing and Decreasing, IODV<sub>DD</sub> = 3.3 V

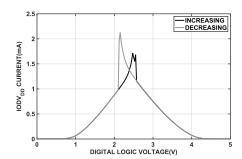

Figure 28. IODV<sub>DD</sub> Current vs. Digital Logic Voltage, Increasing and Decreasing, IODV<sub>DD</sub> = 5 V

www.3peak.com 23 / 48 BA20240601A0

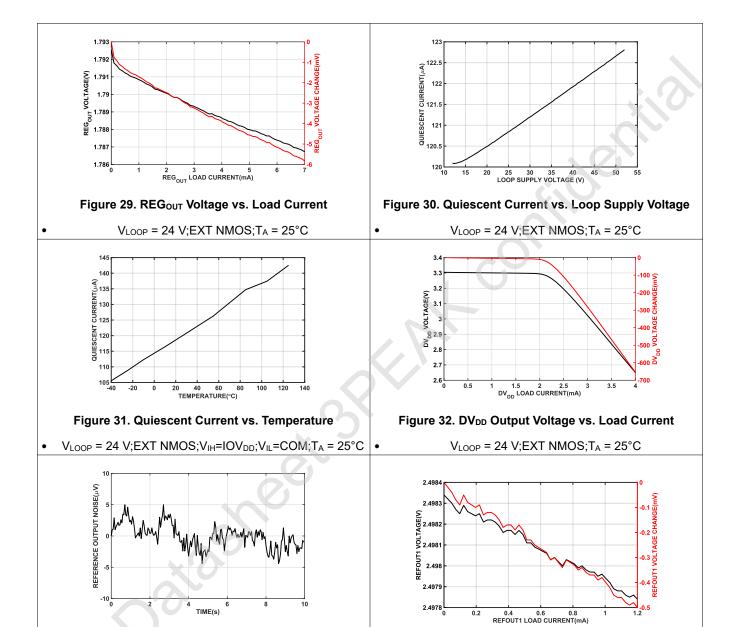

Figure 33. REFOUT1 Voltage Noise, 0.1 Hz to 10 Hz

**Bandwidth**

VLOOP = 24 V;EXT NMOS;TA = 25°C

## 16-Bit, Serial Input, Loop-Powered, 4 mA to 20 mA DAC

Figure 34. REFOUT1 Voltage vs. Load Current

V<sub>LOOP</sub> = 24 V;EXT NMOS;T<sub>A</sub> = 25°C

$V_{LOOP}$  = 24 V;EXT NMOS;; $T_A$  = 25°C; $R_{LOAD}$  = 250  $\Omega$ ; $I_{LOOP}$  = 3.2 mA

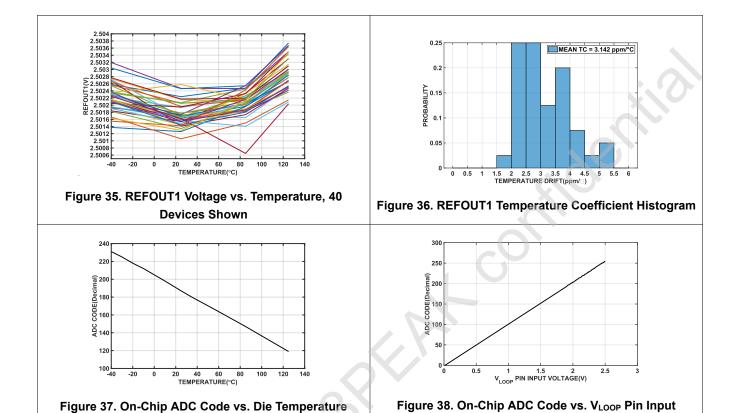

# 16-Bit, Serial Input, Loop-Powered, 4 mA to 20 mA DAC

Voltage

$V_{LOOP} = 24 V;EXT NMOS;;T_A = 25°C$

#### **TERMINOLOGY**

#### **Total Unadjusted Error**

Total unadjusted error (TUE) is a measure of the total output error. TUE consists of INL error, offset error, gain error, and output drift over temperature, in the case of maximum TUE. TUE is expressed in % FSR.

#### Relative Accuracy or Integral Nonlinearity (INL) Error

Relative accuracy, or integral nonlinearity (INL) error, is a measure of the maximum deviation in the output current from a straight line passing through the endpoints of the transfer function. INL error is expressed in % FSR.

#### **Differential Nonlinearity (DNL) Error**

Differential nonlinearity (DNL) error is the difference between the measured change and the ideal 1 LSB change between any two adjacent codes. A specified differential nonlinearity of ±1 LSB maximum ensures monotonicity.

#### **Offset Error**

Offset error is a measure of the output error when zero code is loaded to the DAC register and is expressed in % FSR

#### Offset Error Temperature Coefficient (TC)

Offset error TC is a measure of the change in offset error with changes in temperature and is expressed in ppm FSR/°C.

#### **Gain Error**

Gain error is a measure of the span error of the DAC. It is the deviation in slope of the DAC transfer function from the ideal and is expressed in % FSR.

### **Gain Error Temperature Coefficient (TC)**

Gain error TC is a measure of the change in gain error with changes in temperature and is expressed in ppm FSR/°C.

#### **Full-Scale Error**

Full-scale error is a measure of the output error when full-scale code is loaded to the DAC register and is expressed in % FSR.

#### **Full-Scale Error Temperature Coefficient (TC)**

Full-scale error TC is a measure of the change in full-scale error with changes in temperature and is expressed in ppm FSR/°C.

### **Loop Compliance Voltage Headroom**

Loop compliance voltage headroom is the minimum voltage between the LOOP- and REGIN pins for which the output current is equal to the programmed value

#### **Output Temperature Coefficient (TC)**

Output TC is a measure of the change in the output current at 12 mA with changes in temperature and is expressed in ppm FSR/°C.

#### Voltage Reference Thermal Hysteresis

Voltage reference thermal hysteresis is the difference in output voltage measured at +25°C compared to the output voltage measured at +25°C after cycling the temperature from +25°C to -40°C to +125°C and back to +25°C. The hysteresis is specified for the first and second temperature cycles and is expressed in mV.

#### **Voltage Reference Temperature Coefficient (TC)**

www.3peak.com 26 / 48 BA20240601A0

Voltage reference TC is a measure of the change in the reference output voltage with a change in temperature. The voltage reference TC is calculated using the box method, which defines the TC as the maximum change in the reference output voltage over a given temperature range. Voltage reference TC is expressed in ppm/°C as follows:

$$TC = \frac{(V_{REF\_MAX} - V_{REF\_MIN})}{(V_{REF\_NOM} \times Temp\_Range)} \times 10^{6}$$

(1)

where:V<sub>REF MAX</sub> is the maximum reference output voltage measured over the total temperature range.

V<sub>REF MIN</sub> is the minimum reference output voltage measured over the total temperature range.

V<sub>REF\_NOM</sub> is the nominal reference output voltage, 2.5 V

Temp\_Range is the specified temperature range (-40°C to +125°C)

www.3peak.com 27 / 48 BA20240601A0

### **Detailed Description**

#### Overview

The TPC2221 is a fully integrated, loop-powered digital-to-analog converter (DAC) specifically designed to meet the needs of intelligent sensor manufacturers in the industrial automation field.

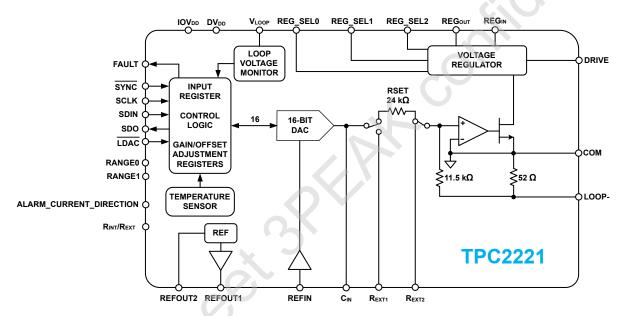

### **Functional Block Diagram**

Figure 39. Functional Block Diagram

### **Feature Description**

### **Functional Modes**

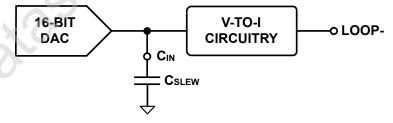

### THEORY OF OPERATION

The TPC2221 is an advanced integrated solution specifically engineered for loop-powered, 4 mA to 20 mA smart transmitter applications. Within a single chip, the TPC2221 integrates a 16-bit DAC and current amplifier for precise digital control of loop current, a voltage regulator to supply power to the entire transmitter, a stable voltage reference, fault alert functions, a versatile SPI-compatible serial interface, gain and offset adjustment registers, and additional features. The detailed characteristics of the TPC2221 are elaborated in the subsequent sections.

#### **FAULT ALERTS**

The TPC2221 incorporates several fault alert mechanisms designed to signal the controller via the FAULT pin and the fault register. In the event of communication loss between the TPC2221 and the microcontroller (SPI fault), the TPC2221 will set the loop current to an alarm value. Upon detecting the FAULT pin being set high, the controller must read the fault register to identify the specific cause of the fault. It is important to note that the watchdog timer does not reset or restart while an alarm is active. If auto fault readback is disabled and an SPI fault occurs, causing the watchdog timer to time out, the timer will

www.3peak.com 28 / 48 BA20240601A0

remain inactive until the status register is manually read by the user. Following this manual readback, the watchdog timer will resume its operation.

#### **SPI FAULT**

The SPI fault is triggered when valid communication with any register of the TPC2221 is not established for a duration exceeding a user-specified interval. Users have the ability to set this interval using the SPI watchdog timeout bits within the control register. The SPI fault bit in the fault register signals any issues on the SPI bus. As this fault results from a communication interruption between the controller and the TPC2221, the loop current is consequently driven to an alarm value. The direction of the alarm current, whether it increases or decreases, is determined by the ALARM\_CURRENT\_DIRECTION pin. Attaching this pin to  $DV_{DD}$  results in an increasing alarm current (22.8 mA/24 mA), while connecting it to COM results in a decreasing alarm current (3.2 mA).

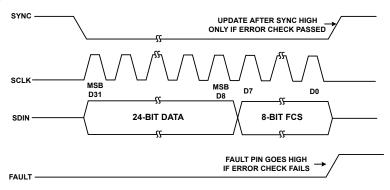

#### **Packet Error Checking**

For ensuring data integrity in noisy conditions, the TPC2221 provides an 8-bit cyclic redundancy check (CRC)-based error detection feature. This is activated by sending a 32-bit serial frame to the TPC2221, with the last eight bits designated as the frame check sequence (FCS). The controlling device must calculate the 8-bit FCS using the specified polynomial to implement packet error checking (PEC):

$$C(x) = X^8 + X^2 + X + 1 \tag{2}$$

The 8-bit FCS is appended to the end of the data-word, and 32 data bits are sent to the TPC2221 before s is taken high. If the check is valid, the data is accepted. If the check fails, the FAULT pin is asserted and the PEC bit of the fault register is set.

24-BIT DATA TRANSFER—NO ERROR CHECKING

32-BIT DATA TRANSFER WITH ERROR CHECKING

Figure 40. PEC Timing

www.3peak.com 29 / 48 BA20240601A0

#### **Current Loop Fault**

The  $I_{\text{LOOP}}$  fault is triggered when the actual loop current deviates from the set loop current by more than  $\pm 0.01\%$  of the full-scale range (FSR). The fault register's  $I_{\text{LOOP}}$  Under bit is activated if the detected loop current is lower than the programmed value, while the  $I_{\text{LOOP}}$  Over bit is activated if the detected loop current exceeds the programmed value. In both scenarios, the FAULT pin is driven to a high logic level. An  $I_{\text{LOOP}}$  Over fault is indicated when the load current supplied by the TPC2221 (through REGout, REFOUT1, REFOUT2, or DVDD) surpasses the programmed loop current. Conversely, an  $I_{\text{LOOP}}$  Under fault is indicated when there is not enough compliance voltage to maintain the programmed loop current, typically due to an excessive load resistance or a low loop supply voltage.

#### **Overtemperature Fault**

The fault register contains two overtemperature alert flags: Temp 100°C and Temp 140°C. Whenever the die temperature of the TPC2221 surpasses the thresholds of 100°C or 140°C, the corresponding flag is activated. In the event that the Temp 140°C flag is triggered in the fault register, the FAULT pin is driven to a high logic state.

#### **Loop Voltage Fault**

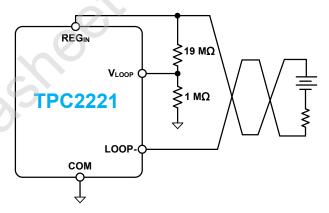

The fault register includes two loop voltage alert flags:  $V_{LOOP}$  12 V and  $V_{LOOP}$  6 V. The  $V_{LOOP}$  12 V flag is activated if the voltage across the  $V_{LOOP}$  and COM pins drops below 0.6 V, which is indicative of a 12 V loop supply voltage, and it resets when the voltage rises above 0.7 V. In a similar fashion, the  $V_{LOOP}$  6 V flag is triggered if the voltage between the  $V_{LOOP}$  and COM pins falls below 0.3 V, corresponding to a 6 V loop supply, and it resets when the voltage exceeds 0.4 V. If the  $V_{LOOP}$  6V flag is triggered in the fault register, the FAULT pin is driven to a high logic level. **Figure 7** depicts how a voltage divider can be used to monitor the loop supply with the  $V_{LOOP}$  input. The suggested voltage divider is composed of a 1 M $\Omega$  and a 19 M $\Omega$  resistor, creating a 20:1 ratio that enables the 2.5 V input range of the  $V_{LOOP}$  pin to oversee loop supplies up to 50 V. With this 20:1 ratio, the predefined  $V_{LOOP}$  6V and  $V_{LOOP}$  12 V alert flags in the fault register trigger loop supply faults at their designated voltages. If a different divider ratio is implemented, the fault flags will generate faults at voltages that are not precisely 6 V and 12 V.

Figure 41. Resistor Divider Connection at VLOOPPin

#### **EXTERNAL CURRENT SETTING RESISTOR**

As depicted in **Figure 1**, the 24 k $\Omega$  resistor R<sub>SET</sub> transforms the DAC output voltage into a current, which is subsequently amplified by a factor of 221 and directed to the LOOP- pin. The temperature stability of the loop current is contingent upon the temperature coefficient of R<sub>SET</sub>.Electrical Characteristics detail the performance characteristics of the TPC2221 when utilizing both the internal R<sub>SET</sub> resistor and an external 24 k $\Omega$  RSET resistor. Employing the internal R<sub>SET</sub> resistor results in an unadjusted total error of less than **0.126% FSR**. Utilizing an external resistor enhances performance to **0.07% FSR**. This specification is predicated on the assumption of an ideal resistor; the actual performance is subject to the absolute value and temperature coefficient of the resistor employed. For further details, refer to the section on**Determining the Expected Total Error**.

www.3peak.com 30 / 48 BA20240601A0

3.2 mA to 24 mA 3.8 mA to 21 mA

## 16-Bit, Serial Input, Loop-Powered, 4 mA to 20 mA DAC

#### LOOP CURRENT RANGE SELECTION

To select the loop current range, connect the RANGE0 and RANGE1 pins to the COM and DVDD pins, as shown in Table 4.

| RANGE1 Pin | RANGE0 Pin | Loop Current Range |

|------------|------------|--------------------|

| COM        | СОМ        | 4 mA to 20 mA      |

| COM        | $DV_DD$    | 3.8 mA to 21 mA    |

**Table 4. Selecting the Loop Current Range**

#### **CONNECTION TO LOOP POWER SUPPLY**

$\mathsf{DV}_\mathsf{DD}$

$\mathsf{DV}_{\mathsf{DD}}$

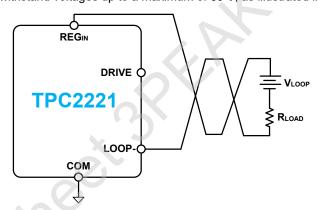

The TPC2221 derives its power from a 4 mA to 20 mA current loop, which is commonly sourced from a power supply situated at a distance from the transmitter unit and typically operates at 24 V. The TPC2221 is capable of being connected directly to this loop power supply and can withstand voltages up to a maximum of **60 V**, as illustrated in **Figure 42**.

COM

$\mathsf{DV}_{\mathsf{DD}}$

Figure 42. Direct Connection of the TPC2221 to Loop Power Supply

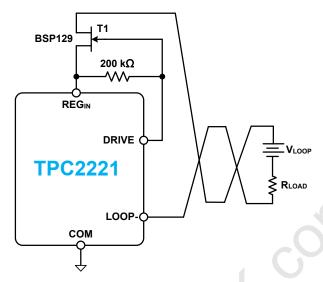

**Figure 42** illustrates the direct connection of the TPC2221 to the loop power supply. **Figure 43**, on the other hand, presents an alternative power connection scheme that incorporates a depletion mode N-channel MOSFET bridging the TPC2221 and the loop power supply. This setup maintains the voltage drop across the TPC2221 around 12 V, thereby capping the maximum on-chip power dissipation at 288 mW (12 V  $\times$  24 mA = 288 mW). In contrast, if the TPC2221 is connected directly to the loop supply as depicted in Figure 43, the maximum on-chip power dissipation for a 24 V loop power supply would be 576 mW (24 V  $\times$  24 mA = 576 mW). It's important to note that the power dissipation varies directly with the loop power supply voltage.

www.3peak.com 31 / 48 BA20240601A0

Figure 43. MOSFET Connecting the TPC2221 to Loop Power Supply

To achieve significant reductions in the rate of change, very large capacitor values are required, which may not be suitable in some applications. In this case, the digital slew rate control feature can be used. The capacitors can be used in conjunction with the digital slew rate control feature as a means of smoothing out the steps caused by the digital code increments, as shown in following figure.

#### **ON-CHIP ADC**