## Features

- High accuraccy

- INL: typical ±1LSB at 16-bit Resolution

- Integrated 2.5V Internal Reference

- Low Drift: 5ppm/°C

- Flexible output configuration

- User selectable Gain: 1/2, 1, 2

- Reset to Zero Scale or Midscale

- High output current capability: 20mA

- Serial Interfaces

- 4 Wire SPI Compatible Serial Interface

- Daisy Chain Operation

- CRC Error Check

- Temperature Range: -40°C to +125°C

- Package: QFN 3X3-16, WLCSP 2.4X2.4-16

# Applications

- Industrial automation

- Optical networking

- Data Acquisition Systems

## Description

The TPC219 is faimily of high accuracy DACs with 16, 14 and 12bit resolution which are all pin-compatible.

The device includes a 2.5V internal reference, which can be used to reduce system complexity

Several gain options could be selected to provide different full scale output voltages, 1.25V, 2.5V and 5V.

The device operates under a single analog supply, and has seperate VIO supply for digital communication. The communication is performed through a serial interface, and can operate under wide range VIO supply voltage.

A power on reset circuit is intergraged to maintain the DAC output at zero scale or midscale.

The device is characterized for temeprature range of -40°C to 125 °C. And is available in small package of QFN and WLCSP.

# **Typical Application Circuit**

## **Table of Contents**

| Features                                | 1  |

|-----------------------------------------|----|

| Applications                            | 1  |

| Description                             | 1  |

| Typical Application Circuit             | 1  |

| Product Family Table                    |    |

| Revision History                        | 3  |

| Pin Configuration and Functions         | 4  |

| Specifications                          | 6  |

| Absolute Maximum Ratings <sup>(1)</sup> | 6  |

| ESD, Electrostatic Discharge Protection | 6  |

| Recommended Operating Conditions        | 6  |

| Thermal Information                     | 7  |

| Electrical Characteristics              | 8  |

| Timing Requirements                     | 12 |

| Timing Diagrams                         | 12 |

| Typical Performance Characteristics     | 14 |

| Detailed Description                    | 16 |

| Overview                                | 16 |

| Functional Block Diagram                | 16 |

| Feature Description                     | 16 |

| Functional Modes                        | 17 |

| Serial Interface                        | 19 |

| Register Table                          | 19 |

| Application and Implementation          | 24 |

| Application Information                 | 24 |

| Typical Application                     | 24 |

| Layout                                  | 25 |

| Layout Guideline                        | 25 |

| Tape and Reel Information               | 26 |

| Package Outline Dimensions              | 27 |

| QFN3X3-16                               | 27 |

| WLCSP                                   | 28 |

| Order Information                       | 29 |

# Product Family Table

| Order Number        | Resolution | Reference         | RESET   | SDO or CLR<br>Operation | Package         |

|---------------------|------------|-------------------|---------|-------------------------|-----------------|

| TPC2190-QFNR        | 16         | Internal/External | 0       | SDO                     | QFN3X3-16       |

| TPC2190-WLPR        | 16         | Internal/External | 0       | SDO                     | WLCSP2.4X2.4-16 |

| TPC2190M-QFNR       | 16         | Internal/External | Midscal | SDO                     | QFN3X3-16       |

| TPC2192-QFNR<br>(1) | 12         | Internal/External | 0       | SDO                     | QFN3X3-16       |

| TPC2192-WLPR        | 12         | Internal/External | 0       | SDO                     | WLCSP2.4X2.4-16 |

#### Note:

(1) Could provide samples in 2 months.

## **Revision History**

| Date     | Revision | Notes             |

|----------|----------|-------------------|

| 2023/6/5 | Rev.A.0  | Released Version. |

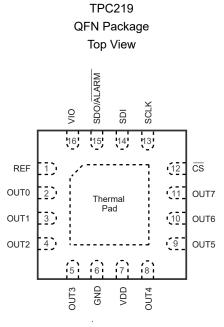

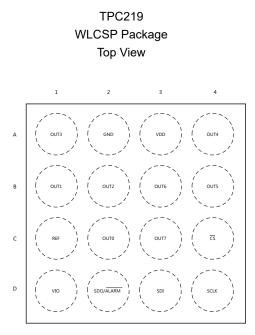

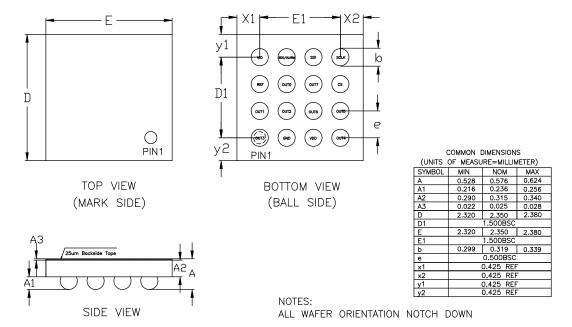

## **Pin Configuration and Functions**

Table 1. Pin Functions

|          | PIN       |           |      | DECODIDITION                                                                                                                                                                                                        |

|----------|-----------|-----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. WQFN | NO. WLCSP | NAME      | TYPE | DESCRIPTION                                                                                                                                                                                                         |

| 1        | C1        | REF       | I/O  | Reference output pin(default). Can be used as reference inpput pin when using external reference.                                                                                                                   |

| 2        | C2        | OUT0      | 0    | DAC channel 0 output.                                                                                                                                                                                               |

| 3        | B1        | OUT1      | 0    | DAC channel 1 output.                                                                                                                                                                                               |

| 4        | B2        | OUT2      | 0    | DAC channel 2 output.                                                                                                                                                                                               |

| 5        | A1        | OUT3      | 0    | DAC channel 3 output.                                                                                                                                                                                               |

| 6        | A2        | GND       | GND  | Ground pin.                                                                                                                                                                                                         |

| 7        | A3        | VDD       | PWR  | Analog supply pin.                                                                                                                                                                                                  |

| 8        | A4        | OUT4      | 0    | DAC channel 4 output.                                                                                                                                                                                               |

| 9        | B4        | OUT5      | 0    | DAC channel 5 output.                                                                                                                                                                                               |

| 10       | B3        | OUT6      | 0    | DAC channel 6 output.                                                                                                                                                                                               |

| 11       | C3        | OUT7      | 0    | DAC channel 7 output.                                                                                                                                                                                               |

| 12       | C4        | CS        | I    | Frame synchronization signal for SPI interface.                                                                                                                                                                     |

| 13       | D4        | SCLK      | I    | Clock input for SPI interface.                                                                                                                                                                                      |

| 14       | D3        | SDI       | I    | Data input for SPI interface.                                                                                                                                                                                       |

| 15       | D2        | SDO/ALARM | 0    | TPC216X: Data output for SPI interface. It is in high<br>impedance when /CS is high. And the pin can also be<br>configured as /Alarm pin, which is open-drain output to<br>indicate a CRC or reference alarm event. |

|          | PIN       |             |      | DESCRIPTION                                                                                                                                                |  |

|----------|-----------|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO. WQFN | NO. WLCSP | NAME        | TYPE | DESCRIPTION                                                                                                                                                |  |

|          |           | LR          | I    | TPC216XC: A low value on /CLR pin clears DAC registers<br>and output to the reset value. A high value on /CLR pin<br>causes the device to exit clear mode. |  |

| 16       | D1        | VIO         | PWR  | IO supply pin.                                                                                                                                             |  |

| -        | -         | Thermal Pad | -    | Thermal pad should be connected to PCB ground plane.                                                                                                       |  |

# **Specifications**

### Absolute Maximum Ratings <sup>(1)</sup>

|                |                                               | MIN  | MAX       | UNIT |

|----------------|-----------------------------------------------|------|-----------|------|

| Supply Voltage | VDD to GND                                    | -0.3 | 6         | V    |

| Supply Voltage | VIO to GND                                    | -0.3 | 6         | V    |

|                | DAC outputs to GND                            | -0.3 | VDD + 0.3 | V    |

| Pin voltage    | REF to GND                                    | -0.3 | VDD + 0.3 | V    |

|                | Digital pins to GND                           | -0.3 | VIO + 0.3 | V    |

| Input current  | Input current to any pin<br>excep supply pins | -10  | 10        | mA   |

|                | Junction, TJ                                  | -40  | 150       | °C   |

| Temperature    | Storage, Tstg                                 | -60  | 150       | C°   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

### ESD, Electrostatic Discharge Protection

| Symbol | Parameter                | Condition                             | Minimum Level | Unit |

|--------|--------------------------|---------------------------------------|---------------|------|

| HBM    | Human Body Model ESD     | ANSI/ESDA/JEDEC JS-001 (1)            | 4             | kV   |

| CDM    | Charged Device Model ESD | ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | 1.5           | kV   |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **Recommended Operating Conditions**

|                          |                               | MIN | NOM | MAX         | UNIT |

|--------------------------|-------------------------------|-----|-----|-------------|------|

| VDD                      | Analog supply<br>voltage      | 2.7 |     | 5.5         | V    |

| VIO                      | Digital IO supply<br>voltage  | 1.7 |     | 5.5         | V    |

| Digital input<br>voltage | Digital input<br>voltage      | 0   |     | VIO         | V    |

|                          | Reference divider<br>disabled | 1.2 |     | (VDD-0.2)/2 | V    |

| VREFIN                   | Reference divider<br>enabled  | 2.4 |     | VDD-0.2     | V    |

|                          | Reference divider<br>disabled | 1.2 |     | VDD/2       | V    |

|    |                                | MIN | NOM | MAX | UNIT |

|----|--------------------------------|-----|-----|-----|------|

|    | Reference divider<br>enabled   | 2.4 |     | VDD | V    |

| TJ | Operating Junction temperature | -40 |     | 125 | °C   |

### Thermal Information

| Package Type | θ <sub>JA</sub> | θյς  | Unit |

|--------------|-----------------|------|------|

| QFN3X3-16    | 33              | 29.5 | °C/W |

| WLCSP        | 68              | 0.3  | °C/W |

### **Electrical Characteristics**

all minimum/maximum specifications at V DD =2.7 to 5.5V, VIO =1.7 to 5.5V ,  $V_{REFIN}$  =1.25 to 5.5V,  $R_{LOAD}$ =2k $\Omega$  to GND,  $C_{LOAD}$ =200pF to GND, digital inputs at  $V_{IO}$  or GND,  $T_{J}$  = -40°C to +125°C and all typical specifications at  $T_{J}J$  = 25°C.

|                         | PARAMETER                          | TEST CONDITIONS                           | MIN        | ТҮР        | MAX            | UNIT             |

|-------------------------|------------------------------------|-------------------------------------------|------------|------------|----------------|------------------|

| STATIC PERFORM          | MANCE                              | 1                                         | 1          | 1          | 4              |                  |

| -                       | nance specified with DAC output    | s unloaded for all gain options, ເ        | unless oth | erwise not | ed. End po     | int fit          |

| between codes. 16       | 6-bit: Code 256 to 65280           |                                           |            |            |                |                  |

| Resolution              |                                    |                                           | 16         |            |                | Bits             |

| DNL (TPC2190)           | Differential nonlinearity          |                                           | -1         | ±0.5       | 1.5            | LSB              |

| DNL (TPC2192)           | Differential nonlinearity          |                                           | -1         | ±0.5       | 1              | LSB              |

| IN II. (TE 00 ( 00)     | Integral nonlinearity              | V <sub>DD</sub> 3.3~5.5V                  | -2.5       | ±0.5       | 2.5            | LSB              |

| INL (TPC2190)           | Integral nonlinearity              | V <sub>DD</sub> 2.7~3.3V                  | -3.5       | ±0.5       | 3.5            | LSB              |

| INL (TPC2192)           | Integral nonlinearity              |                                           | -1         | ±0.5       | 1              | LSB              |

| TUE                     | Total unadjusted error             | REF-DIV=0                                 |            | ±0.05      | ±0.2           | %FSR             |

|                         |                                    | REF-DIV=1                                 |            | ±0.05      | ±0.3           | %FSR             |

| OE                      | Offset error                       | All Gians                                 |            | ±0.75      | ±2.5           | mV               |

|                         | Offset error temperature drift     |                                           |            | ±1.5       |                | uV/°C            |

| GE                      | Gain error                         | REF-DIV=0                                 |            | ±0.05      | ±0.1           | %FSR             |

|                         |                                    | REF-DIV=1                                 |            | ±0.05      | ±0.2           | %FSR             |

|                         | Gain error temperature drift       |                                           |            | ±1.2       |                | ppm of<br>FSR/°C |

| ZSE                     | Zero-scale error                   | DAC code = zero scale                     |            | 0.5        | 2.5            | mV               |

|                         | Zero-scale error temperature drift |                                           |            | ±1.5       |                | uV/°C            |

| FSE                     | Full-scale error                   | REF-DIV=0                                 |            | ±0.05      | ±0.15          | %FSR             |

|                         |                                    | REF-DIV=1                                 |            | ±0.05      | ±0.25          | %FSR             |

|                         | Full-scale error temperature drift |                                           |            | ±2         |                | ppm of<br>FSR/°C |

| OUTPUT CHARAG           | CTERISTICS                         | 1                                         |            | 1          |                |                  |

|                         |                                    | Gain = 2 (BUFF-GAIN = 1,<br>REF-DIV = 0)  | 0          |            | 2 x V<br>REF   | V                |

| Voltage range           |                                    | Gain = 1 (BUFF-GAIN = 1,<br>REF-DIV = 1)  | 0          |            | V<br>REF       | v                |

|                         |                                    | Gain =1/2 (BUFF-GAIN = 0,<br>REF-DIV = 1) | 0          |            | 1/2 x V<br>REF | V                |

|                         |                                    | to GND or VDD (unloaded)                  |            | 0.004      |                | V                |

| Output voltage headroom |                                    | to GND or VDD (-10 mA ≤<br>IOUT ≤ 10 mA)  | 0.3        |            |                | V                |

| P                           | ARAMETER                     | TEST CONDITIONS                                                  | MIN | ТҮР   | MAX | UNIT   |

|-----------------------------|------------------------------|------------------------------------------------------------------|-----|-------|-----|--------|

| Short circuit current       |                              | DAC code = full scale. Output<br>shorted to GND                  |     | 28    |     | mA     |

| (1)                         |                              | DAC code = zero scale.<br>Output shorted to VDD                  |     | 25    |     | mA     |

| C                           | Capacitive load stability    | RLOAD=∞                                                          | 0   |       | 2   |        |

| CL                          | (2)                          | RLOAD=2kΩ                                                        | 0   |       | 10  | nF     |

| RL                          | Clamp resistance             |                                                                  |     | 1     |     | kΩ     |

| Load regulation             |                              | DAC code = midscale, -10<br>mA <= IOUT<= 10 mA                   |     | 85    |     | μV/mA  |

| DC output impedance         |                              | DAC code = midscale                                              |     | 0.085 |     | Ω      |

| DYNAMIC PERFOR              | RMANCE                       |                                                                  |     |       |     |        |

|                             |                              | 1/4 to 3/4 scale and 3/4 to<br>1/4 scale settling to ±2 LSB<br>V |     |       |     |        |

| Tst Output voltage settling | Output voltage settling time | DD<br>=5.5V,V<br>REFIN                                           |     | 6     |     | μs     |

|                             |                              | =2.5V,GAIN=2                                                     |     |       |     |        |

|                             |                              | -2.3V,GAIN-2                                                     |     |       |     |        |

|                             |                              | DD                                                               |     |       |     |        |

|                             | Slew rate                    | =5.5V,V                                                          |     | 0.8   |     | V/µs   |

|                             |                              | REFIN                                                            |     |       |     |        |

|                             |                              | =2.5V,GAIN=2 , 10% to 90%                                        |     |       |     |        |

|                             |                              | 0.1 Hz to 10 Hz, midscale<br>code,V                              |     |       |     |        |

| Vn                          | Output noise                 | DD<br>=5.5V,V                                                    |     | 17    |     | μVpp   |

|                             |                              | REFIN                                                            |     |       |     |        |

|                             |                              | =2.5V,GAIN=2                                                     |     |       |     |        |

| Output noise density        |                              | 1kHz, midscale code,V                                            |     |       |     |        |

|                             |                              | DD                                                               |     |       |     |        |

|                             |                              | =5.5V,V                                                          |     | 85    |     |        |

|                             |                              | REFIN                                                            |     |       |     | nV/√Hz |

|                             |                              | =2.5V,GAIN=2                                                     |     |       |     |        |

|                             |                              | 10kHz, midscale code,V                                           |     |       |     |        |

|                             |                              | DD                                                               |     | 64    |     |        |

|                             |                              | =5.5V,V                                                          |     |       |     |        |

|        | PARAMETER                   | TEST CONDITIONS                                        | MIN | ТҮР  | MAX | UNIT |

|--------|-----------------------------|--------------------------------------------------------|-----|------|-----|------|

|        |                             | REFIN                                                  |     |      |     |      |

|        |                             | =2.5V,GAIN=2                                           |     |      |     |      |

|        |                             | 1kHz, midscale code,V                                  |     |      |     |      |

|        |                             | DD                                                     |     |      |     |      |

|        |                             | =5.5V,V                                                |     | 50   |     |      |

|        |                             | REFIN                                                  |     |      |     |      |

|        |                             | =2.5V,GAIN=1                                           |     |      |     |      |

|        |                             | 10kHz, midscale code,V                                 |     |      |     | -    |

|        |                             | DD                                                     |     |      |     |      |

|        |                             | =5.5V,V                                                |     | 50   |     |      |

|        |                             | REFIN                                                  |     |      |     |      |

|        |                             | =2.5V,GAIN=1                                           |     |      |     |      |

|        |                             | Midscale code, frequency                               |     |      |     |      |

|        |                             | =60 Hz,                                                |     |      |     |      |

| PSRRac | AC PSRR                     | amplitude = 200 mVPP                                   |     | 76   |     | dB   |

|        |                             | superimposed on V                                      |     |      |     |      |

|        |                             | DD                                                     |     |      |     |      |

| PSRRdc | DC PSRR                     | Midscale code,VDD=                                     |     | 20   |     | uV/V |

|        |                             | 5V±10%                                                 |     |      |     |      |

|        | Code change glitch impulse  | 1 LSB change around major<br>carrier                   |     | 2.5  |     | nV-s |

|        |                             | DACx-PWDWN 1 to 0                                      |     |      |     |      |

|        |                             | transition. DAC code = full                            |     |      |     |      |

|        | Power-up time               | scale. VDD = 5.5 V, VREFIN                             |     | 14.2 |     | μs   |

|        |                             | = 2.5 V, Gain = 2                                      |     |      |     |      |

|        |                             | (3)                                                    |     |      |     |      |

|        |                             | DAC code = zero scale. VDD                             |     |      |     |      |

|        | Power-down glitch amplitude | = 5.5 V, VREFIN = 2.5 V,                               |     | 25   |     | mV   |

|        |                             | Gain = 2. CLOAD = 50 pF<br>1/4 to 3/4 scale and 3/4 to |     |      |     |      |

|        |                             | 1/4 to 3/4 scale and 3/4 to<br>1/4 scale               |     |      |     |      |

|        | Overshot/Downshot           | VDD=5.5V,VREFIN=2.5V,GAI                               |     |      |     |      |

|        |                             | N=2                                                    |     |      |     |      |

|        |                             | Measured DAC output at                                 |     |      |     |      |

|        | Channel-to-channel AC       | midscale, Code 32 to full-                             |     |      |     | nV-s |

|        | crosstalk                   | scale swing on asjacent<br>channel                     |     |      |     |      |

|        |                             | Measured DAC output at                                 |     |      |     |      |

|        | Channel-to-channel DC       | midscale, all other DAC                                |     | 1    |     | μV   |

|        | crosstalk                   | outputs at full-scale, Gain=1                          |     |      |     |      |

|              | PARAMETER                                     | TEST CONDITIONS                                                                                                 | MIN          | TYP | MAX          | UNIT          |

|--------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------|-----|--------------|---------------|

|              |                                               | Measured DAC output at<br>midscale, all other DAC<br>outputs at full-scale, Gain=2                              |              | 10  |              | μV            |

| INTERNAL RE  | FERENCE CHARACTERISTICS                       |                                                                                                                 |              |     |              |               |

| VREFOUT      | Internal referencel voltage                   | TA = 25°C                                                                                                       | 2.494        | 2.5 | 2.506        | V             |

| тс           | Internal reference<br>temperature coefficient | TJ = -40°C to 125°C                                                                                             |              | 8   |              | ppm/°C        |

|              | Internal reference impedance                  |                                                                                                                 |              | 0.1 |              | Ω             |

|              | Internal reference output noise               | 0.1 Hz to 10 Hz                                                                                                 |              | 15  |              | μVPP          |

|              | Internal reference noise density              | 10 kHz, REFLOAD = 10 nF                                                                                         |              | 370 |              | nV/<br>sqrtHz |

|              | Internal reference load current               |                                                                                                                 |              | ±5  |              | mA            |

|              | refierence Load regulation                    | source and sink                                                                                                 |              | 100 |              | uV/mA         |

|              | Internal reference load cap                   | actual capacitance                                                                                              | 300          |     | 2200         | nF            |

| EXTERNAL RI  | EFERENCE CHARACTERISTICS                      |                                                                                                                 |              |     | 1            |               |

|              |                                               | V                                                                                                               |              |     |              |               |

|              | Referencel input current                      | REFIN                                                                                                           |              | 25  |              | uA            |

|              |                                               | =2.5V                                                                                                           |              |     |              |               |

|              | Referencel input impedance                    |                                                                                                                 |              | 100 |              | kΩ            |

|              | Referencel input capacitance                  |                                                                                                                 |              | 5   |              | pF            |

| DIGITAL INPU | T CHARACTERISTICS                             |                                                                                                                 |              |     | 1            | 1             |

| VIH          | High-level input voltage                      |                                                                                                                 | 0.7 ×<br>VIO |     |              | V             |

| VIL          | Low-level input voltage                       |                                                                                                                 |              |     | 0.3 ×<br>VIO | V             |

|              | Input current                                 |                                                                                                                 |              | ±2  |              | μA            |

|              | Input pin capacitance                         |                                                                                                                 |              | 2   |              | pF            |

| DIGITAL OUT  | PUT CHARACTERISTICS                           |                                                                                                                 |              |     |              | _             |

| VOH          | High-level output voltage                     | ILOAD = 0.2 mA                                                                                                  | VIO –<br>0.4 |     |              | V             |

| VOL          | Low-level output voltage                      | ILOAD = 0.2 mA                                                                                                  |              |     | 0.4          | V             |

|              | Output pin capacitance                        |                                                                                                                 |              | 4   |              | pF            |

| POWER CON    | SUMPTION CHARACTERISTICS                      |                                                                                                                 |              |     |              |               |

| IVDD         | VDD supply current                            | Active mode. Internal<br>reference enabled. Gain = 1.<br>DAC code = full scale.<br>Outputs unloaded. SPI static |              | 5   | 6            | mA            |

| P    | ARAMETER           | TEST CONDITIONS                                                                                                  | TEST CONDITIONS MIN |     |     |    |  |

|------|--------------------|------------------------------------------------------------------------------------------------------------------|---------------------|-----|-----|----|--|

|      |                    | Active mode. Internal<br>reference disabled. Gain = 1.<br>DAC code = full scale.<br>Outputs unloaded. SPI static |                     | 4.5 | 5.5 |    |  |

|      |                    | Power-down                                                                                                       |                     | 15  |     |    |  |

| IVIO | VIO supply current |                                                                                                                  |                     | 6.8 | 15  | μA |  |

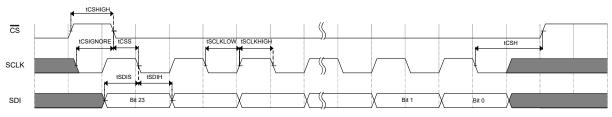

### **Timing Requirements**

all minimum/maximum specifications at V DD =2.7 to 5.5V, VIO =1.7 to 5.5V ,  $V_{REFIN}$  =1.25 to 5.5V,  $R_{LOAD}$ =2k $\Omega$  to GND, $C_{LOAD}$ =200pF to GND,digital inputs at  $V_{IO}$  or GND, $T_{J}$  = -40°C to +125°C and all typical specifications at  $T_{J}J$  = 25°C.

|                       |                         | MIN | NOM | MAX    | UNIT |

|-----------------------|-------------------------|-----|-----|--------|------|

| SPI TIMING REQUIREMEN | TS                      | ·   |     | •<br>• |      |

| f(SCLK)               | SCLK frequency          |     |     | 20     | MHz  |

| t(SCLKHIGH)           | SCLK high time          | 23  |     |        | ns   |

| tSCLKLOW              | SCLK low time           | 23  |     |        | ns   |

| t(SDISU)              | SDI setup time          | 7   |     |        | ns   |

| t(SDIHD)              | SDI hold time           | 7   |     |        | ns   |

| t(SDOTOZ)             | SDO driven to tri-state | 0   |     | 15     | ns   |

| t(SDOTOD)             | SDO tri-state to driven | 0   |     | 18     | ns   |

| t(SDODLY)             | SDO output delay        | 0   |     | 18     | ns   |

| t(CSSU)               | CS setup time           | 10  |     |        | ns   |

| t(CSHD)               | CS hold time            | 20  |     |        | ns   |

| t(CSHIGH)             | CS high time            | 20  |     |        | ns   |

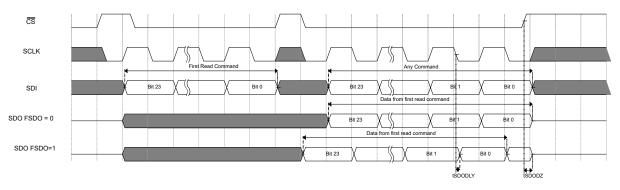

### **Timing Diagrams**

Figure 1. SPI Write Timing Diagram

Figure 2. SPI ReadTiming Diagram

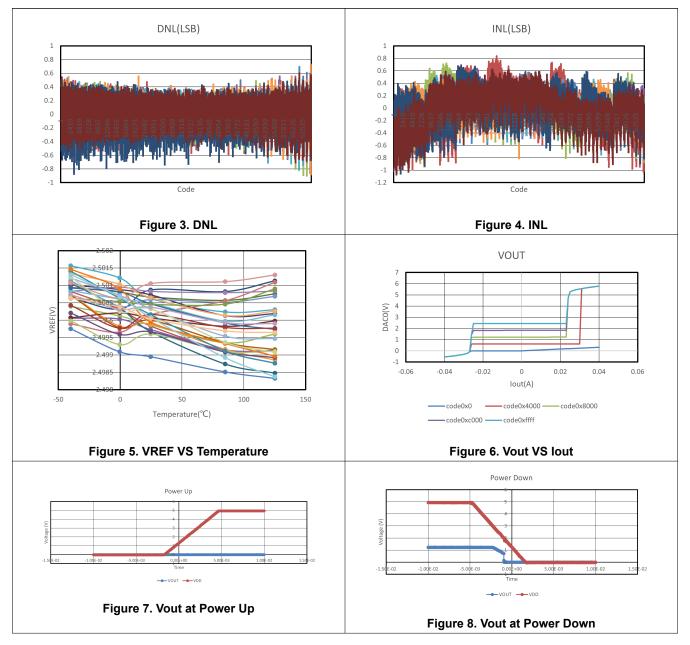

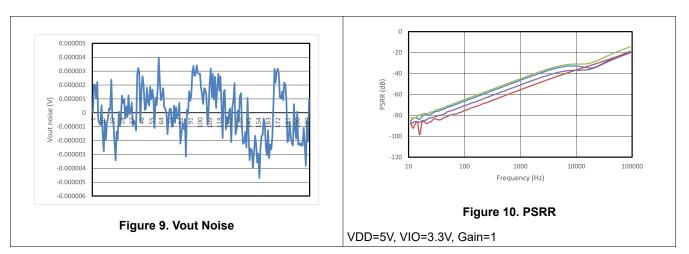

### **Typical Performance Characteristics**

At TA = 25°C, VDD = 5.5 V, Internal Reference = 2.5 V, Gain = 2, DAC outputs unloaded, unless otherwise noted.

## **Detailed Description**

### Overview

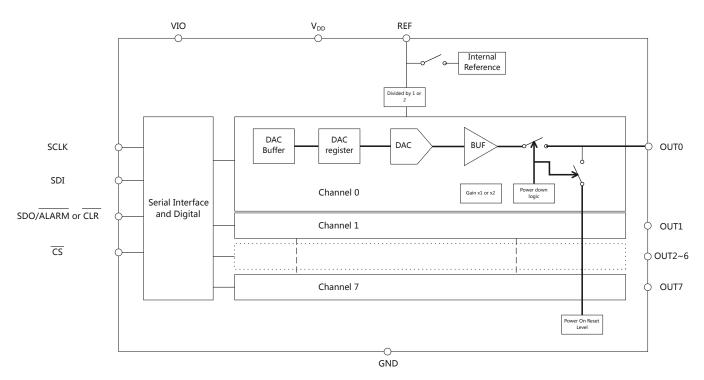

The TPC219X is a pin-compatible family of 8 channel, high accurate, voltage-output digital-to-analog converters (DACs), with 16-, 14- and 12-bit resolution. The devices provide a 2.5 V internal reference. Also output range can be selected to be 1.25 V (gain =  $\frac{1}{2}$ ), 2.5 V (gain = 1) or 5 V(gain = 2).

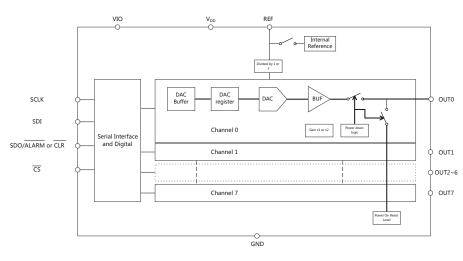

### **Functional Block Diagram**

Figure 11. Functional Block Diagram

### **Feature Description**

#### **DAC transfer function**

The DAC output voltage is given by following equation

$$V_{OUT} = \frac{CODE}{2^n} \times \frac{V_{REF}}{DIV} \times GAIN$$

CODE = decimal value of the binary code in the DAC register.

n: DAC resolution bits.

VREF = DAC reference voltage.

DIV: 1 or 2 as set by REF-DIV bit.

Gain: 1 or 2 as set bu BUFF-GAIN bit.

(1)

#### **DAC Register Structure**

Data written to the DAC data registers is initially stored in the DAC buffer registers. And then transfer of data from the DAC buffer registers to the active DAC registers, can be selected to happen immediately (asynchronous mode) or initiated by an LDAC trigger (synchronous mode). Once the DAC active registers are updated, the DAC outputs change to the new values. When a DAC Data register is read, the value held in the DAC buffer register is returned (not the value in the DAC active register).

The SYNC-EN bit controls the update mode for each DAC channel. In asynchronous mode, writing to the DAC data register results in an immediate update of the DAC active register and DAC output on the CS rising edge. In synchronous mode, writing to the DAC data register does not update the DAC output, but the update happens when an LDAC trigger event is generated through the LDAC bit. The synchronous update mode can update multiple DAC outputs imultaneously.

A DAC broadcast register is proved to simultaneously update multiple DAC outputs with the same value by a single register write. Each DAC channel can be configured to be updated or not by a broadcast command, through the corresponding DAC-BRDCAST-EN bit. A register write to the BRDCAST-DATA register forces selected DAC channels that have been configured for broadcast operation to update their outputs. The DAC ouputs update to the broadcast value on CS rising edge independently of their synchronous mode configuration.

### **CLEAR Operation**

The  $\overline{\text{CLR}}$  pin can update multiple DAC outputs to the clear value simultaneously: zero code or midscale code (for different parts). Channels can be independently configured to update or remain unaffected by the  $\overline{\text{CLR}}$  pin

#### Reference

The device provides a internal 2.5V reference, which is enabled by default after power up. The internal reference is available on the REF pin. And External reference is supported by disabling the enable reference by CONFIG register.

The reference voltage from the internal reference or an external one can be divided by a factor of two by setting the REF-DIV bit.

#### **Reset Options**

After power up, and the  $V_{DD}$  and  $V_{IO}$  supplies have settled, the Power On Reset (POR) function causes all registers to initialize to their default values. And DAC output remains at the power-up voltage.

A software reset is provided by writing the reserved code 0x1010 to SOFT-RESET bits.

### **Functional Modes**

#### Stand Alone Operation

A serial interface access cycle can be initiated by asserting the  $ov\overline{CS}$  pin low.

SDI data are clocked on SCLK falling edges. A regular serial interface access cycle is 24 bits long with error checking disabled and 32 bits long with error checking enabled.

If the access cycle contains more than the minimum clock edges, only the last 24 or 32 bits are used by the device.

#### **Daisy Chain Operation**

For systems that contain more than one devices, the SDO pin can be used to daisy-chain them together. Daisy-chain operation is useful in reducing the number of serial interface lines.

By connecting the SDO output of the first device to the SDI input of the next device in the chain, a multiple-device interface is constructed. Each device in the system requires 24 clock pulses. As a result the total number of clock cycles must be equal to 24 × N, where N is the total number of devices in the daisy chain.

The first falling edge on the CS pin starts the operation cycle. If more than 24 SCLK pulses are applied while the CS pin is kept low, the data ripples out of the shift register and is clocked out on the SDO pin either on the falling edge or rising edge of SCLK according to the FSDO bit.

#### Frame Error Checking

Error checking is provide that can be used to check the integrity of SPI data communication. This feature can be enabled by setting the CRC-EN bit.

The error checking scheme is based on the CRC-8-ATM (HEC) polynomial  $x^8 + x^2 + x + 1$  (that is, 100000111).

When error checking is enabled, the serial interface access cycle width is 32 bits. The normal 24-bit SPI data is appended with an 8-bit CRC polynomial by the host processor before feeding it to the device.

| BIT   | FIELD     | DESCRIPTION                                                                                                                                                                                          |  |  |  |

|-------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 31    | RW        | Identifies the communication as a read<br>or write command to the addressed<br>register. R/W = 0 sets a write operation.<br>R/W = 1 sets a read operation.                                           |  |  |  |

| 30    | CRC-ERROR | Reserved bit. Set to zero.                                                                                                                                                                           |  |  |  |

| 29:28 | Reserved  | Reserved bits. Must be filled with zeros.                                                                                                                                                            |  |  |  |

| 27:24 | A[3:0]    | Register address. Specifies the registe<br>to be accessed during the read or write<br>operation.                                                                                                     |  |  |  |

| 23:8  | DI[15:0]  | Data cycle bits. If a write command,<br>the data cycle bits are the values to<br>be written to the register with address<br>A[3:0]. If a read command, the data<br>cycle bits are don't care values. |  |  |  |

| 7:0   | CRC       | 8-bit CRC polynomial.                                                                                                                                                                                |  |  |  |

#### Table 2. Error Checking Serial Interface Access Cycle

The device decodes the 32-bit access cycle to compute the CRC remainder on CS rising edges. If no error exists, the CRC remainder is zero and data are accepted by the device.

A write operation failing the CRC check causes the data to be ignored by the device. After the write command, a second access cycle can be issued to determine the error checking result (CRC-ERROR bit) on the SDO pin

#### Table 3. Write Operation Error Checking Cycle

| BIT   | FIELD     | DESCRIPTION                                             |

|-------|-----------|---------------------------------------------------------|

| 31    | RW        | Echo RW from previous access cycle (RW = 0).            |

| 30    | CRC-ERROR | Returns a 1 when a CRC error is detected, 0 otherwise.  |

| 29:28 | Reserved  | Echo bits 29:28 from previous access cycle (all zeros). |

| 27:24 | A[3:0]    | Echo address from previous access cycle.                |

| 23:8  | DO[15:0]  | Echo data from previous access cycle.                   |

| BIT | FIELD | DESCRIPTION                        |

|-----|-------|------------------------------------|

| 7:0 | CRC   | Calculated CRC value of bits 31:8. |

A read operation must be followed by a second access cycle to get the requested data on the SDO pin. The error check result (CRC-ERROR bit) from the read command is output on the SDO pin.

#### Table 4. Read Operation Error Checking Cycle

| BIT   | FIELD     | DESCRIPTION                                             |

|-------|-----------|---------------------------------------------------------|

| 31    | RW        | Echo RW from previous access cycle (RW = 1).            |

| 30    | CRC-ERROR | Returns a 1 when a CRC error is detected, 0 otherwise.  |

| 29:28 | Reserved  | Echo bits 29:28 from previous access cycle (all zeros). |

| 27:24 | A[3:0]    | Echo address from previous access cycle.                |

| 23:8  | DO[15:0]  | Readback data requested on previous access cycle.       |

| 7:0   | CRC       | Calculated CRC value of bits 31:8.                      |

#### Power Down Mode

The device's output amplifiers and internal reference can be independently powered down through the CONFIG register. At power-up all output channels and the device internal referece are active by default. A DAC output channel in power-down mode is connected internally to GND through a 1 k $\Omega$  resistor.

### Serial Interface

The TPC219 family supports SPI-compatible interface.

### **Register Table**

| DECIOT       | TV      |              | ADDRE      |         | DATA BITS                              |         |         |         |         |    |    |    |    |          |    |    |    |    |    |

|--------------|---------|--------------|------------|---------|----------------------------------------|---------|---------|---------|---------|----|----|----|----|----------|----|----|----|----|----|

| REGIST<br>ER |         | RESET        | SS<br>BITS | D1<br>5 | D1<br>4                                | D1<br>3 | D1<br>2 | D1<br>1 | D1<br>0 | D9 | D8 | D7 | D6 | D5       | D4 | D3 | D2 | D1 | D0 |

| NOP          | W       | 16'h0000     | 7'h00      |         | NOP                                    |         |         |         |         |    |    |    |    |          |    |    |    |    |    |

| DEVICE<br>ID | R       | -            | 7'h01      |         | DEVICE ID                              |         |         |         |         |    |    |    |    | VEF<br>N | -  |    |    |    |    |

| SYNC         | R/<br>W | 16'hFF0<br>0 | 7'h02      |         | DACx-BRDCAST-EN DACx-SYNC-EN           |         |         |         |         |    |    |    |    |          |    |    |    |    |    |

| CONFIG       | R/<br>W | 16'h0000     | 7'h03      |         | Reserve d La La CR CR CE DO DACX-PWDWN |         |         |         |         |    |    |    |    |          |    |    |    |    |    |

|              |          |                          | ADDRE |    |                                                                                                                                                                                            |    |    |    |    |     | DATA  | BITS  | 5      |    |                |       |      |    |    |

|--------------|----------|--------------------------|-------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|----|-----|-------|-------|--------|----|----------------|-------|------|----|----|

| REGIST<br>ER | TY<br>PE | RESET                    | SS    | D1 | D1                                                                                                                                                                                         | D1 | D1 | D1 | D1 | D9  | D8    | D7    | D6     | D5 | D4             | D3    | D2   | D1 | D0 |

|              |          |                          | BITS  | 5  | 4                                                                                                                                                                                          | 3  | 2  | 1  | 0  | 00  | 00    | 01    | 00     |    |                |       | 02   |    |    |

| GAIN         | R/<br>W  | 16'h0000<br>16'h00F<br>F | 7'h04 |    | CL         CL           R-4         R0         RE           TO         TO         F           7-         3-         DIV           MS         MS         EN           K         K         K |    |    |    |    |     |       |       |        |    |                |       |      |    |    |

| TRIGGE<br>R  | w        | 16'h0000                 | 7'h05 |    | Reserved LD AC SOFT-RESE                                                                                                                                                                   |    |    |    |    |     |       |       |        |    |                | ESET[ | 3:0] |    |    |

| BRDCA<br>ST  | R/<br>W  | 16'h0000                 | 7'h06 |    | BRDCAST-DATA[15:0]                                                                                                                                                                         |    |    |    |    |     |       |       |        |    |                |       |      |    |    |

| STATUS       | R/<br>W  | 16'h0000                 | 7'h07 |    | Reserved                                                                                                                                                                                   |    |    |    |    |     |       |       |        |    | RE<br>FA<br>LM |       |      |    |    |

| DAC0         | R/<br>W  | 16'h0000<br>16'h8000     | 7'h08 |    |                                                                                                                                                                                            |    |    |    |    | DAC | 0-DA  | TA[15 | 5:0]   |    |                |       |      |    |    |

| DAC1         | R/<br>W  | 16'h0000<br>16'h8000     | 7'h09 |    |                                                                                                                                                                                            |    |    |    |    | DAC | C1-DA | TA[15 | 5:0]   |    |                |       |      |    |    |

| DAC2         | R/<br>W  | 16'h0000<br>16'h8000     | 7'h0a |    |                                                                                                                                                                                            |    |    |    |    | DAC | 2-DA  | TA[15 | 5 : 0] |    |                |       |      |    |    |

| DAC3         | R/<br>W  | 16'h0000<br>16'h8000     | 7'h0b |    |                                                                                                                                                                                            |    |    |    |    | DAC | 3-DA  | TA[15 | 5 : 0] |    |                |       |      |    |    |

| DAC4         | R/<br>W  | 16'h0000<br>16'h8000     | 7'h0c |    |                                                                                                                                                                                            |    |    |    |    | DAC | :4-DA | TA[15 | 5 : 0] |    |                |       |      |    |    |

| DAC5         | R/<br>W  | 16'h0000<br>16'h8000     | 7'h0d |    | DAC5-DATA[15 : 0]                                                                                                                                                                          |    |    |    |    |     |       |       |        |    |                |       |      |    |    |

| DAC6         | R/<br>W  | 16'h0000<br>16'h8000     | 7'h0e |    |                                                                                                                                                                                            |    |    |    |    | DAC | C6-DA | TA[15 | 5 : 0] |    |                |       |      |    |    |

| DAC7         | R/<br>W  | 16'h0000<br>16'h8000     | 7'h0f |    |                                                                                                                                                                                            |    |    |    |    | DAC | 7-DA  | TA[15 | 5 : 0] |    |                |       |      |    |    |

### **NOP Register**

| Bit  | Field | Туре | Reset  | Description                                       |

|------|-------|------|--------|---------------------------------------------------|

| 15:0 | NOP   | w    | 0x0000 | No operation. Write 0000h for proper no-operation |

| 10.0 |       |      |        | command                                           |

### **Device ID Register**

| Bit  | Field           | Туре | Reset      | Description      |                                                     |

|------|-----------------|------|------------|------------------|-----------------------------------------------------|

|      | 15:2 DEVICEID R |      | Device ID: |                  |                                                     |

| 15:2 |                 | R    |            | D15 Reserved - 0 |                                                     |

| 15.2 | DEVICEID        |      |            |                  | D14:12 Resolution - 000 (16-bit); 001 (14-bit); 010 |

|      |                 |      |            | (12-bit)         |                                                     |

| Bit | Field     | Туре | Reset Description                  |                                      |  |

|-----|-----------|------|------------------------------------|--------------------------------------|--|

|     |           |      | D11:8 Channels - 1000 (8 channels) |                                      |  |

|     |           |      |                                    | D7 Reset - 0 ; 1 reset- to-midscale) |  |

|     |           |      |                                    | D6:2 Reserved - 00101                |  |

| 1:0 | VERSIONID | R    | 10                                 | Version ID. Subject to change        |  |

### Sync Register

| Bit | Field           | Туре | Reset | Description                                                                                              |

|-----|-----------------|------|-------|----------------------------------------------------------------------------------------------------------|

| 15  | DAC7-BRDCAST-EN | R/W  | 1     |                                                                                                          |

| 14  | DAC6-BRDCAST-EN | R/W  | 1     | When est to 1 the corresponding DAC is set to                                                            |

| 13  | DAC5-BRDCAST-EN | R/W  | 1     | When set to 1 the corresponding DAC is set to<br>update its output after a serial interface write to the |

| 12  | DAC4-BRDCAST-EN | R/W  | 1     | BRDCAST register.                                                                                        |

| 11  | DAC3-BRDCAST-EN | R/W  | 1     | When cleared to 0 the corresponding DAC output                                                           |

| 10  | DAC2-BRDCAST-EN | R/W  | 1     | remains unaffected after a serial interface write to the                                                 |

| 9   | DAC1-BRDCAST-EN | R/W  | 1     | BRDCAST register.                                                                                        |

| 8   | DAC0-BRDCAST-EN | R/W  | 1     |                                                                                                          |

| 7   | DAC7-SYNC-EN    | R/W  | 0     |                                                                                                          |

| 6   | DAC6-SYNC-EN    | R/W  | 0     |                                                                                                          |

| 5   | DAC5-SYNC-EN    | R/W  | 0     | When set to 1 the corresponding DAC output is set to update in response to an LDAC trigger (synchronous  |

| 4   | DAC4-SYNC-EN    | R/W  | 0     | mode).                                                                                                   |

| 3   | DAC3-SYNC-EN    | R/W  | 0     | When cleared to 0 the corresponding DAC output                                                           |

| 2   | DAC2-SYNC-EN    | R/W  | 0     | is set to update immediately on a CS rising edge                                                         |

| 1   | DAC1-SYNC-EN    | R/W  | 0     | (asynchronous mode).                                                                                     |

| 0   | DAC0-SYNC-EN    | R/W  | 0     |                                                                                                          |

### **Config Register**

| Bit   | Field    | Туре | Reset                       | Description                                                                                                                                                                                                                                                        |

|-------|----------|------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:14 | Reserved |      | 00 Reserved for factory use |                                                                                                                                                                                                                                                                    |

| 13    | ALM-SEL  | R/W  | 0                           | ALARM Select<br>0:ALARMpin is CRC-ERROR<br>1: ALARM pin is REF-ALARM                                                                                                                                                                                               |

| 12    | ALM-EN   | R/W  | 0                           | Configure SDO/ALARM pin. When 1: SDO/ALARM<br>pin is an active-low, open-drain, alarm pin. An<br>external 10 kΩ pullup resistor to V <sub>lo</sub> required. FSDO<br>and DSDO bits are ignored. When 0: SDO/ALARM<br>pin is a serial interface, push-pull, SDO pin |

| 11    | CRC-EN   | R/W  | 0                           | CRC enable bit. Set to 1 to enable CRC. Set to 0 to disable                                                                                                                                                                                                        |

| 10    | FSDO     | R/W  | 0                           | Fast SDO bit (half-cycle speedup). When 0, SDO<br>updates on an SCLK rising edge. When 1, SDO<br>updates a half-cycle earlier, during an SCLK falling<br>edge.                                                                                                     |

| Bit | Field      | Туре | Reset | Description                                                                                                                                                      |

|-----|------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9   | DSDO       | R/W  | 0     | Disable SDO bit. When1, SDO is always tri-stated. When 0, SDO is driven while $\overline{\text{CS}}$ is low, and tri-stated while $\overline{\text{CS}}$ is high |

| 8   | REF-PWDWN  | R/W  | 0     | When set to 1 disables the device internal reference                                                                                                             |

| 7   | DAC7-PWDWN | R/W  | 0     |                                                                                                                                                                  |

| 6   | DAC6-PWDWN | R/W  | 0     |                                                                                                                                                                  |

| 5   | DAC5-PWDWN | R/W  | 0     |                                                                                                                                                                  |

| 4   | DAC4-PWDWN | R/W  | 0     | When set to 1 the corresponding DAC is set in power-                                                                                                             |

| 3   | DAC3-PWDWN | R/W  | 0     | down mode and its output is connected to GND<br>through a 1 kΩ internal resistor.                                                                                |

| 2   | DAC2-PWDWN | R/W  | 0     |                                                                                                                                                                  |

| 1   | DAC1-PWDWN | R/W  | 0     |                                                                                                                                                                  |

| 0   | DAC0-PWDWN | R/W  | 0     |                                                                                                                                                                  |

### **Gain Register**

| Bit   | Field                       | Туре | Reset | Description                                                                                                                                                                    |

|-------|-----------------------------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:11 | Reserved                    | _    | 0     | Reserved for factory use.                                                                                                                                                      |

| 10    | Reserved / CLR-4TO7-<br>MSK | R/W  | 0     | For non-clear pin device: Reserved for factory use.<br>For clear pin device. When cleared to 0 the                                                                             |

| 9     | Reserved / CLR-0TO3-<br>MSK | R/W  | 0     | corresponding DAC group is set to clear in response<br>to a logic-low value on the CLR pin. When set to 1 the<br>corresponding DAC group remains unaffected by the<br>CLR pin. |

| 8     | REFDIV-EN                   | R/W  | 0/1   | When set to 1 the reference voltage is internally<br>divided by a factor of 2.<br>When cleared to 0 the reference voltage is<br>unaffected.                                    |

| 7     | BUFF7-GAIN                  | R/W  | 0/1   |                                                                                                                                                                                |

| 6     | BUFF6-GAIN                  | R/W  | 0/1   |                                                                                                                                                                                |

| 5     | BUFF5-GAIN                  | R/W  | 0/1   | <ul> <li>When set to 1 the buffer amplifier for corresponding</li> <li>DAC has a gain of 2. Default value for the default</li> </ul>                                           |

| 4     | BUFF4-GAIN                  | R/W  | 0/1   | middle scale output devices.                                                                                                                                                   |

| 3     | BUFF3-GAIN                  | R/W  | 0/1   | When cleared to 0 the buffer amplifier for                                                                                                                                     |

| 2     | BUFF2-GAIN                  | R/W  | 0/1   | corresponding DAC has a gain of 1. Default value for                                                                                                                           |

| 1     | BUFF1-GAIN                  | R/W  | 0/1   | the default zero scale output devices.                                                                                                                                         |

| 0     | BUFF0-GAIN                  | R/W  | 0/1   |                                                                                                                                                                                |

### **Trigger Register**

| Bit  | Field    | Туре | Reset                       | Description                                                                                                     |

|------|----------|------|-----------------------------|-----------------------------------------------------------------------------------------------------------------|

| 15:5 | Reserved |      | 0 Reserved for factory use. |                                                                                                                 |

| 4    | LDAC     | w    | 0                           | Set this bit to 1 to synchronously load those DACs that have been set in synchronous mode in the SYNC register. |

| Bit | Field           | Туре | Reset | Description                                   |

|-----|-----------------|------|-------|-----------------------------------------------|

| 2.0 |                 | 14/  | 0.40  | When set to the reserved code 1010 resets the |

| 3:0 | SOFT-RESET[3:0] | W    | 0x0   | device to its default state.                  |

#### **Broadcast Register**

| Bit  | Field              | Туре | Reset  | Description                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|------|--------------------|------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 15:0 | BRDCAST-DATA[15:0] | R/W  | 0×0000 | Writing to the BRDCAST register forces those DAC<br>channels that have been set to broadcast in the<br>SYNC register to update their active data register with<br>the BRDCAST-DATA value.<br>Data are MSB aligned in straight binary format and<br>follows the format below:<br>16bit version: { DATA[15:0] } 14bit version:<br>{ DATA[13:0], x, x }<br>12bit version: { DATA[11:0], x, x, x, x }<br>x - Don't care bits |  |  |  |  |

#### **Status Register**

| Bit  | Field    | Туре | Reset                       | Description                                                                                                                                                                 |

|------|----------|------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:1 | Reserved | _    | 0 Reserved for factory use. |                                                                                                                                                                             |

| 0    | REF-ALM  | R    | 0                           | Reference alarm bit. Reads 1 when the difference<br>between V <sub>REF</sub> /DIV and V <sub>DD</sub> is below the required<br>minimum analog threshold. Reads 0 otherwise. |

### DAC Register (Address = 0x8 to 0xF)

| Bit  | Field           | Туре | Reset               | Description                                                                                                                                                                                                                                                                                                                                                                                                                |

|------|-----------------|------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | DACx-DATA[15:0] | R/W  | 0x0000 or<br>0x8000 | Stores the 16-, 14- or 12-bit data to be loaded to<br>DACx in MSB aligned straight binary format. The<br>default value is zero-code for default zero scale<br>output version, midscale-code for the default middle<br>scale output version.<br>Data follows the format below:<br>16bit version: { DATA[15:0] }<br>14bit version: { DATA[13:0], x, x }<br>12 bit version: { DATA[11:0], x, x, x, x }<br>x – Don't care bits |

## **Application and Implementation**

Note

Information in the following application sections is not part of the 3PEAK's component specification and 3PEAK does not warrant its accuracy or completeness. 3PEAK's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### **Application Information**

The TPC219 seris has high linearity, small package size and internal reference, which are suitable for applications such as optical networking, Test equipment, industrial automation and data acquisition systems.

### **Typical Application**

## Layout

### Layout Guideline

- Both input capacitors and output capacitors must be placed to the device pins as close as possible.

- It is recommended to bypass the input pin to ground with a 0.1 µF bypass capacitor.

- It is recommended to use wide trace lengths or thick copper weight to minimize I×R drop and heat dissipation.

- Exposed pad must be connected to the PCB ground plane directly, the copper area must be as large as possible.

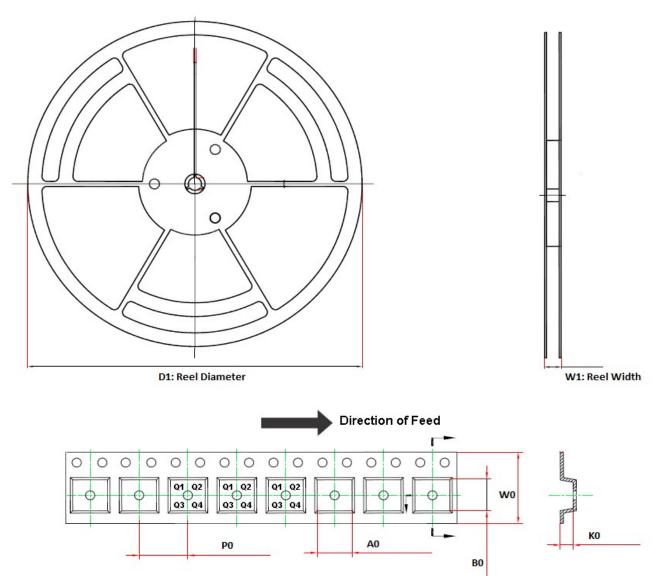

# **Tape and Reel Information**

| Order Number      | Package   | D1 (mm) | W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P0 (mm) | W0 (mm) | Pin1<br>Quadrant |

|-------------------|-----------|---------|---------|---------|---------|---------|---------|---------|------------------|

| TPC2190-<br>QFNR  | QFN3X3-16 | 330     | 17.6    | 3.3     | 3.3     | 1       | 8       | 12      | Q1               |

| TPC2190M-<br>QFNR | QFN3X3-16 | 330     | 17.6    | 3.3     | 3.3     | 1       | 8       | 12      | Q1               |

| TPC2190-<br>WLPR  | WLCSP     | 178     | 12.2    | 2.6     | 2.6     | 0.73    | 4.0     | 8       | Q1               |

| TPC2192-<br>WLPR  | WLCSP     | 178     | 12.2    | 2.6     | 2.6     | 0.73    | 4.0     | 8       | Q1               |

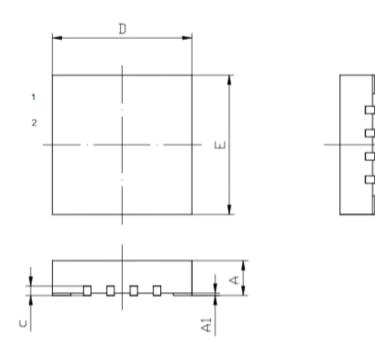

# Package Outline Dimensions

### QFN3X3-16

NOTES

1. Do not include mold flash or protrusion.

2. This drawing is subject to change without notice.

| Symbol |       | ensions<br>Ilimeters | Dimensions<br>In Inches |       |  |

|--------|-------|----------------------|-------------------------|-------|--|

| -      | MIN   | MAX                  | MIN                     | MAX   |  |

| A      | 0.700 | 0.800                | 0.028                   | 0.031 |  |

| A1     | 0.000 | 0.050                | 0.000                   | 0.002 |  |

| b      | 0.180 | 0.300                | 0.007                   | 0.012 |  |

| o      | 0.203 | REF                  | 0.008 REF               |       |  |

| D      | 2.900 | 3.100                | 0.114                   | 0.122 |  |

| D2     | 0.700 | 0.900                | 0.028                   | 0.035 |  |

| E      | 2.900 | 3.100                | 0.114                   | 0.122 |  |

| E2     | 0.700 | 0.900                | 0.028                   | 0.035 |  |

| e      | 0.50  | 0 BSC                | 0.020                   | BSC   |  |

| L      | 0.300 | 0.500                | 0.012                   | 0.020 |  |

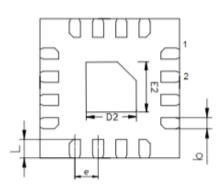

### WLCSP

### **Order Information**

| Order Number  | Operating Temperature<br>Range | Package   | Marking Information | MSL | Transport Media, Quantity | Eco Plan |

|---------------|--------------------------------|-----------|---------------------|-----|---------------------------|----------|

| TPC2190-QFNR  | −40 to 125°C                   | QFN3X3-16 | 2190                | 1   | Tape and Reel, 4000       | Green    |

| TPC2190M-QFNR | −40 to 125°C                   | QFN3X3-16 | 2190M               | 1   | Tape and Reel, 4000       | Green    |

| TPC2190-WLPR  | −40 to 125°C                   | WLCSP     | 190                 | 1   | Tape and Reel, 3000       | Green    |

| TPC2192-WLPR  | −40 to 125°C                   | WLCSP     | 192                 | 1   | Tape and Reel, 3000       | Green    |

(1) For future products, contact the 3PEAK factory for more information and sample. 3PEAK defines "Green" to mean RoHS compatible and free of halogen substances.

Green: 3PEAK defines "Green" to mean RoHS compatible and free of halogen substances.

Trademarks. Any of the 思瑞浦 or 3PEAK trade names, trademarks, graphic marks, and domain names("Trademarks") contained in this document/material are the property of 3PEAK. You may NOT reproduce, modify, publish, transmit or distribute any Trademark without the prior written consent of 3PEAK.

Performance Information. Performance tests or performance range contained in this document/material are results of design simulation or actual tests conducted under designated testing environment. Any differences in testing environment or simulation environment, including but not limited to testing method, testing process or testing temperature, may affect actual performance of the product.

Forward-Looking Statements. The information in this document/material may contain forward-looking statements, except for statements or descriptions of historical facts. These forward-looking statements are based upon our current understanding of our industry, management philosophy and certain assumptions and speculative calculations. These forward-looking statements are subject to risks and uncertainties and our actual results may differ. Please do not rely solely on the above information to make your business decisions.