### **Features**

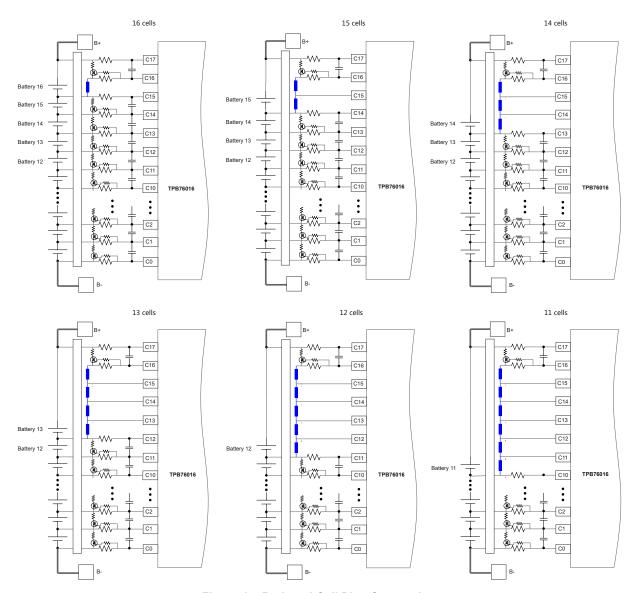

- · Measures up to 17 Cells in Series

- Voltage Measurement

- 2-mV Cell Voltage Measurement Accuracy (typical)

- 50-ms Conversation Time for 17 Cells (Nominal)

- Current Measurement

- ±100-mV Measurement Range Across Sense Resistor

- 50-μV Current Measurement Accuracy (typical)

- Support Low Leakage Current

Deep Sleep Mode: 25 μA

Sleep Mode: 30 μAShutdown Mode: 2.5 μA

- Extensive Protection Including Voltage, Current,

- Temperature

High Voltage Tolerance of ±80 V on Cell Connect

- Support for Temperature Sensing Using Internal Sensor and up to 4 External Thermistors

- Integrated Programmable Memory for Customer Use

- Integrated Secondary Chemical Fuse Drive Protection

- Autonomous or Host-controlled Cell Balance

- 1-Mbps SPI Communication Interface

- Operational Temperature Range: −40°C to +125°C

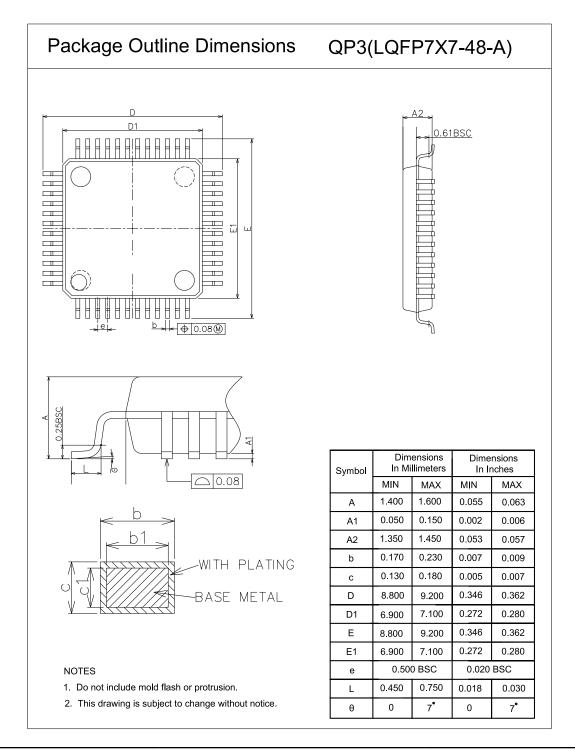

- LQFP7x7-48 Package

## **Applications**

- Telecom 48 V UPS

- E-bike or E-motor or LEV

- Garden Tools

- Drones

## **Description**

The TPB76016 is a multicell battery stack monitor that measures up to 17 series battery cells with a total measurement error of less than 5 mV typical. The cell measurement range is from 0 V to 5 V, with supporting Li-ion, Li-Polymer, and LiFePO4 battery types. All 17 cells can be measured within 50 ms. The TPB76016 also integrates an ADC to measure charge/discharge current and provides a coulomb counter.

The TPB76016 integrates a safety engine that provides reliability protection for OV, UV, OTC, UTC, OTD, UTD, COC, DOC, SCD, SOV with programmable detection threshold and delay time. The COC, DOC, and SCD use a hardware comparator for fast protection.

The TPB76016 provides internal cell balance, the cell balance current is 50 mA, for a higher cell balance current, an external cell balance circuit may be used.

The device has a host communication peripheral supporting 1-Mbps SPI. The TPB76016 is available in the LQFP7x7-48 package, and the operation temperature range is from -40°C to 125°C.

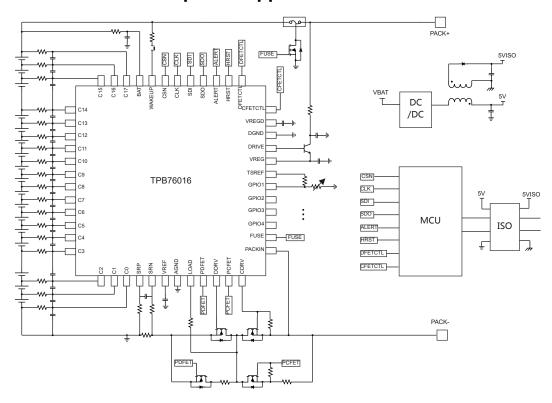

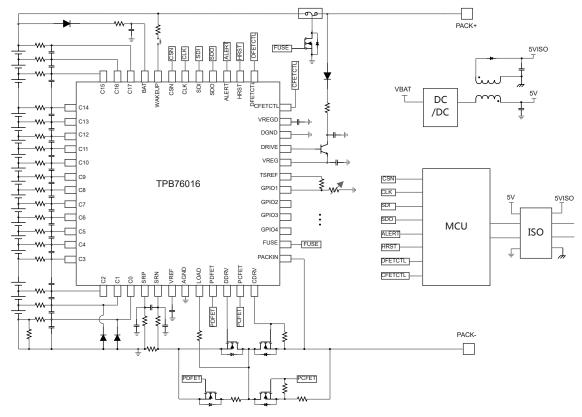

# **Simplified Application Circuit**

www.3peak.com 2 / 98 FA20230601A1

## **Table of Contents**

| Features                                | 1  |

|-----------------------------------------|----|

| Applications                            | 1  |

| Description                             | 1  |

| Simplified Application Circuit          | 2  |

| Product Family Table                    | 4  |

| Revision History                        | 4  |

| Pin Configuration and Functions         | 5  |

| Specifications                          | 8  |

| Absolute Maximum Ratings                | 8  |

| ESD, Electrostatic Discharge Protection | 9  |

| Recommended Operating Conditions        | 9  |

| Thermal Information                     | 9  |

| Electrical Characteristics              | 10 |

| Typical Performance Characteristics     | 14 |

| Detailed Description                    | 15 |

| Overview                                | 15 |

| Functional Block Diagram                | 15 |

| Feature Description                     | 16 |

| Register Maps                           | 29 |

| Application and Implementation          | 89 |

| Application Information                 | 89 |

| Typical Application                     | 89 |

| Reduced Cell Count Applications         | 90 |

| Unused Pins                             | 91 |

| Layout                                  | 93 |

| Layout Guideline                        | 93 |

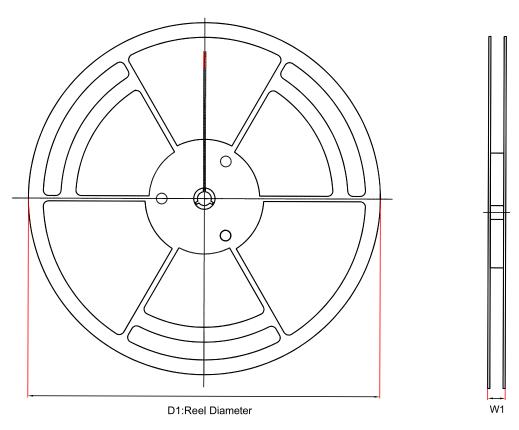

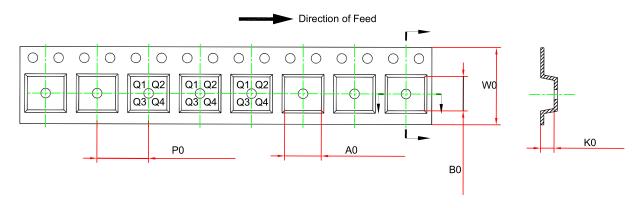

| Tape and Reel Information               | 94 |

| Package Outline Dimensions              | 95 |

| LQFP7x7-48                              | 95 |

| Order Information                       | 96 |

| IMPORTANT NOTICE AND DISCLAIMER         | 97 |

# **Product Family Table**

| Order Number MSL |   | Marking Information | Package |  |

|------------------|---|---------------------|---------|--|

| TPB76016-QP3R    | 3 | 76016               | LQFP-48 |  |

## **Revision History**

| Date       | Revision | Notes                                                                                                                                                                                                                             |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2024-09-18 | Rev. A.0 | Initial release                                                                                                                                                                                                                   |

| 2025-03-08 | Rev. A.1 | Corrected typo of t <sub>COC_DLY</sub> , t <sub>DOC_DLY</sub> , t <sub>SCD_DLY</sub> in the EC table Corrected typos in description Updated ALERT pin description Updated Host mode description Updated SPI Interface description |

www.3peak.com 4 / 98 FA20230601A1

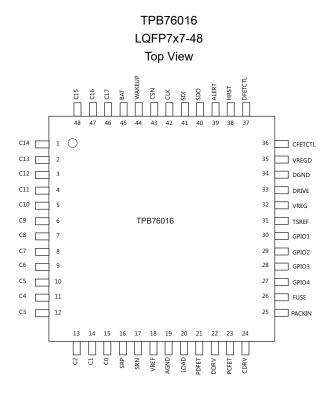

## **Pin Configuration and Functions**

Table 1. Pin Functions: TPB76016

| No | Name | I/O | Description                                                                                                                                                |

|----|------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | C14  | I   | Cell voltage sense connection 14. Connect C14 to the junction of the positive terminal of cell 14 and the negative terminal of cell 15 through a resistor. |

| 2  | C13  | I   | Cell voltage sense connection 13. Connect C13 to the junction of the positive terminal of cell 13 and the negative terminal of cell 14 through a resistor. |

| 3  | C12  | I   | Cell voltage sense connection 12. Connect C12 to the junction of the positive terminal of cell 12 and the negative terminal of cell 13 through a resistor. |

| 4  | C11  | I   | Cell voltage sense connection 11. Connect C11 to the junction of the positive terminal of cell 11 and the negative terminal of cell 12 through a resistor. |

| 5  | C10  | I   | Cell voltage sense connection 10. Connect C10 to the junction of the positive terminal of cell 10 and the negative terminal of cell 11 through a resistor. |

| 6  | C9   | I   | Cell voltage sense connection 9. Connect C9 to the junction of the positive terminal of cell 9 and the negative terminal of cell 10 through a resistor.    |

www.3peak.com 5 / 98 FA20230601A1

| No | Name   | I/O | Description                                                                                                                                            |

|----|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7  | C8     | I   | Cell voltage sense connection 8. Connect C8 to the junction of the positive terminal of cell 8 and the negative terminal of cell 9 through a resistor. |

| 8  | C7     | I   | Cell voltage sense connection 7. Connect C7 to the junction of the positive terminal of cell 7 and the negative terminal of cell 8 through a resistor. |

| 9  | C6     | I   | Cell voltage sense connection 6. Connect C6 to the junction of the positive terminal of cell 6 and the negative terminal of cell 7 through a resistor. |

| 10 | C5     | I   | Cell voltage sense connection 5. Connect C5 to the junction of the positive terminal of cell 5 and the negative terminal of cell 6 through a resistor. |

| 11 | C4     | I   | Cell voltage sense connection 4. Connect C4 to the junction of the positive terminal of cell 4 and the negative terminal of cell 5 through a resistor. |

| 12 | С3     | ı   | Cell voltage sense connection 3. Connect C3 to the junction of the positive terminal of cell 3 and the negative terminal of cell 4 through a resistor. |

| 13 | C2     | ı   | Cell voltage sense connection 2. Connect C2 to the junction of the positive terminal of cell 2 and the negative terminal of cell 3 through a resistor. |

| 14 | C1     | I   | Cell voltage sense connection 1. Connect C1 to the junction of the positive terminal of cell 1 and the negative terminal of cell 2 through a resistor. |

| 15 | C0     | I   | Cell voltage sense connection 0. Connect C0 to the junction of the negative terminal of cell 1 through a resistor.                                     |

| 16 | SRP    | I   | Current sense positive input pin.                                                                                                                      |

| 17 | SRN    | I   | Current sense negative input pin.                                                                                                                      |

| 18 | VREF   | 0   | Voltage reference. Connect a bypass capacitor to ground. Do not connect any external load on this pin.                                                 |

| 19 | AGND   | GND | Analog ground                                                                                                                                          |

| 20 | LOAD   | I   | Load detect pin.                                                                                                                                       |

| 21 | PDFET  | 0   | Predischarge FET control pin.                                                                                                                          |

| 22 | DDRV   | 0   | Discharge FET control pin.                                                                                                                             |

| 23 | PCFET  | 0   | Precharge FET control pin.                                                                                                                             |

| 24 | CDRV   | 0   | Charge FET control pin.                                                                                                                                |

| 25 | PACKIN | I   | Pack voltage input pin.                                                                                                                                |

| 26 | FUSE   | 0   | Fuse drive.                                                                                                                                            |

| 27 | GPIO4  | I/O | General purpose input/output 4. GPIO4 is configurable as an ADC input to measure an external temperature sensor (NTC) or other DC voltage.             |

www.3peak.com 6 / 98 FA20230601A1

| No | Name    | I/O | Description                                                                                                                                                |

|----|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28 | GPIO3   | I/O | General purpose input/output 3. GPIO3 is configurable as an ADC input to measure an external temperature sensor (NTC) or other DC voltage.                 |

| 29 | GPIO2   | I/O | General purpose input/output 2. GPIO2 is configurable as an ADC input to measure an external temperature sensor (NTC) or other DC voltage.                 |

| 30 | GPIO1   | I/O | General purpose input/output 1. GPIO1 is configurable as an ADC input to measure an external temperature sensor (NTC) or other DC voltage.                 |

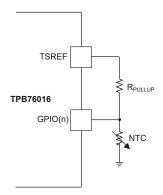

| 31 | TSREF   | 0   | Temperature bias output voltage for NTC                                                                                                                    |

| 32 | VREG    | I   | Input pin for internal supply. 2.2µF capacitor is recommended to connected to ground.                                                                      |

| 33 | DRIVE   | 0   | Base control for external pre-regulator transistor.                                                                                                        |

| 34 | DGND    | GND | Digital ground.                                                                                                                                            |

| 35 | VREGD   | 0   | Digital voltage supply for GPIO.                                                                                                                           |

| 36 | CFETCTL | I   | Charge FET control input pin.                                                                                                                              |

| 37 | DFETCTL | I   | Discharge FET control input pin.                                                                                                                           |

| 38 | HRST    | I   | Hardware reset pin.                                                                                                                                        |

| 39 | ALERT   | 0   | Interruption output pin. ALERT is open drain output, it outputs an 10-ms low pulse when fault occurs, if the fault persists, the ALERT output remains low. |

| 40 | SDO     | 0   | Slave data output pin.                                                                                                                                     |

| 41 | SDI     | I   | Slave data input pin.                                                                                                                                      |

| 42 | CLK     | I   | Clock input pin.                                                                                                                                           |

| 43 | CSN     | I   | Selection input pin. Active low.                                                                                                                           |

| 44 | WAKEUP  | I   | External wakeup pin from shutdown mode. High active. Connect to high if using this device in standalone protection mode always.                            |

| 45 | BAT     | I   | Battery stack connection.                                                                                                                                  |

| 46 | C17     | I   | Cell voltage sense connection 17. Connect C17 to the positive terminal of top cell through a resistor.                                                     |

| 47 | C16     | I   | Cell voltage sense connection 16. Connect C16 to the junction of the positive terminal of cell 16 and the negative terminal of cell 17 through a resistor. |

| 48 | C15     | I   | Cell voltage sense connection 15. Connect C15 to the junction of the positive terminal of cell 15 and the negative terminal of cell 16 through a resistor. |

www.3peak.com 7 / 98 FA20230601A1

## **Specifications**

### **Absolute Maximum Ratings**

|                  | Parameter                                                                       | Min  | Max | Unit |

|------------------|---------------------------------------------------------------------------------|------|-----|------|

|                  | BAT to AGND                                                                     | -0.3 | 80  | V    |

|                  | Cn to Cn-1 (n=1 to 17)                                                          | -80  | 80  | V    |

|                  | Cn to AGND (n=1 to 17)                                                          | -0.3 | 80  | V    |

|                  | C0 to AGND                                                                      | -0.3 | 6.5 | V    |

|                  | GPIOn to AGND (n=1 to 4)                                                        | -0.3 | 6.5 | V    |

| Input Voltage    | CSN, SDI, CLK, CFETCTL, DFETCTL, HRST to AGND                                   | -0.3 | 6.5 | V    |

|                  | SRN, SRP to AGND                                                                | -0.5 | 0.7 | V    |

|                  | SRN, SRP to AGND (1ms pulse, $10\Omega$ resistor in series with pin externally) | -0.5 | 3.6 | V    |

|                  | LOAD to AGND, WAKEUP to AGND                                                    | -0.3 | 80  | V    |

|                  | PACKIN to BAT                                                                   | -80  | 0   | V    |

|                  | VREG, VREGD to AGND                                                             | -0.3 | 6.5 | V    |

|                  | VREF, TSREF to AGND                                                             | -0.3 | 6.5 | V    |

|                  | SDO to AGND                                                                     | -0.3 | 6.5 | V    |

| Output Voltage   | DRIVE to AGND                                                                   | -0.3 | 6.5 | V    |

|                  | CDRV, PCFET to BAT                                                              | -80  | 0   | V    |

|                  | DDRV, PDFET to AGND                                                             | -0.3 | 20  | V    |

|                  | FUSE to AGND                                                                    | -0.3 | 20  | V    |

|                  | DRIVE, GPIOn(n=1-4), SDO current                                                |      | 10  | mA   |

|                  | FUSE                                                                            |      | 100 | mA   |

| Output Current   | DDRV, PDFET current                                                             |      | 50  | mA   |

|                  | VREGD current                                                                   |      | 40  | mA   |

|                  | TSREF current                                                                   |      | 20  | mA   |

| T <sub>A</sub>   | Operating Temperature Range                                                     | -40  | 125 | °C   |

| TJ               | Junction Temperature Range                                                      | -40  | 150 | °C   |

| T <sub>STG</sub> | Storage Temperature Range                                                       | -55  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

www.3peak.com 8 / 98 FA20230601A1

<sup>(2)</sup> This data was taken with the JEDEC low effective thermal conductivity test board.

<sup>(3)</sup> This data was taken with the JEDEC standard multilayer test boards.

### **ESD, Electrostatic Discharge Protection**

| Parameter |                          | Parameter Condition        |      | Unit |

|-----------|--------------------------|----------------------------|------|------|

| НВМ       | Human Body Model ESD     | ANSI/ESDA/JEDEC JS-001 (1) | 2000 | V    |

| CDM       | Charged Device Model ESD | ANSI/ESDA/JEDEC JS-002 (2) | 1000 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### **Recommended Operating Conditions**

|                         | Parameter                                                                  |     |  | Max | Unit |

|-------------------------|----------------------------------------------------------------------------|-----|--|-----|------|

| $V_{BAT}$               | Total Battery Module Voltage (VBAT), full functionality available          | 12  |  | 75  | V    |

| $V_{\text{CELL\_DIFF}}$ | Cell Differential Voltage (Cn-Cn-1, n=1 to 17)                             | 0   |  | 5   | ٧    |

| VCELL_COM               | Cell Common Voltage (C0-AGND)                                              | 0   |  | 0.3 | V    |

| V <sub>IO</sub>         | GPIOn (n=1 to 4), SDI, SDO, CSN, CLK, HRST, DFETCTL, CFETCTL input voltage | 0   |  | 5   | V    |

| I <sub>IO</sub>         | GPIOn (n=1 to 6), SDO current                                              | -5  |  | 5   | mA   |

| ITSREF                  | Bias Voltage for External Pull up for Temperature Current                  |     |  | 10  | mA   |

| T <sub>OPR</sub>        | Operating Temperature                                                      | -40 |  | 125 | °C   |

### **Thermal Information**

| Package Type | θ <sub>JA</sub> | θυς  | Unit |

|--------------|-----------------|------|------|

| LQFP7x7-48   | 50.3            | 17.4 | °C/W |

www.3peak.com 9 / 98 FA20230601A1

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **Electrical Characteristics**

All test conditions:  $V_{BAT}$  = 62 V,  $T_A$  = -40°C to 85°C, unless otherwise noted.

| Symbol               | Parameter                                                        | Conditions                                                                                                                                   | Min      | Тур  | Max  | Unit   |

|----------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------|------|------|--------|

| Voltage N            | Measurement ADC                                                  |                                                                                                                                              | <u> </u> | 1    | 1    | '      |

| V <sub>VADC_IN</sub> | Input Voltage Range for Cell Voltage<br>Measurement              |                                                                                                                                              | 0        |      | 5    | V      |

| V <sub>VADC_LS</sub> | Measurement Resolution                                           |                                                                                                                                              |          | 0.1  |      | mV/Bit |

| V <sub>OFFSET</sub>  | ADC Offset Voltage                                               |                                                                                                                                              |          | 0.1  |      | mV     |

| GERR                 | ADC Gain Error                                                   |                                                                                                                                              |          | 0.01 |      | %      |

|                      | Cn - Cn-1 = 1.5 V, T <sub>A</sub> =<br>-20°C to 65°C, n =1 to 17 | -5.0                                                                                                                                         |          | 5.0  | mV   |        |

|                      |                                                                  | Cn - Cn-1 = 3.1 V, T <sub>A</sub> =<br>-20°C to 65°C, n =1 to 17                                                                             | -5.0     |      | 5.0  | mV     |

|                      | V <sub>TME</sub> Total Measurement Error                         | Cn - Cn-1 = 3.9 V, T <sub>A</sub> =<br>-20°C to 65°C, n = 1 to 17                                                                            | -5.0     |      | 5.0  | mV     |

|                      |                                                                  | Cn - Cn-1= 4.5V, $T_A$ =-20°C to 65°C, n=1 to 17                                                                                             | -5.0     |      | 5.0  | mV     |

|                      |                                                                  | Cn - Cn-1 = 1.5 V, $T_A$ = -40°C to 85°C, n = 1 to 17                                                                                        | -5.0     |      | 5.0  | mV     |

|                      |                                                                  | Cn - Cn-1 = 3.1 V, T <sub>A</sub> =<br>-40°C to 85°C, n=1 to 17                                                                              | -5.0     |      | 5.0  | mV     |

| $V_{TME}$            |                                                                  | Cn - Cn-1 = 3.9 V, T <sub>A</sub> =<br>-40°C to 85°C, n=1 to 17                                                                              | -5.5     |      | 5.5  | mV     |

|                      |                                                                  | Cn - Cn-1 = 4.5 V, T <sub>A</sub> =<br>-40°C to 85°C, n = 1 to 17                                                                            | -6.0     |      | 6.0  | mV     |

|                      |                                                                  | GPIOn to AGND = $0.6 \text{ V}$<br>~3.3 V, T <sub>A</sub> = $-40^{\circ}\text{C}$ to $85^{\circ}\text{C}$ ,<br>n = 1 to 4                    | -15.0    |      | 15.0 | mV     |

|                      |                                                                  | GPIOn to AGND = 0.6V<br>~ V <sub>TSREF</sub> , T <sub>A</sub> = -40°C to<br>85°C, n =1 to 4, accuracy<br>for thermistor ratio, % of<br>TSREF | -0.5     |      | 0.5  | %      |

|                      |                                                                  | BAT to AGND, $T_A = -40^{\circ}$ C to 85°C                                                                                                   | -1.5     |      | 1.5  | %      |

|                      | Input Leakage Current When Inputs not                            | Cn, n = 0 to 17                                                                                                                              |          | 10   |      | nA     |

| I <sub>lkg_M</sub>   | being Measured                                                   | GPIOn, n = 1 to 4                                                                                                                            |          | 10   |      | nA     |

| lu o                 | Input Leakage Current When Inputs not                            | Cn, n = 0 to 17                                                                                                                              |          | ±1   |      | μA     |

| I <sub>lkg_</sub> S  | being Measured                                                   | GPIOn, n = 1 to 4                                                                                                                            |          | ±1   |      | μA     |

www.3peak.com 10 / 98 FA20230601A1

All test conditions:  $V_{BAT}$  = 62 V,  $T_A$  = -40°C to 85°C, unless otherwise noted.

| Symbol               | Parameter                                   | Conditions                                                                                            | Min   | Тур | Max  | Unit   |

|----------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------|-------|-----|------|--------|

| Voltage F            | Reference                                   |                                                                                                       |       |     |      |        |

| .,                   | Main Reference Voltage                      | VREF Pin, No Load                                                                                     | 3.28  | 3.3 | 3.32 | V      |

| V <sub>REF</sub>     | Main Reference Voltage TC                   | VREF Pin, No Load                                                                                     |       | 10  |      | ppm/°C |

| V <sub>TSREF</sub>   | Buffered Reference Voltage                  | VTSREF Pin, No load to 1k<br>Load                                                                     | 3.27  | 3.3 | 3.33 | V      |

|                      | Buffered Reference Voltage TC               | VTSREF Pin, No Load                                                                                   |       | 20  |      | ppm/°C |

| Current N            | Measurement ADC                             |                                                                                                       |       |     |      |        |

| V <sub>CADC_IN</sub> | Input Voltage Range for Current Measurement | V <sub>SRP</sub> - V <sub>SRN</sub>                                                                   | -0.1  |     | 0.1  | V      |

| V<br>CADC_LSB        | Current Sense Measurement Resolution        |                                                                                                       |       | 4   |      | μV/LSB |

|                      |                                             | V <sub>SRP</sub> - V <sub>SRN</sub> = 0, T <sub>A</sub> = 25°C                                        | -30   |     | 30   | μV     |

| .,                   | Current ADC Total Measurement Error (1)     | $V_{SRP} - V_{SRN} = 0$ , $T_A = -40$ °C to 85°C                                                      | -90   |     | 120  | μV     |

| V <sub>CADC_TM</sub> |                                             | $V_{SRP}$ - $V_{SRN}$ = -0.1 V to 0.1<br>V, $T_A$ = -20°C to 65°C                                     | -150  |     | 150  | μV     |

|                      |                                             | $V_{SRP} - V_{SRN} = -0.1 \text{ V to } 0.1$<br>V, $T_A = -40^{\circ}\text{C to } 85^{\circ}\text{C}$ | -220  |     | 220  | μV     |

| V <sub>CC_GAIN</sub> | Gain error                                  |                                                                                                       | -0.14 |     | 0.14 | %      |

| R <sub>CC_IN</sub>   | Effective Input Resistance                  |                                                                                                       |       | 100 |      | kΩ     |

| General I            | DC Specifications                           |                                                                                                       |       |     |      |        |

|                      |                                             | Shutdown Mode                                                                                         |       | 2.5 | 4    | μA     |

| I <sub>BAT</sub>     | Current of BAT Pin                          | Deep Sleep Mode                                                                                       |       | 10  |      | μA     |

| IDAI                 | Garrent of BATT III                         | Sleep Mode                                                                                            |       | 30  |      | μA     |

|                      |                                             | Normal Mode                                                                                           |       | 30  |      | μA     |

| V <sub>BAT</sub>     | BAT Supply Voltage Range                    |                                                                                                       | 12    |     | 75   | V      |

|                      |                                             | Deep Sleep Mode                                                                                       |       | 10  |      | μA     |

| $I_{REG}$            | VREG Current                                | Sleep Mode                                                                                            |       | 10  |      | μA     |

|                      |                                             | Normal Mode                                                                                           |       | 2.5 |      | mA     |

| V <sub>REG</sub>     | VREG Supply Voltage                         | no load,                                                                                              |       | 5   |      | V      |

| $V_{DRIVE}$          | DRIVE Output Voltage                        | Sourcing 1 µA                                                                                         |       | 5.7 |      | V      |

|                      |                                             | Sourcing 500 μA                                                                                       |       | 5.7 |      | V      |

| V <sub>REGD</sub>    | Digital Supply Voltage                      | 5mA load                                                                                              |       | 3.3 |      | V      |

|                      | Balancing<br>⊺                              |                                                                                                       |       |     |      |        |

| R <sub>BAL_ON</sub>  | Internal Cell Balancing Resistance          |                                                                                                       |       | 45  |      | Ω      |

<sup>(1)</sup> Guaranteed by bench test

www.3peak.com 11 / 98 FA20230601A1

All test conditions:  $V_{BAT}$  = 62 V,  $T_A$  = -40°C to 85°C, unless otherwise noted.

| Symbol                 | Parameter                                                                   | Conditions                                                    | Min                       | Тур   | Max                       | Unit |

|------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------|-------|---------------------------|------|

| Logic Inpu             | t and Output                                                                |                                                               |                           |       |                           |      |

| Vон                    | Logic-level Output-voltage High, SDO                                        | I <sub>LOAD</sub> = 5 mA                                      | 0.6×<br>V <sub>REGD</sub> |       | $V_{REGD}$                | V    |

| V <sub>OL</sub>        | Logic-level Output Low, SDO                                                 | I <sub>LOAD</sub> = 5mA                                       |                           |       | 0.8                       | V    |

| V <sub>IH</sub>        | Logic-level Input-voltage High,<br>CSN, CLK, SDI, HRST,<br>DFETCTL, CFETCTL |                                                               | 0.7×<br>V <sub>REGD</sub> |       | V <sub>REGD</sub>         | V    |

| V <sub>IL</sub>        | Logic-level Input-voltage Low,<br>CSN, CLK, SDI, HRST,<br>DFETCTL, CFETCTL  |                                                               |                           |       | 0.3×<br>V <sub>REGD</sub> | V    |

| I <sub>LKG</sub>       | Input Leakage Current                                                       | SCLK,SDI                                                      |                           |       | 1                         | μA   |

| Wakeup                 |                                                                             |                                                               |                           |       |                           |      |

| V <sub>IH_WAKEUP</sub> | WAKEUP High-input Voltage                                                   | WAKEUP in shutdown mode                                       | 2                         |       |                           | ٧    |

| twakeup_ho             | WAKEUP Hold Time                                                            |                                                               |                           | 8     |                           | ms   |

| Load Dete              | ction                                                                       |                                                               |                           |       | 1                         |      |

| $V_{LOAD\_RM}$         | Load Removal Detect Voltage                                                 | V <sub>BAT</sub> > 12 V                                       |                           | 1     |                           | ٧    |

| I <sub>LOAD</sub>      | Leakage Current                                                             | $V_{LOAD} = V_{BAT} = 80 \text{ V}, R_{LOAD}$ is disconnected |                           |       | 1                         | μA   |

| Б                      | Internal Decistor to ACND                                                   | VM_PD_SEL[1:0] = 11                                           |                           | 45    |                           | kΩ   |

| R <sub>LOAD</sub>      | Internal Resistor to AGND                                                   | VM_PD_SEL[1:0] = 00                                           |                           | 1900  |                           | kΩ   |

| PACKIN                 |                                                                             |                                                               |                           |       |                           |      |

| VPACKINH               | Charger In Detect Voltage High                                              |                                                               |                           | -0.3  |                           | V    |

| V <sub>PACKIN_RM</sub> | Charger Removal Detect Voltage                                              |                                                               |                           | -0.15 |                           | V    |

| I <sub>PACKIN</sub>    |                                                                             |                                                               |                           |       | 1                         | μA   |

| RPACKIN                |                                                                             |                                                               |                           | 800   |                           | ΜΩ   |

| PCFET and              | d PDFET Drive                                                               |                                                               |                           |       |                           |      |

| V <sub>PCFET_ON</sub>  | Output Voltage, PCFET on                                                    | $R_{load} = 1 M\Omega$                                        |                           | 10    |                           | V    |

| IPULLUP_PCF<br>ET      | Current Sink for PCFET                                                      |                                                               | 8                         | 10    | 14                        | μA   |

| V <sub>PDFET_ON</sub>  | Output Voltage, PDFET on                                                    |                                                               | 8                         | 12    | 16                        | V    |

| R <sub>PULLDOWN</sub>  | R Pulldown for PDFET                                                        |                                                               |                           | 100   |                           | Ω    |

www.3peak.com 12 / 98 FA20230601A1

| Symbol                   | Parameter                                                            | Conditions                  | Min  | Тур | Max  | Unit |

|--------------------------|----------------------------------------------------------------------|-----------------------------|------|-----|------|------|

| CDRV and                 | DDRV                                                                 |                             |      |     |      |      |

| V <sub>CFET_ON</sub>     | Output Voltage, CFET on                                              | Rload = 1 M                 |      | 10  |      | V    |

| I <sub>PULLUP_</sub> CFE | Current Sink for CFET                                                |                             | 8    | 10  | 14   | μΑ   |

| V <sub>DFET_ON</sub>     | Output Voltage, DFET on                                              |                             | 8    | 12  | 16   | V    |

| R <sub>PULLDOWN</sub>    | R Pulldown for DFET                                                  |                             |      | 100 |      | Ω    |

| FUSE Drive               | 9                                                                    |                             |      |     |      |      |

| V <sub>OH</sub>          | Output Voltage High                                                  | C <sub>L</sub> = 1 nF, 5 kΩ |      | 12  | 14   | V    |

| Current Co               | mparator Protection                                                  |                             |      |     |      |      |

| Vcoc                     | Overcurrent in Charge Threshold<br>Setting Range <sup>(1)</sup>      | 4-mV step                   | 4    |     | 128  | mV   |

| V <sub>COCA</sub>        | V <sub>COC</sub> Accuracy                                            | Setting ≥ 16 mV             |      | 5   |      | mV   |

| t <sub>COC_DLY</sub>     | V <sub>COC</sub> Delay <sup>(1)</sup>                                | 40-ms step                  | 10   |     | 1250 | ms   |

| V <sub>DOC</sub>         | Overcurrent in Discharge Threshold Setting Range (1)                 | 6-mV step                   | 12   |     | 198  | mV   |

| V <sub>DOCA</sub>        | V <sub>DOC</sub> Accuracy                                            | Setting ≥ 42 mV             |      | 5   |      | mV   |

| t <sub>DOC_DLY</sub>     | V <sub>DOC</sub> Delay <sup>(1)</sup>                                | 40-ms step                  | 10   |     | 1250 | ms   |

| V <sub>SCD</sub>         | Short Current in Discharge<br>Threshold Setting Range <sup>(1)</sup> |                             | 16   |     | 384  | mV   |

| V <sub>SCD_ACC</sub>     | V <sub>SCD</sub> Accuracy                                            | Setting ≥ 48 mV             |      | 5   |      | mV   |

| t <sub>SCD_DLY</sub>     | V <sub>SCD</sub> Delay <sup>(1)</sup>                                | 10-μs step                  | 5    |     | 155  | μs   |

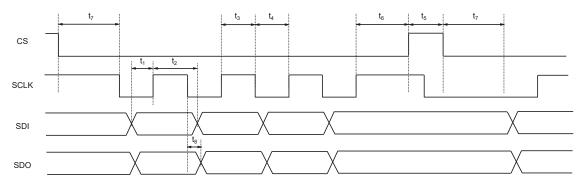

| SPI Timing               | Requirements (2) (See Figure 12)                                     |                             | _    |     |      |      |

| t <sub>CLK</sub>         | SPI Clock Period                                                     |                             | 1    |     |      | μs   |

| t <sub>1</sub>           | SDI Setup Time before SCLK<br>Rising Edge                            |                             | 25   |     |      | ns   |

| t <sub>2</sub>           | SDI Hold Time after SCLK Rising Edge                                 |                             | 25   |     |      | ns   |

| t <sub>3</sub>           | SCLK High                                                            |                             | 200  |     |      | ns   |

| t <sub>4</sub>           | SCLK Low                                                             |                             | 200  |     |      | ns   |

| t <sub>5</sub>           | CS Rising Edge to CS Falling Edge                                    |                             | 0.65 |     |      | μs   |

| t <sub>6</sub>           | SCLK Rising Edge to CS Rising Edge                                   |                             | 0.8  |     |      | μs   |

| t <sub>7</sub>           | CS Falling Edge to SCLK Falling Edge                                 |                             | 1    |     |      | μs   |

| t <sub>8</sub>           | SCLK Falling Edge to SDO Valid                                       |                             |      |     | 60   | ns   |

<sup>(1)</sup> Guarantee by bench test(2) Design Guarantee

13 / 98 FA20230601A1 www.3peak.com

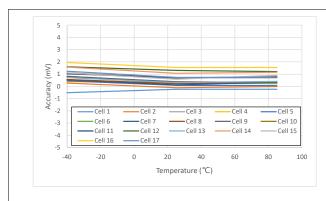

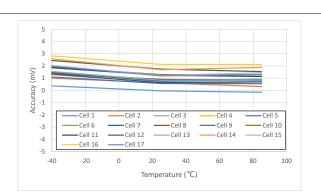

### **Typical Performance Characteristics**

All test conditions: V<sub>BAT</sub> = 62 V, T<sub>A</sub> = +25°C, unless otherwise noted.

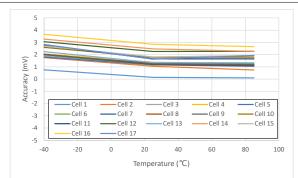

Figure 1. Cell Voltage Measurement Error vs.

Temperature with Cell Voltage = 1.5 V

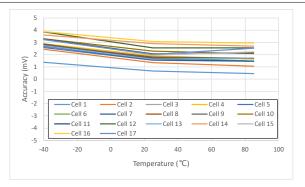

Figure 2. Cell Voltage Measurement Error vs.

Temperature with Cell Voltage = 2.3 V

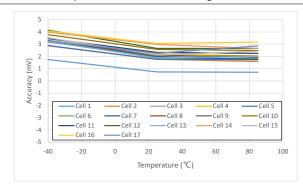

Figure 3. Cell Voltage Measurement Error vs.

Temperature with Cell Voltage = 3.1 V

Figure 4. Cell Voltage Measurement Error vs.

Temperature with Cell Voltage = 3.9 V

Figure 5. Cell Voltage Measurement Error vs.

Temperature with Cell Voltage = 4.5 V

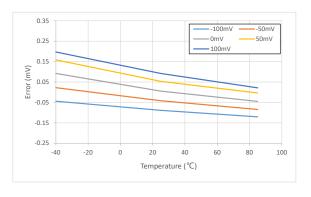

Figure 6. Current Measurement Error vs. Temperature

www.3peak.com 14 / 98 FA20230601A1

## **Detailed Description**

#### Overview

The TPB76016 is a multicell battery stack monitor that measures up to 17 series battery cells with a total measurement error of less than 5mV typical. The cell measurement range is from 0V to 5V, with supporting Li-ion, Li-Polymer, and LiFePO4 battery types. All 17 cells can be measured within 50ms. The TPB76016 also integrates an ADC to measure charge/discharge current with a coulomb counter, which provides data for host-based algorithms and control. The TPB76016 integrates a safety engine that provides reliability protection for OV, UV, OTC, UTC, OTD, UTD, COC, DOC, SCD, and SOV with programmable detection threshold and delay time. The COC, DOC, and SCD use a hardware comparator for fast protection. The TPB76016 provides internal cell balance, the cell balance current is 50 mA, for a higher cell balance current, an external cell balance circuit may be used.

The TPB76016 has a host communication peripheral supporting 1Mbps SPI, multiple digital control and status data are available through SPI. The device includes an interrupt to the host and independent control for host override of each low-side protection NFET. There are four GPIO pins which can be used for temperature measurements using external thermistors, and a FUSE drive to control external fuse to achieve secondary protection. The one-time-programmable (OTP) memory is available for customers to set up device operation on their own side.

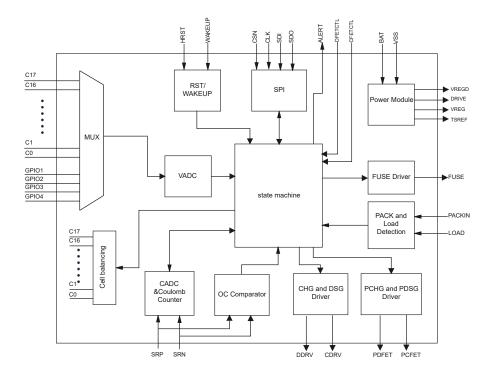

## **Functional Block Diagram**

Figure 7. Functional Block Diagram

www.3peak.com 15 / 98 FA20230601A1

#### **Feature Description**

#### **Operation Modes**

The TPB76016 supports two operation modes, one is standalone mode, another is host mode. In standalone mode, the TPB76016 can operate independently to fulfill the measurement and protection, while it also provides the flexibility of cooperation with the host through the SPI interface, external host can access the internal registers of the TPB76016 to get ADC measurement results and protection state, and etc. In host mode, TPB76016 doesn't implement measurement without host control, and the protection should be implemented by the host to control and charge FET and discharge FET, while the over-current protection is operated by the device independently. After power-on reset, TPB76016 enters standalone mode by default, host mode is available by factory trim.

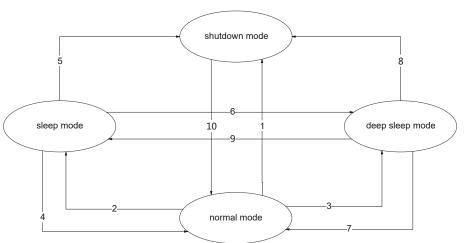

In standalone mode, the TPB76016 has four power modes to support optimized features and power consumption, the device is able to transit between modes either automatically or controlled by the host.

- Norma mode: in this mode, the device performs frequent measurements of cell voltages, current, thermistor temperature and various other voltages, operates protection, and provides data and status updates.

- Sleep mode: there are wake period and quiet period in this mode. In the wake period, the operation is the same as normal mode. In the quiet period, the ADC measurement is disabled, the REF voltage is off, the TSREF voltage can be set on or off, the cell balance and load detection function are disabled either, the power consumption is reduced, and the current hardware protections are still enabled. The wake period and quiet period are adjustable in registers 0X45 and 0X46. In sleep mode, the device total average current consumption of the device is reduced.

- Deep sleep mode: in this mode, the operation is the same as the quiet period of sleep mode, the device total current consumption of the device is reduced further.

- Shutdown mode: in this mode, the device is completely disabled, all measurement and protection are disabled, and the CHG, PCHG, DSG, and PDSG FETs are all disabled, while the WAKEUP and charger in detection are still enabled. This is the lowest power state of the device, which may be used for shipment or long-term storage. After powering on, the TPB76016 enters this mode.

The power mode transition is shown below.

Figure 8. Power Mode Transition

The power mode transition table is as below.

| Transition | Transition Initial Mode Condition |                        | Final Mode      |

|------------|-----------------------------------|------------------------|-----------------|

| 4          | Nia was al Nia al a               | SPI SHUTDOWN command   | CLULTDOWN Marke |

| 1          | Normal Mode                       | HRST high pulse > 8 ms | SHUTDOWN Mode   |

www.3peak.com 16 / 98 FA20230601A1

| Transition | Initial Mode   | Condition                                                                                                                                                        | Final Mode     |  |  |

|------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|

|            |                | SUV shutdown                                                                                                                                                     |                |  |  |

|            |                | Low BAT voltage                                                                                                                                                  |                |  |  |

|            |                | Thermal shutdown                                                                                                                                                 |                |  |  |

| 2          |                | SPI SLEEP command (configurable)  AND Enter sleep mode is enabled  AND No fault  AND Standalone  AND charge/discharge current lower than sleep current threshold | SLEEP Mode     |  |  |

| 3          |                | SPI DEEPSLEEP command                                                                                                                                            | DEEPSLEEP Mode |  |  |

|            |                | SPI Exit_SLEEP command                                                                                                                                           |                |  |  |

| 4          |                | Fault occurs                                                                                                                                                     | Normal Mode    |  |  |

| 4          |                | Charge/Discharge Current larger than sleep current threshold                                                                                                     | - Normal Mode  |  |  |

|            | 0, 555 14      | HRST high pulse>8ms                                                                                                                                              |                |  |  |

|            | SLEEP Mode     | Low BAT voltage                                                                                                                                                  |                |  |  |

| 5          |                | SUV shutdown                                                                                                                                                     | SHUTDOWN Mode  |  |  |

|            |                |                                                                                                                                                                  |                |  |  |

|            |                | Thermal shutdown                                                                                                                                                 |                |  |  |

| 6          |                | SPI DEEPSLEEP command                                                                                                                                            | DEEPSLEEP Mode |  |  |

| 7          |                | SPI exit DEEPSLEEP command                                                                                                                                       | Normal Mode    |  |  |

| 7          |                | Charger plug in detected                                                                                                                                         | Normal Mode    |  |  |

|            |                | SPI SHUTDWON Command                                                                                                                                             |                |  |  |

| 0          | DEEPSLEEP Mode | HRST high pulse>8ms                                                                                                                                              | CLUITDOWN Mada |  |  |

| 8          |                | Thermal shutdown                                                                                                                                                 | SHUTDOWN Mode  |  |  |

|            |                | Low BAT voltage                                                                                                                                                  |                |  |  |

| 9          |                | SPI SLEEP Command                                                                                                                                                | SLEEP Mode     |  |  |

|            |                | Charger plug in detected                                                                                                                                         |                |  |  |

| 10         | SHUTDOWN Mode  | WAKEUP high pulse>8ms                                                                                                                                            | Normal Mode    |  |  |

|            |                | SPI bus active                                                                                                                                                   |                |  |  |

In host mode, the TPB76016 operates in normal power mode and waits for the host command to implement measurement, if the host sends the SPI SHUTDOWN command, the device enters shutdown mode. In power-up procedure of host mode device, the host should disable measurement firstly by configuring REG0x47H to 0xFF, REG0x48H to 0x7F, REG0x49H to 0xF0, then send a command to implement measurement.

#### **Voltage Measurement ADC**

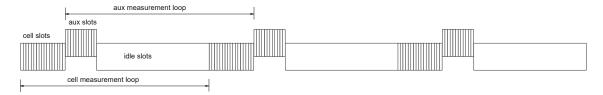

The TPB76016 integrates a 16-bit  $\Sigma$ - $\Delta$  ADC with multiplex to measure cell voltages, up to four external thermistors, BAT voltage, VAO, BG, VDRIVE, LOAD pin, VREG, VREGD, and TSREF. The TPB76016 supports cells up to 17-series cell, each cell voltage is a differential measurement of Cn and Cn-1 (n=1 to 17), and each cell voltage measurement range is 0 to 5V with 100 $\mu$ V/LSB. All 17 cell voltages are measured in a cell measurement loop which consists of multiple measurement slots, each cell voltage takes a measurement slot. LOAD pin is measured in the load detection measurement loop, and

www.3peak.com 17 / 98 FA20230601A1

external thermistors, BAT voltage, VAO, and other voltages are measured in the aux measurement loop, each voltage takes a measurement slot. There is an open wire measurement loop dedicated to the open wire detection period.

Each measurement loop time can be set from 50ms to 10s through registers, while open wire measurement loop time is set from 1s to 80s, see more detail in REG0x47H and REG0x48H. Take the cell voltage measurement loop and aux measurement loop for example, the measurement slot in each measurement loop is arranged as in Figure 9, the measurement slots take a small section of measurement loop time, and the remaining is injected with idle slots. Customers can get more accurate ADC results by setting higher OSR in CELL\_OSR, AUX\_OSR, and LD\_OSR bits.

Figure 9. Measurement Slot Timing

The voltage measurement ADC results are stored in 16-bit registers, from register 0XC0 to 0XFD.

#### **Current Measurement ADC**

The TPB76016 implements another 16-bit  $\Sigma$ - $\Delta$  ADC to measure the charge/discharge current, the current is sensed via the sense resistor between the SRP and SRN pins through an external RC filter. The current ADC input voltage range is -0.1 V to 0.1 V with 4  $\mu$ V/LSB. The current is measured in the current measurement loop, the loop time can be set from 50 ms to 10 s through the register, see more detail in REG0x49H. Customers can get more accurate ADC results by setting higher OSR in the CADC\_OSR bit.

The current measurement ADC result is a 16-bit signed number, stored in registers 0XFE and 0XFF, the 1 in signed bit means discharge current, and 0 means charge current.

The TPB76016 also provides a coulomb counter in 32-bit format stored in registers 0XAB to 0XAE, the MSB is the sign bit, 1 means discharge current, and 0 means charge current. The coulomb counter is updated every 10 ms. If the registers 0XAB to 0XAE are full, the CCUF\_FLG or CCOF\_FLG bit will be set.

#### **Measurement in Host Mode**

In host mode, TPB76016 waits for the host poll command to implement ADC measurement, when the measurement is done, the TPB76016 provides the done indication in the POLL\_STAT bit, and the host should implement the read command to get the measurement results. Refer to the SPI Interface section for more information about poll command and read command.

#### **Protection**

The TPB76016 integrates a safety engine that provides reliability protection for OV, UV, OTC, UTC, OTD, UTD, COC, DOC, SCD, and SOV with a programmable detection threshold and delay time.

- 1. Over Voltage Protection

- The TPB76016 monitors the voltages of every cell using voltage measurement ADC, if any cell voltage is higher than the over-voltage threshold for a deglitch time, the over-voltage protection is triggered. The over-voltage threshold is set in OV TH SEL bits, the deglitch time is set in OV DLY SEL bits.

- In over voltage state, the TPB76016 turns off CHG FET, enable charger removal detection and load insert detection, sets the corresponding bit in the over-voltage status register and over-voltage flag register, and triggers an alert signal to the host if OV ALT EN is enabled.

- The over-voltage protection is released if all cell voltages decrease to less than the over voltage release threshold, which is set in OV\_RCV\_SEL bits. The corresponding bit in over voltage status is cleared, while the flag bit needs the host to clear.

- 2. Under Voltage Protection

www.3peak.com 18 / 98 FA20230601A1

The TPB76016 monitors the voltages of every cell using voltage measurement ADC, if any cell voltage is lower than under-voltage threshold for a deglitch time, the under-voltage protection is triggered. The under-voltage threshold is set in UV TH SEL bits, the deglitch time is set in UV DLY SEL bits.

In the under voltage state, the TPB76016 turns off discharge FET, enables load removal detection, sets the corresponding bit in under the voltage status register and under the voltage flag register, and triggers an alert signal to host if UV ALT EN is enabled.

The under-voltage protection is released if all cell voltages rise higher than the under voltage release threshold, which is set in UV\_RCV\_SEL bits. The corresponding bit in under voltage status is cleared, while the flag bit needs the host to clear.

#### 3. Super Under Voltage Protection

In the under voltage state, if any cell voltage still decreases to lower than the super under voltage threshold for a deglitch time, the super under voltage protection is triggered, the super under voltage threshold is set in SUV\_TH\_SEL bits, the deglitch time is set in SUV\_DLY\_SEL bits.

When super under voltage protection is triggered, the device enters shutdown mode.

#### 4. Over Temperature Charge

The TPB76016 monitors the temperature of the NTC thermistor via the voltage of the GPIO pin where the NTC thermistor is connected, if the GPIO voltage is lower than over-temperature charger threshold, for a deglitch time, the over-temperature charge protection is triggered. The over-temperature charge threshold is set in OTC\_TH\_SEL bits, the deglitch time is set in OTC\_DLY\_SEL bits.

In over temperature charge state, the CHG FET and DSG FET are turned off, the corresponding bit in GPIOn\_OTC\_STAT register and GPIOn\_OTC\_STAT flag register are set, and an alert signal is triggered if OTC\_ALT\_EN is enabled. The over-temperature charge protection is released if GPIOn voltage is higher than over temperature charge recovery threshold, set in OTC\_RCV\_SEL bits, for deglitch time, set in OTC\_RCV\_DLY\_SEL, the corresponding status bit is cleared, while the flag bit needs a host to clear.

#### 5. Under Temperature Charge

The TPB76016 monitors the temperature of the NTC thermistor via the voltage of the GPIO pin where the NTC thermistor is connected, if GPIO voltage is higher than the under-temperature charger threshold, set in UTC\_TH\_SEL bits, for a deglitch time, set in UTC\_DLY\_SEL bits, the under temperature charge protection is triggered.

In under temperature charge state, the CHG FET and DSG FET are turned off, the corresponding bit in GPIOn\_UTC\_STAT register and GPIOn\_UTC\_STAT flag register are set, and an alert signal is triggered if UTC\_ALT\_EN is enabled.

The under-temperature charge protection is released if GPIOn voltage is lower than under temperature charge recovery threshold, set in UTC\_RCV\_SEL bits, for deglitch time, set in UTC\_RCV\_DLY\_SEL bits, the corresponding status bit is cleared, while the flag bit needs a host to clear.

### 6. Over Temperature Discharge

The TPB76016 monitors the temperature of the NTC thermistor via the voltage of the GPIO pin where the NTC thermistor is connected, if the GPIO voltage is lower than over temperature discharger threshold, set in OTD\_TH\_SEL bits, for a deglitch time, set in OTD\_DLY\_SEL bits, the over temperature discharge protection is triggered. In over temperature discharge state, the DSG FET is turned off, the corresponding bit in GPIOn\_OTD\_STAT register and GPIOn\_OTD\_STAT flag register are set, and an alert signal is triggered if OTD\_ALT\_EN is enabled. The over-temperature discharge protection is released if the GPIOn voltage is higher than over temperature discharge recovery threshold, set in OTD\_RCV\_SEL bits, for deglitch time, set in OTD\_RCV\_DLY\_SEL bits, the corresponding status bit is cleared, while the flag bit needs the host to clear.

#### 7. Under Temperature Discharge

The TPB76016 monitors the temperature of the NTC thermistor via the voltage of the GPIO pin where the NTC thermistor is connected, if the GPIO voltage is higher than under temperature discharger threshold, set in UTD\_TH\_SEL bits, for a deglitch time, set in UTD\_DLY\_SEL bits, the under-temperature discharge protection is triggered. In under temperature discharge state, the DSG FET is turned off, the corresponding bit in GPIOn\_UTD\_STAT register and GPIOn\_UTD\_STAT flag register are set, and an alert signal is triggered if UTD\_ALT\_EN is enabled. The under-temperature discharge protection is released if GPIOn voltage is lower than under temperature discharge recovery threshold, set in UTD\_RCV\_SEL bits, for deglitch time, set in UTD\_RCV\_DLY\_SEL bits, the corresponding status bit is cleared, while the flag bit needs the host to clear.

#### 8. Charge Over Current

www.3peak.com 19 / 98 FA20230601A1

The TPB76016 detects the charge current via the hardware comparator, if the charge current is larger than the charge over the current threshold for a deglitch time, the charge over current protection is triggered. The charge over the current threshold is set in COC\_SEL bits, the deglitch time is set in COC\_DLY\_SEL bits.

In charge over current state, the TPB76016 turns off the CHG FET, enables charger removal detection, sets COC\_STAT bit and COC\_FLG bit, and triggers an alert signal to the host if OCC\_ALT\_EN is enabled.

The charge over current protection is released in either of the three ways below, which can be selected in COC\_RCV\_SEL bits.

- · Charger removal is detected

- After the recovery delay time, which is set in COC\_RCV\_DLY\_SEL bits.

- After recovery delay time for three times, if over current is still there, the state is latched, needs the host to release the latch by setting CLR CUR bit.

#### 9. Discharge Over Current

The TPB76016 detects the discharge current via the hardware comparator, if the discharge current is larger than the discharge over current threshold for a deglitch time, the discharge over current protection is triggered. The discharge over current is set in DOC\_SEL bits, the deglitch time is set in DOC\_DLY\_SEL bits.

In discharge over current state, the TPB76016 turns off the DSG FET, enables charger insert detection and load removal detection, sets DOC\_STAT bit and DOC\_FLG bit, and triggers an alert signal to host if DOC\_ALT\_EN is enabled. The discharge over current protection is released in either one of below three ways below, which can be selected in

- · Load removal is detected

- After the recovery delay time, which is set in DOC\_RCV\_DLY\_SEL bits.

- After recovery delay time for three times, if over current is still there, the state is latched, and need a host to release the latch by setting CLR CUR bit.

### 10. Discharge Short Current

DOC RCV SEL bits.

The TPB76016 detects the discharge current via the hardware comparator, if the discharge current is larger than the discharge short current threshold for a deglitch time, the discharge short current protection is triggered. The discharge short current is set in SCD\_SEL bits, the deglitch time is set in SCD\_DLY\_SEL bits.

In the discharge short current state, the TPB76016 turns off the DSG FET, enables charger insert detection and load removal detection, sets SCD\_STAT bit and SCD\_FLG bit, and triggers an alert signal to host if SCD\_ALT\_EN is enabled. The state is latched.

The discharge short current protection is released in either one of below two ways below, which can be selected in SCD\_RCV\_SEL bits.

- Host releases the latch by setting CLR\_CUR bit

- load removal is detected

In host mode, the charge over current protection, discharge over current protection, and discharge short current protection are implemented by the TPB76016 itself, the voltage protection and temperature protection need a host to implement.

### **Open Wire Detection**

The TPB76016 integrates open wire detection. The open wire detection is configured by OW\_PERIOD bits, if these bits are set to 111, the open wire detection is disabled, otherwise, the open wire detection is enabled, and the detection period is fixed by the configuration. The open wire detection depends on the ADC to measure each cell voltage, during each cell detection slot, the cell voltage is measured by ADC for the first time, then the cell balance FET is turned on for a short time, after that, the cell voltage is measured by ADC for the second time, the open wire for that cell is detected if the one of below condition is met

- ADC measurement result each time is lower than 0.5 V.

- The difference between the two ADC measurement results is larger than the open wire threshold, set in OW\_TH\_SEL bits.

www.3peak.com 20 / 98 FA20230601A1

If the open wire is detected, the OW\_STAT and OW\_FLG bit are set, and an alert is triggered if OW\_ALT\_EN is enabled, the OW\_FLG bit needs a host to write CLR\_OW bit to clear. The corresponding cell of open wire is shown in OW\_CH\_STAT bits, and the voltage difference of twice ADC measurement result is shown in OW\_SUB bits.

The open wire detection is checked on each cell one by one from the highest number cell to the lowest.

#### **FET SYNC**

In UV, DOC, and SCD protection, the DSG FET is turned off, if the charger is inserted, charging is allowed, and the charging current flows through the body diode of the DSG FET. While DSG FET can be turned on by the FET SYNC function regardless of UV, DOC, and SCD protection. DSG FET SYNC function should be enabled in DFET\_SYNC\_EN bit first, then configure the DFET in DFETSYNC\_ON bit, when the device detects the charging current larger than the threshold of charging wake current for a deglitch time, the DSGFET is turned on. The charging wake current is set in CWAKED\_SEL bits, and the deglitch time is set in CWAKED\_DLY SEL bits.

Similarly, in OV, COC protection, the CHG FET is turned off, if the load is inserted, discharging is allowed, and the discharging current flows through the body diode of CHG FET. While CHG FET can be turned on by the FET SYNC function regardless of OV and COC protection. CHG FET SYNC function should be enabled in the CFET\_SYNC\_EN bit first, then configure the CFET in the CFETSYNC\_ON bit, when the device detects the discharging current larger than the threshold of discharging wake current for a deglitch time, the CHGFET is turned on. The discharging wake current is set in CWAKEC\_SEL bits, and the deglitch time is set in CWAKEC\_DLY\_SEL bits.

#### **FET Driver and Control**

The TPB76016 integrates the NMOSFET driver, including the CHG FET driver, DSG FET driver, PreCHG FET driver, and PreDSG FET driver, in corresponding to the pins of CDRV, DDRV, PCFET, and PDFET. The DDRV and PDFET are push-pull output, while CDRV and PCFET are current source outputs, the source current capability is set in CDRV\_20U and PCDRV 20U bit. The FET driver is controlled by the state machine.

#### **CHG FET Driver**

The condition of controlling the CHG FET Driver is as below, with priority descending.

- CFETCTL pin control. If the CFETCTL pin detects a high input, the CHG FET is turned off, otherwise, the CHG FET

control depends on the below controls. This pin can be configured to low active by the FET\_CTL\_INV bit.

- FET SYNC function control, as described in the FET SYNC section.

- Register control. CHG FET driver controlled by the register is enabled by setting REG\_CTRL bit to 1, then configuring CFET\_CTL bit to turn on or turn off the CHG FET.

- State machine control. During the power-on initiation procedure, the CHG FET is turned off, then depends on the state

machine after the initiation procedure. In deep sleep mode or shutdown mode, the CHG FET is turned off. In normal

mode or sleep mode, the CHG FET control depends on the protection state.

- In the case that CHG FET is controlled by the register, if COC occurs, CHG FET will be turned off.

#### **DSG FET Driver**

The condition of controlling the DSG FET Driver is as below, with priority descending.

- DFETCTL pin control. If the DFETCTL pin detects a high input, the DSG FET is turned off, otherwise, the DSG FET

control depends on the below controls. This pin can be configured to low active by the FET\_CTL\_INV bit.

- FET SYNC function control, as described in the FET SYNC section.

- Register control. DSG FET driver controlled by register is enabled by setting REG\_CTRL bit to 1, then configure DFET CTL bit to turn on or turn off the DSG FET.

- State machine control. During the power-on initiation procedure, the DSG FET is turned off, then depends on the state machine after the initiation procedure. In deep sleep mode or shutdown mode, the DSG FET is turned off. In normal mode or sleep mode, the DSG FET control depends on the protection state.

www.3peak.com 21 / 98 FA20230601A1

In the case that DSG FET is controlled by the register, if DOC or SCD occurs, DSG FET will be turned off.

#### **PRECHG FET Driver**

The TPB76016 integrates pre CHG FET driver, the condition of controlling pre CHG FET Driver is as below, with priority descending.

- Register control. Pre CHG FET driver controlled by register is enabled by setting the REG\_CTRL bit to 1, then configure

the PCFET\_CTL bit to turn on or turn off the Pre CHG FET.

- State machine control. During power-on initiation procedure, the Pre CHG FET is turned off, then depends on state machine after initiation procedure. In deepsleep mode or shutdown mode, the Pre CHG FET is turned off. In normal mode or sleep mode, the device detects the battery voltage to decide, if the battery voltage is lower than the pre charge threshold, set in PCHG\_SEL bits, the pre CHG FET is turned on, if the battery voltage is higher than the pre charge recovery threshold, set in PCHG\_RCV\_SEL bits, the pre CHG FET is off. In other conditions, the pre CHG FET is off. The CHG FET is off during pre charging.

#### **PREDSG FET Driver**

The TPB76016 integrates pre DSG FET driver. During power-on initiation procedure, the Pre DSG FET is turned off, then depends on state machine after initiation procedure. In deepsleep mode or shutdown mode, the Pre DSG FET is turned off. In normal mode or sleep mode, the pre DSG FET driver is turned off in protection state, or cell balancing is on going, or cell open wire is detected, otherwise, the pre DSG FET is controlled by register. Pre DSG FET driver controlled by register is enabled by setting the REG CTRL bit to 1, then configure the PDFET CTL bit to turn on or turn off the Pre DSG FET.

#### **Cell Balance**

The TPB76016 integrates internal passive cell balance function, and supports odd or even channel cell balance, it is enabled under the conditions that,

- 1. RLX BAL EN is set to 1, which enables cell balance

- 2. No faults occur, except OV, UV and UTC

- 3. Cell balance timer is enabled, which is set in BAL\_TIMER\_DIS bit, and the balance timer is set in BAL\_TO\_SEL and BAL\_RANGE\_SEL bits.

When the cell balance function is enabled, the device monitors each cell voltage in each cell voltage measurement loop, and finds the max voltage cell and min voltage cell. If the max voltage is higher than the balance start threshold, set in VCB\_START\_SEL bits, and the difference voltage between the max cell voltage and min cell voltage is higher than the difference threshold, set in VCB\_TH\_SEL bits, the cell balance conditions are met. If the max voltage cell is odd channel cell, then all the odd channel cells that meet cell balance conditions start balancing, the internal cell balance FET are turned on. So is the same if the max voltage cell is even channel cell.

The balance timer is normally set longer than the cell voltage measurement loop period, if cell voltage measurement is required when cell balancing is on going, the cell balancing suspends, and after a delay time, set in BAL\_RLS\_TIMER\_SEL bits, the cell voltage measurement loop starts, during the cell voltage measurement, the balance timer still counts.

The cell balance stops if the voltage difference between the max cell voltage and min cell voltage is lower than VCB\_TH\_SEL, or if balance timer is out, the balance timeout sets BAL\_TO\_FLG bit, which needs host to clear it, then next cell balance can start.

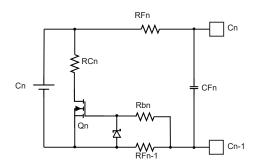

The internal passive cell balance limits the max cell balancing current due to IC thermal consideration. An external circuit is needed when larger cell balancing current is required, the external cell balancing circuit is as below Figure 10. The external balance current is determined by cell voltage, the gate-source voltage of Qn and the value of resistor RCn.

www.3peak.com 22 / 98 FA20230601A1

Figure 10. External Balance Circuit

In host mode, the host can control any channel balance to implement a flexible balance strategy. The host can select the channel for balance in REG0x45H, REG0x46H, and REG0x47H. The 8 bits in REG0x45H are used to select cell 1 to cell 8, with LSB for cell 1 and MSB for cell 8. The 8 bits in REG0x46H are used to select cell 9 to cell 16, with LSB for cell 9 and MSB for cell 16. The bit0 in REG0x47H is used to select cell 17. The start and stop of cell balance in host mode are controlled by poll command, refer SPI Interface section for more information.

#### **Load Detection**