#### **Features**

- Maximum Voltage Input 28V

- Wide Operation Voltage Range from 4V to 24V

- Low Current Consumption

- Normal Mode 4µA at +25°C

- Shutdown Mode 0.4µA at +25°C

- High Accuracy Voltage Detection Circuit for each cell

- Programmable Overcharge Threshold Voltage from 4.1V to 4.8V in 50mV step

- Overcharge Threshold Accuracy ±20mV (+25°C)

- Overcharge Threshold Accuracy ±25mV (-10°C to +60°C)

- Overcharge Hysteresis Voltage –380mV

- Internal Delay Timer for Overcharge

- Selectable Overcharge Detection Delay Time 2s, 4s, 6s, and 8s

- Selectable Delay Time for Shutdown 2s, 4s, 6s, and 8s

- High CO Pull Up Voltage

- Selectable CMOS Active High or Low output

- Test Mode to Shorten Mass Production Time

- Integrated Linear Regulator

- Selectable LDO Output 3.0V, and 3.3V

- LDO output Cut off Voltage 2.5V

- Output Current 2mA

- Short Circuit Protector

### **Applications**

- Notebook

- · Portable Equipment

### **Description**

The TPB7462 series is a secondary overcharge hardware protector for 2s, 3s, or 4s lithium-ion battery packs

TPB7462 series provides high accuracy overcharge threshold to avoid the safety risk from battery pack. It also provides the CTL pin to directly control output or connect PTC (Positive Temperature Coefficient) resistor to monitor overtemperature of battery pack.

The TPB7462 integrates a LDO for powering external circuit with extremely low leakage current.

TPB7462 is available in WDFN2x2-8 package. Its operation temperature range is from -40°C to +85°C.

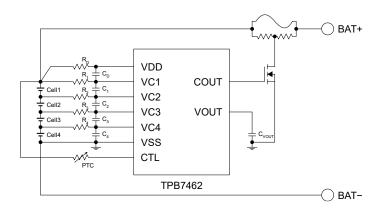

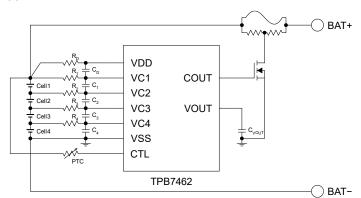

## **Typical Application Circuit**

### **Product Name Rule**

TPB7462 X X X - DFGR

| Function | Sel | ection |

|----------|-----|--------|

|   | CTL Function at Shutdown | Timer Reset Delay Function | COUT        | VOUT |

|---|--------------------------|----------------------------|-------------|------|

| Α | Disable                  | Disable                    | Active High | 3.0V |

| В | Enable                   | Disable                    | Active High | 3.0V |

| С | Disable                  | Enable                     | Active High | 3.0V |

| D | Enable                   | Enable                     | Active High | 3.0V |

| Е | Disable                  | Disable                    | Active High | 3.3V |

| F | Enable                   | Disable                    | Active High | 3.3V |

| G | Disable                  | Enable                     | Active High | 3.3V |

| Н | Enable                   | Enable                     | Active High | 3.3V |

Delay Time Selection

Overvoltage Threshold Selection

|   | Overvoitage Threshold Ociccion |  |  |  |  |

|---|--------------------------------|--|--|--|--|

|   | Overvoltage Threshold          |  |  |  |  |

| Α | 4.800V                         |  |  |  |  |

| В | 4.750V                         |  |  |  |  |

| С | 4.700V                         |  |  |  |  |

| D | 4.650V                         |  |  |  |  |

| Е | 4.600V                         |  |  |  |  |

| F | 4.550V                         |  |  |  |  |

| G | 4.500V                         |  |  |  |  |

| Н | 4.450V                         |  |  |  |  |

| ī | 4.400V                         |  |  |  |  |

| J | 4.350V                         |  |  |  |  |

| K | 4.300V                         |  |  |  |  |

| L | 4.250V                         |  |  |  |  |

|   | Overvoltage Delay Time | Shutdown Delay Time |

|---|------------------------|---------------------|

| Α | 2s                     | 2s                  |

| В | 2s                     | 4s                  |

| С | 2s                     | 6s                  |

| D | 2s                     | 8s                  |

| Е | 4s                     | 2s                  |

| F | 4s                     | 4s                  |

| G | 4s                     | 6s                  |

| Н | 4s                     | 8s                  |

| I | 6s                     | 2s                  |

| J | 6s                     | 4s                  |

| K | 6s                     | 6s                  |

| L | 6s                     | 8s                  |

| М | 8s                     | 2s                  |

| Ν | 8s                     | 4s                  |

| 0 | 8s                     | 6s                  |

| Р | 8s                     | 8s                  |

|   |                        |                     |

### **Table of Contents**

| Features                                | ······································ |

|-----------------------------------------|----------------------------------------|

| Applications                            | ,                                      |

| Description                             | ,                                      |

| Typical Application Circuit             |                                        |

|                                         |                                        |

| Product Name Rule                       |                                        |

| Revision History                        | 4                                      |

| Pin Configuration and Functions         |                                        |

| Pin Functions                           |                                        |

| Specifications                          | (                                      |

| Absolute Maximum Ratings                | 6                                      |

| ESD, Electrostatic Discharge Protection | 6                                      |

| Thermal Information                     | 6                                      |

| Electrical Characteristics              |                                        |

| Typical Performance Characteristics     |                                        |

| Detailed Description                    | 10                                     |

| Overview                                | 10                                     |

| Feature Description                     | 10                                     |

| Application and Implementation          | 12                                     |

| Application Information                 | 12                                     |

| Typical Application                     | 12                                     |

| Layout                                  | 12                                     |

| Layout Guideline                        | 12                                     |

| Tape and Reel Information               | 13                                     |

| Package Outline Dimensions              | 14                                     |

| DFN2X2-8                                | 14                                     |

| Order Information                       | 1                                      |

| IMPORTANT NOTICE AND DISCLAIMER         |                                        |

## **Revision History**

| Date       | Revision | Notes                                 |

|------------|----------|---------------------------------------|

| 2022-04-06 | Rev.A.0  | First Release Version                 |

| 2022-05-23 | Rev.A.1  | Update I <sub>SD</sub> test condition |

www.3peak.com 4 / 16 Rev.A.1

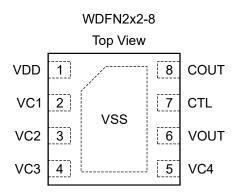

## **Pin Configuration and Functions**

### **Pin Functions**

| Р   | in             | 1/0 | Description                                                                                                         |

|-----|----------------|-----|---------------------------------------------------------------------------------------------------------------------|

| No. | Name           | I/O | Description                                                                                                         |

| 1   | VDD            | I   | Power Supply. Connect a 0.1μF capacitor to ground.                                                                  |

| 2   | VC1            | I   | Voltage Sense Input of Positive Terminator of 1st Cell.                                                             |

| 3   | VC2            | I   | Voltage Sense Input of Positive Terminator of 2 <sup>nd</sup> Cell and Negative Terminator of 1 <sup>st</sup> Cell. |

| 4   | VC3            | I   | Voltage Sense Input of Positive Terminator of 3 <sup>rd</sup> Cell and Negative Terminator of 2 <sup>nd</sup> Cell. |

| 5   | VC4            | I   | Voltage Sense Input of Positive Terminator of 4 <sup>th</sup> Cell and Negative Terminator of 3 <sup>rd</sup> Cell. |

| 6   | VOUT           | 0   | Voltage Regulator Output.                                                                                           |

| 7   | CTL            | I   | Control Pin for COUT.                                                                                               |

| 8   | COUT           | 0   | FET Control. CMOS Output Active High or Active Low, NCH Open Drain Active High                                      |

| 9   | Exposed<br>Pad |     | Ground and Voltage Sense Input of Negative Terminator of 4 <sup>th</sup> Cell.                                      |

www.3peak.com 5 / 16 Rev.A.1

### **Specifications**

### **Absolute Maximum Ratings**

|                        | Parameter                           |            | Max | Unit |

|------------------------|-------------------------------------|------------|-----|------|

| Supply Voltage         | Supply Voltage VDD to VSS           |            | 28  | V    |

|                        | VDD to VC1                          | -0.3       | 6.5 | V    |

| Sense Input<br>Voltage | VCn+1 to VCn, n=1,2,3               | -0.3       | 6.5 | V    |

| Voltage                | VC4 to VSS                          | -0.3       | 6.5 | V    |

| VCO                    | COUT Output Voltage to VSS          | -0.3       | 6.5 | V    |

| VOUT                   | VOUT Output Voltage to VSS          | -0.3       | 6.5 | V    |

| VCTL                   | CTL Pin Input Voltage               | -0.3       | 28  | V    |

| TJ                     | Maximum Junction Temperature        |            | 150 | °C   |

| TA                     | Operating Temperature Range         | <b>–45</b> | 85  | °C   |

| T <sub>STG</sub>       | Storage Temperature Range           | -65        | 150 | °C   |

| TL                     | Lead Temperature (Soldering 10 sec) |            | 300 | °C   |

**Note:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

- (1) This data was taken with the JEDEC low effective thermal conductivity test board.

- (2) This data was taken with the JEDEC standard multilayer test boards.

### **ESD, Electrostatic Discharge Protection**

| Symbol | Parameter Condition      |                                       | Minimum Level | Unit |

|--------|--------------------------|---------------------------------------|---------------|------|

| НВМ    | Human Body Model ESD     | ANSI/ESDA/JEDEC JS-001(1)             | 2000          | V    |

| CDM    | Charged Device Model ESD | ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | 1500          | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### **Thermal Information**

| Package Type | θ <sub>JA</sub> | θ <sub>JC</sub> | Unit |

|--------------|-----------------|-----------------|------|

| WDFN2X2-8    | TBD             | TBD             | °C/W |

www.3peak.com 6 / 16 Rev.A.1

#### **Electrical Characteristics**

All test condition is  $T_A = +25$ °C, unless otherwise noted.

| Symbol           | Parameter                               | Conditions                                                                                                | Min                      | Тур                  | Max                  | Unit |

|------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------|----------------------|----------------------|------|

| Overcharg        | ge and Shutdown Threshold               |                                                                                                           |                          | -                    |                      |      |

|                  |                                         | TA = 25°C                                                                                                 | -20                      |                      | 20                   | mV   |

| Vota             | Overcharge threshold accuracy           | TA = -20°C to 60°C                                                                                        | -25                      |                      | 25                   | mV   |

|                  |                                         | TA = -40°C to 85°C                                                                                        | -35                      |                      | 35                   | mV   |

| V <sub>HYS</sub> | Overcharge Hysteresis Voltage           |                                                                                                           |                          | -0.38                |                      | V    |

| .,               | a                                       | TA = 25°C                                                                                                 | 2.35                     | 2.50                 | 2.65                 | V    |

| V <sub>SD</sub>  | Shutdown Voltage Threshold              | TA = -40°C to 85°C                                                                                        | 2.30                     |                      | 2.70                 | V    |

| V <sub>SDR</sub> | Shutdown Release Voltage                | TA = 25°C                                                                                                 | 2.65                     | 2.80                 | 3.00                 | V    |

| V <sub>TM</sub>  | Test Mode Transition Threshold          |                                                                                                           |                          |                      | 4                    | V    |

| Input Volta      | age and Current                         |                                                                                                           |                          |                      |                      |      |

| V <sub>DD</sub>  | Operation Voltage                       |                                                                                                           | 4                        |                      | 24                   | V    |

| I <sub>DD</sub>  | Supply Current at Normal Mode           | VDD = VC1, VC4-VSS = V <sub>Cn</sub> -<br>V <sub>Cn+1</sub> = 3.8V, n = 1 to 3                            |                          |                      | 4                    | μА   |

| I <sub>SD</sub>  | Supply Current at Shutdown<br>Mode      | VDD = VC1, VC4-VSS = V <sub>Cn</sub> -<br>V <sub>Cn+1</sub> = 2V, n = 1 to 3                              |                          |                      | 0.4                  | μА   |

| Ivcn             | Input Current of VCn Pin, n = 2 to 4    | VDD = VC1, VC4-VSS = V <sub>Cn</sub> -<br>V <sub>Cn+1</sub> = 3.8V, n = 1 to 3                            |                          |                      | 0.3                  | μА   |

| IVCn             | Input Current of VC1 Pin, n = 1         |                                                                                                           |                          |                      | 2                    | μΑ   |

|                  | Input Current of CTL                    | VDD = VC1, VC4-VSS = V <sub>Cn</sub> -<br>V <sub>Cn+1</sub> = 4.0V, n = 1 to 3, V <sub>CTL</sub> =<br>16V | 1.2                      | 1.6                  | 2.4                  | μА   |

| Ість             |                                         | VDD = VC1, VC4-VSS = $V_{Cn-}$<br>$V_{Cn+1}$ = 2.0V, n = 1 to 3, $V_{CTL}$ = 8V, CTL Enable at Shutdown   | 0.6                      | 0.8                  | 1.2                  | μА   |

|                  |                                         | VDD = VC1, VC4-VSS = $V_{Cn-}$<br>$V_{Cn+1}$ = 3.8V, n = 1 to 3, $V_{CTL}$ = 8V, CTL Disable at Shutdown  | 0.35                     |                      | 0.35                 | μА   |

| Delay Time       | е                                       |                                                                                                           |                          |                      |                      |      |

| tov              | Overcharge Delay Time                   |                                                                                                           | tovx0.8                  | tov                  | tovx1.2              |      |

| t <sub>OVR</sub> | Overcharge Release Time                 |                                                                                                           | 12.8                     | 16                   | 19.2                 | ms   |

| tsD              | Shutdown Delay Time                     |                                                                                                           | t <sub>SD</sub> x0.8     | t <sub>SD</sub>      | t <sub>SD</sub> x1.2 |      |

| t <sub>TR</sub>  | Overcharge Delay Timer Reset Delay Time |                                                                                                           |                          | 0.38                 |                      | ms   |

| tovF             | Overcharge Delay Time in Test<br>Mode   |                                                                                                           | 0.8/128 ×t <sub>OV</sub> | $\frac{1}{128}$ ×tov | 1.2 ×t <sub>OV</sub> |      |

| t <sub>tst</sub> | Transition Time to Test Mode            |                                                                                                           |                          |                      | 40                   | ms   |

| tстL             | CTL Pin Response Time                   |                                                                                                           |                          |                      | 3                    | ms   |

\*Note: (1) 100% tested at TA=25°C.

### **Electrical Characteristics (Continued)**

All test condition is  $T_A$  = +25°C, unless otherwise noted.

| Symbol             | Parameter                   | Conditions                                                                                               | Min                         | Тур                         | Max                 | Unit |  |  |  |

|--------------------|-----------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------|---------------------|------|--|--|--|

| COUT Out           | COUT Output Voltage         |                                                                                                          |                             |                             |                     |      |  |  |  |

| V <sub>COL</sub>   | COUT Pin ON Voltage         | $I_{OL} = 50\mu A, VDD = VC1,$<br>$VC4-VSS = V_{Cn}-V_{Cn+1} =$<br>$V_{OV} - 0.1V, n = 1 \text{ to } 3$  |                             | 0.08                        | 0.5                 | V    |  |  |  |

| V <sub>C</sub> OH1 | COUT Pin ON Voltage 1       | $I_{OH} = -1\mu A$ , VDD = VC1,<br>VC4-VSS = V <sub>Cn</sub> -V <sub>Cn+1</sub> = 4.7V, n = 1 to 3       | 4.0                         | 4.7                         | 5.4                 | V    |  |  |  |

| V <sub>COH2</sub>  | COUT Pin ON Voltage 2       | I <sub>OH</sub> = -1mA, VDD = VC1,<br>VC4-VSS = V <sub>Cn</sub> -V <sub>Cn+1</sub> =<br>4.7V, n = 1 to 3 | V <sub>COH1</sub> —<br>0.5V | V <sub>COH1</sub> –<br>0.1V |                     | V    |  |  |  |

| Voltage Re         | egulator Output             |                                                                                                          |                             |                             |                     |      |  |  |  |

| V <sub>OUT</sub>   | VR Output Voltage           | V <sub>DD</sub> = 5.1V to 25V. I <sub>OUT</sub> = 10μA                                                   | 2.94                        | 3.0                         | 3.06                | V    |  |  |  |

| Іоит               | VR Output Current           | V <sub>DD</sub> = 5.1V to 25V                                                                            |                             |                             | 2                   | mA   |  |  |  |

| CTL Input          | CTL Input Voltage           |                                                                                                          |                             |                             |                     |      |  |  |  |

| ViH                | CTL Pin Input Voltage, High |                                                                                                          | V <sub>DD</sub> -0.         |                             |                     | V    |  |  |  |

| VIL                | CTL Pin Input Voltage, Low  |                                                                                                          |                             |                             | V <sub>DD</sub> -2. | V    |  |  |  |

<sup>\*</sup>Note: (1) 100% tested at T<sub>A</sub> = 25°C.

www.3peak.com 8 / 16 Rev.A.1

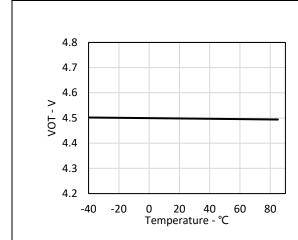

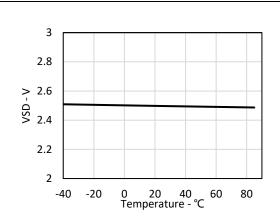

### **Typical Performance Characteristics**

All test condition: TA = +25°C, unless otherwise noted.

Figure 1 Overvoltage Threshold (4.5V) vs Temperature

Figure 2 Shutdown Voltage Threshold  $V_{\text{SD}}$  vs Temperature

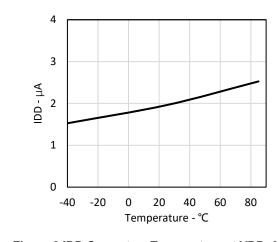

Figure 3 IDD Current vs Temperature at VDD=3.8V

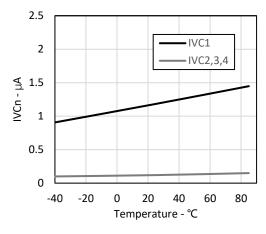

Figure 4 IVCn vs Temperature

### **Detailed Description**

#### Overview

The TPB7462 series is a secondary overcharge hardware protector for 2s, 3s, or 4s lithium-ion battery packs. It provides high accuracy overcharge threshold to avoid the safety risk from battery pack. It also provides the CTL pin to directly control output or connect PTC (Positive Temperature Coefficient) resistor to monitor overtemperature of battery pack.

The TPB7462 integrates a LDO for powering external circuit with extremely low leakage current.

#### **Feature Description**

#### **Overcharge Detection**

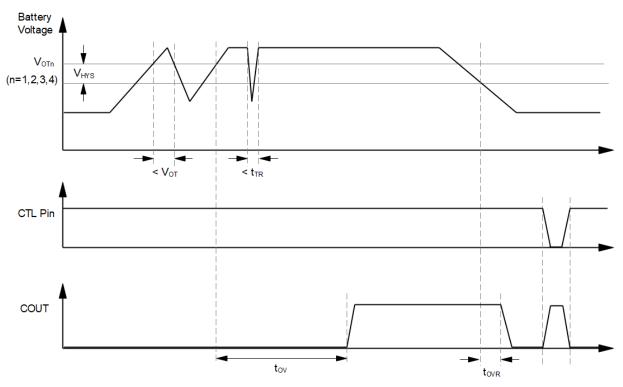

The TPB7462 monitors VC1 to VC2, VC2 to VC3, VC3 to VC4, and VC4 to VSS voltage for over voltage protection. When the voltage of any cell exceeds VoT during charging and lasts for equal to or longer than overcharge delay time (tov), COUT pin turns to H. This is called overcharge protection mode. COUT pin drives the connecting FET to provide charge control and a second protection.

Once all the cell voltages are lower than  $V_{OT}$  +  $V_{HYS}$  and last for overcharge release time ( $t_{OVR}$ ), the overcharge is released, COUT pin turns to L, the TPB7462 enters normal state.

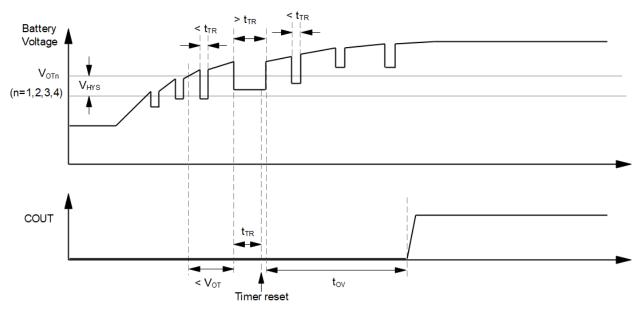

#### **Overcharge Timer Reset**

When an overcharge release noise that forces all the cell voltages temporarily below the overcharge detection voltage ( $V_{OT}$ ) during the overcharge delay time ( $t_{OV}$ ) counting period, the overcharge delay time will be continuously counted if the period of overcharge release noise is shorter than the overcharge delay timer reset time ( $t_{TR}$ ). Otherwise, counting of  $t_{OV}$  will be reset if the period of overcharge release noise is equal to or longer than  $t_{TR}$ . After that, when  $V_{OT}$  has been exceeded, counting  $t_{OV}$  resumes. Disabling of overcharge timer reset function is user selectable.

#### **Shutdown Detection**

The TPB7462 monitors VC1 to VC2, VC2 to VC3, VC3 to VC4, and VC4 to VSS voltage for shutdown protection. When all the cell voltages are less than the  $V_{SD}$  during discharging and last for equal to or longer than shutdown delay time ( $t_{SD}$ ), VOUT pin turns to L. Once the voltage of any cell exceeds  $V_{SDR}$ , TPB7462 enters normal mode and VOUT pin becomes to H.

#### **CTL Function**

The TPB7462 has a CTL pin to control the output of the COUT.

Table 1. Control via CTL Pin

| CTL pin    | COUT         |              |  |  |  |

|------------|--------------|--------------|--|--|--|

|            | Active High  | Active Low   |  |  |  |

| "H"        | Normal state | Normal state |  |  |  |

| "Open"     | "H"          | "L"          |  |  |  |

| "L"        | "H"          | "L"          |  |  |  |

| "L" to "H" |              |              |  |  |  |

| "H" to "L" |              |              |  |  |  |

www.3peak.com 10 / 16 Rev.A.1

COUT output active high/low is user selectable. Enabling/ disabling of CTL control function in the shutdown state is user selectable.

#### **Timing**

Overcharge detection

Figure 5 Timing for Overcharge

#### Overcharge Timer Reset

Figure 6 Timing for Overcharge Timer Reset

www.3peak.com 11 / 16 Rev.A.1

### **Application and Implementation**

#### NOTE

Information in the following applications sections is not part of the 3PEAK's component specification and 3PEAK does not warrant its accuracy or completeness. 3PEAK's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### **Application Information**

The TPB7462 series monitors the overcharge voltage of battery for 2s, 3s, or 4s lithium-ion battery packs and controls the charging path through COUT when overcharge is detected. It also provides the CTL pin to directly control output or connect PTC resistor to monitor temperature of battery packs. The TPB7462 returns to normal state when abnormal events are disappeared.

#### **Typical Application**

Figure 7 shows the typical application schematic of the TPB7462.

Figure 7 TPB7462 Typical Application Circuit

| Symbol                                                                             | Description                                                                        | Recommend Value | Unit |  |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------|------|--|

| R <sub>1</sub> , R <sub>2</sub> , R <sub>3</sub> , R <sub>4</sub>                  | R <sub>2</sub> , R <sub>3</sub> , R <sub>4</sub> Voltage monitor filter resistor 1 |                 | kΩ   |  |

| C <sub>P</sub> , C <sub>1</sub> , C <sub>2</sub> , C <sub>3</sub> , C <sub>4</sub> | Voltage monitor filter capacitor                                                   | 0.1             | μF   |  |

| R <sub>P</sub>                                                                     | Supply voltage filter resistor                                                     | 100             | Ω    |  |

| СР                                                                                 | Supply voltage filter capacitor                                                    | 0.1             | μF   |  |

| CVOUT Regulator output capacitor                                                   |                                                                                    | 0.1             | μF   |  |

### Layout

#### **Layout Guideline**

Both filter capacitors and output capacitor must be placed to the device pins as close as possible.

It is recommended to use wide trace lengths or thick copper weight to minimize I×R drop and heat dissipation.

Exposed pad must be connected to the PCB ground plane directly, the copper area must be as large as possible. To get the best thermal performance, thermal vis should be placed under and around the exposed pad with enough number and size.

www.3peak.com 12 / 16 Rev.A.1

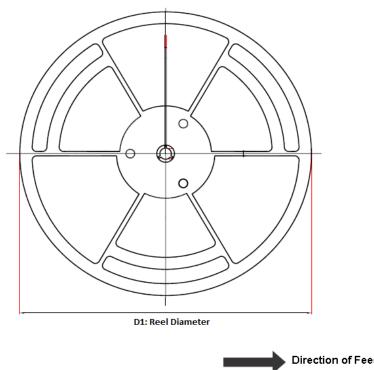

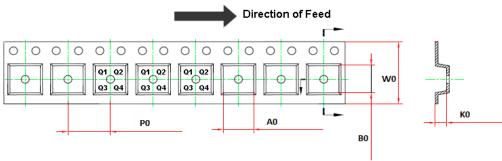

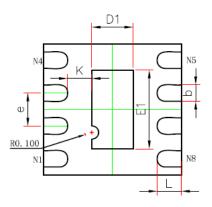

## **Tape and Reel Information**

| Order Number    | Package  | D1<br>(mm) | W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | W0<br>(mm) | Pin1<br>Quadrant |

|-----------------|----------|------------|------------|------------|------------|------------|------------|------------|------------------|

| TPB7462GGA-DFGR | DFN2X2-8 | 180        | 13.1       | 2.3        | 2.3        | 1.1        | 4          | 8          | Q1               |

www.3peak.com 13 / 16 Rev.A.1

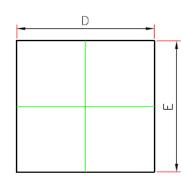

# Package Outline Dimensions DFN2X2-8

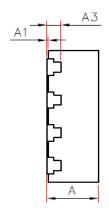

SIDE VIEW

TOP VIEW

BOTTOM VIEW

| Symbol | Dimensions In | n Millimeters | Dimensions In Inches |       |       |  |

|--------|---------------|---------------|----------------------|-------|-------|--|

| Symbol | Min.          | Max.          | Min.                 | Max.  |       |  |

| Α      | 0.700         | 0.800         | 0.028                | 0.031 |       |  |

| A1     | 0.000         | 0.050         | 0.000                | 0.002 |       |  |

| A3     | 0.203         | REF.          | 0.008                | REF.  |       |  |

| D      | 1.900         | 2.100         | 0.075                | 0.083 |       |  |

| E      | 1.900         | 2.100         | 0.075                | 0.083 |       |  |

| D1     | 0.500         | 0.700         | 0.020                | 0.028 |       |  |

| E1     | 1.100         | 1.100 1.300   | 1.300                | 0.043 | 0.051 |  |

| k      | 0.350         | REF.          | 0.014                | REF.  |       |  |

| b      | 0.200 0.300   |               | 0.008                | 0.012 |       |  |

| е      | 0.500         | BSC.          | 0.020BSC.            |       |       |  |

| Ĺ      | 0.274         | 0.426         | 0.011                | 0.017 |       |  |

### **Order Information**

| Order Number    | Operating Temperature<br>Range | Package  | Marking<br>Information | MSL | Transport Media,<br>Quantity | Eco Plan |

|-----------------|--------------------------------|----------|------------------------|-----|------------------------------|----------|

| TPB7462GGA-DFGR | −40 to 85°C                    | DFN2X2-8 | 2NA                    | 3   | Tape and Reel, 3000          | Green    |

**Green:** 3PEAK defines "Green" to mean RoHS compatible and free of halogen substances.

#### IMPORTANT NOTICE AND DISCLAIMER

Copyright© 3PEAK 2012-2023. All rights reserved.

**Trademarks.** Any of the 思瑞浦 or 3PEAK trade names, trademarks, graphic marks, and domain names contained in this document /material are the property of 3PEAK. You may NOT reproduce, modify, publish, transmit or distribute any Trademark without the prior written consent of 3PEAK.

**Performance Information.** Performance tests or performance range contained in this document/material are either results of design simulation or actual tests conducted under designated testing environment. Any variation in testing environment or simulation environment, including but not limited to testing method, testing process or testing temperature, may affect actual performance of the product.

**Disclaimer.** 3PEAK provides technical and reliability data (including data sheets), design resources (including reference designs), application or other design recommendations, networking tools, security information and other resources "As Is". 3PEAK makes no warranty as to the absence of defects, and makes no warranties of any kind, express or implied, including without limitation, implied warranties as to merchantability, fitness for a particular purpose or non-infringement of any third-party's intellectual property rights. Unless otherwise specified in writing, products supplied by 3PEAK are not designed to be used in any life-threatening scenarios, including critical medical applications, automotive safety-critical systems, aviation, aerospace, or any situations where failure could result in bodily harm, loss of life, or significant property damage. 3PEAK disclaims all liability for any such unauthorized use.

www.3peak.com 16 / 16 Rev.A.1