### Features

- 16-bit, 4-channel ADC with Integrated Analog Frontend

- Sampling with 500 KSPS throughput Rate

- Independently Programmable Channel Inputs

- True Bipolar Single-ended: ±12.288 V, ±10.24 V, ±6.144 V, ±5.12 V, ±3.072 V, ±2.56 V

- Unipolar Single-ended: 0 V 12.288 V, 0 V 10.24

V, 0 V 6.144 V, 0 V 5.12 V

- True Bipolar Fully-differential: ±12.288 V, ±10.24 V, ±6.144 V, ±5.12 V

- Configurable Analog Bandwidth: 15 kHz or 35 kHz

- Power Supply

- Single Analog Supply: 5 V

- Digital Supply: 1.71 V to 5 V

- Highly Integrated Analog Front-end

- 1-MΩ Analog Input Impedance

- Programmable Gain Amplifier

- Analog Low-pass Filter

- Internal Accurate Reference and Reference Buffer

- ±30 V Analog Input Overvoltage Clamp Protection with 8-kV ESD

- Flexible Digital and Interface

- Serial Interface Compatible with SPI

- Daisy-chain Function

- Channel Sequencer

- Integrated Diagnostic Function

- Analog Input Open Detect with Manual or Auto Mode

- Optional Cyclic Redundancy Check (CRC) Error Checking

- AUX Input with Direct Connection to ADC Inputs

- Typical Performance

- DNL: ±0.5 LSB

- INL: ±1 LSB

- SNR: 90.5 dB

- SINAD: 90 dB

- THD: -103 dB

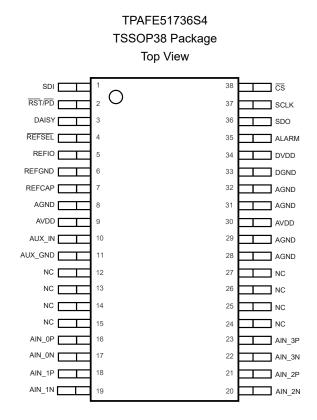

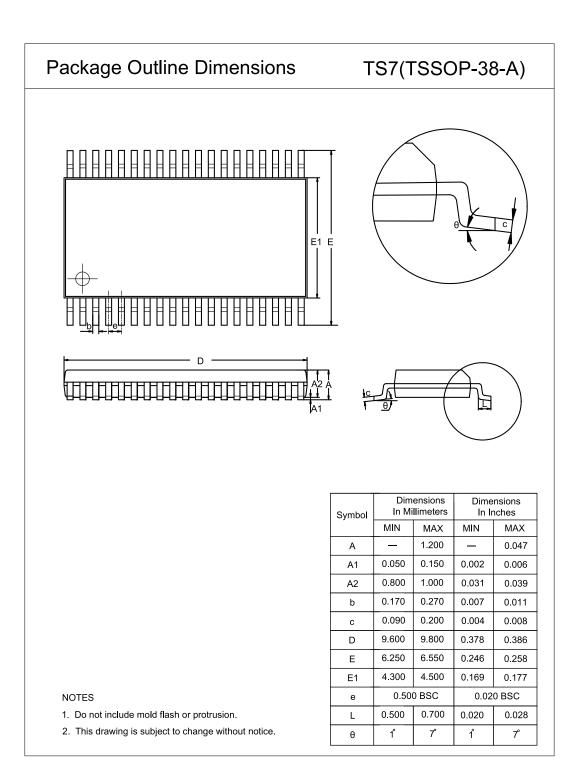

- Package: TSSOP38 Package

- Wide Operating Temperature Range: -40°C to +125°C

### Applications

- Analog Input Modules

- Relay Protection

- Multi-channel Data Acquisition

### Description

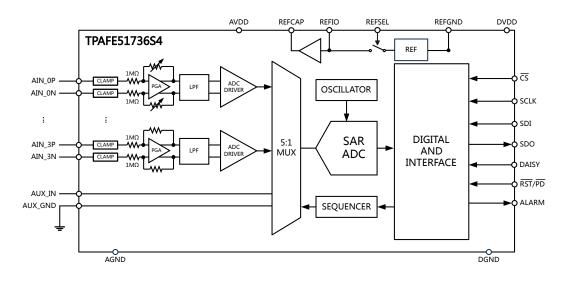

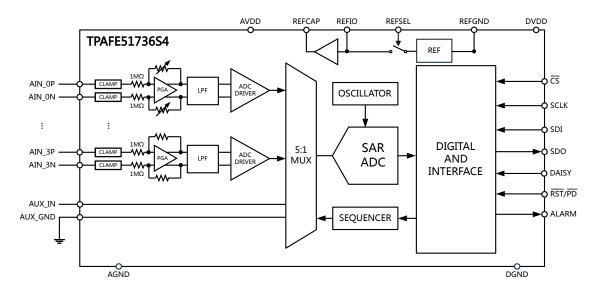

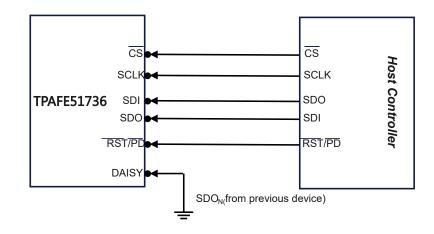

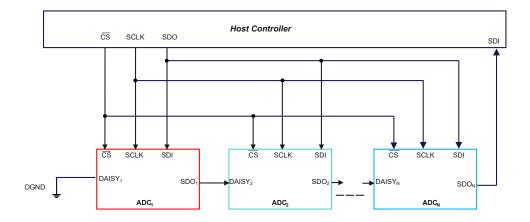

The TPAFE51736S4 is a 4-channel, 16-bit, 500 kSPS sampling system based on a successive approximation register (SAR) analog-to-digital converter (ADC). The TPAFE51736S4 is highly integrated with an analog frontend for each channel, including an input overvoltage clamp, 1 M $\Omega$  input impedance, programmable gain amplifier (PGA), active low-pass filter, and ADC driver. Internal precision and low-drift reference with buffer make the device feasible for a compact data acquisition solution. The digital interface supports communication with various host controllers with SPI-compatible serial and daisy-chaining of multiple devices.

The TPAFE51736S4 can process true bipolar single-ended ±12.288 V, ±10.24 V, ±6.144 V, ±5.12 V, ±3.072 V, ±2.56 V, unipolar single-ended 0 V - 12.288 V, 0 V - 10.24 V, 0 V - 6.144 V, 0 V - 5.12 V, and true bipolar fully-differential ±12.288 V, ±10.24 V, ±6.144 V, ±5.12 V input signals, with single 5 V analog power supply. The 1 M $\Omega$  high input impedance simplified analog input design, and the device can be connected directly to sensors. The analog input overvoltage can protect the device up to ±30 V. The device offers a simple SPI-compatible serial interface and also supports daisy-chaining of multiple devices.

The device integrates various diagnostic functions to improve system robustness, like analog input open detection and CRC error checking on read and write data and registers.

The TPAFE51736S4 is available in the 38-lead TSSOP 9.7 mm x 4.4 mm package and operates from  $-40^{\circ}$ C to  $+125^{\circ}$ C.

# **Functional Block Diagram**

## **Table of Contents**

| Features                                                     | 1  |

|--------------------------------------------------------------|----|

| Applications                                                 | 1  |

| Description                                                  | 1  |

| Functional Block Diagram                                     | 2  |

| Product Family Table                                         | 5  |

| Revision History                                             | 5  |

| Pin Configuration and Functions                              | 6  |

| Specifications                                               | 8  |

| Absolute Maximum Ratings <sup>(1)</sup>                      | 8  |

| ESD, Electrostatic Discharge Protection                      | 8  |

| Recommended Operating Conditions                             | 8  |

| Thermal Information                                          | 8  |

| Electrical Characteristics                                   | 9  |

| Timing Requirements <sup>(1)</sup>                           | 16 |

| Typical Performance Characteristics                          | 18 |

| Detailed Description                                         | 23 |

| Overview                                                     | 23 |

| Functional Block Diagram                                     | 23 |

| Feature Description                                          | 24 |

| Device Functional Modes                                      | 30 |

| Register Maps                                                | 42 |

| Command Registers                                            | 43 |

| Program Registers                                            | 45 |

| Program Registers Map                                        | 47 |

| Auto-Scan Sequence Enable Register (address = 01h)           | 51 |

| Channel Power Down Register (address = 02h)                  | 52 |

| Device Features Selection Control Register (address = 03h)   | 54 |

| Range Select Registers (addresses 05h-0Ch)                   | 56 |

| Over Range Setting Registers (address 0Dh)                   | 57 |

| LPF Bandwidth Configuration Registers (address 0Eh)          | 58 |

| CRC Configure Register (address = 0Fh)                       | 59 |

| Alarm Overview Tripped-flag Register (address = 10h)         | 59 |

| Alarm Flag Registers: Tripped and Active (address = 11h-14h) | 60 |

| Alarm Threshold Setting Registers (addresses = 15h-3Ch)      | 61 |

| Command Read-Back Register (address = 3Fh)                   | 64 |

| Open Detect Enable Register (address = 78h)                  | 65 |

| Open Detected Register (address = 79h)         | 66 |

|------------------------------------------------|----|

| Open Detect Mode Register (address = 7Ah)      | 67 |

| Open Detect Threshold Register (address = 7Bh) | 67 |

| Status Register (address = 7Dh)                | 67 |

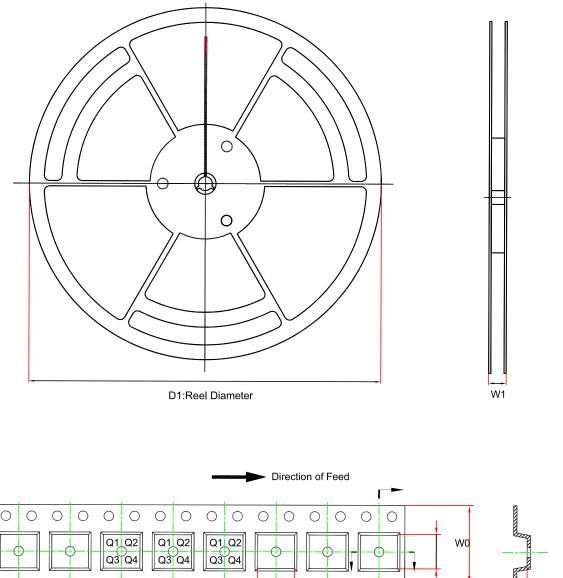

| Tape and Reel Information                      | 68 |

| Package Outline Dimensions                     | 69 |

| TSSOP38                                        | 69 |

| Order Information                              | 70 |

| IMPORTANT NOTICE AND DISCLAIMER                | 71 |

# Product Family Table

| Order Number      | Channels | Resolution | Throughput | Package |

|-------------------|----------|------------|------------|---------|

| TPAFE51736S4-TS7R | 4        | 16 Bits    | 500 kSPS   | TSSOP38 |

# **Revision History**

| Date       | Revision | Notes                    |

|------------|----------|--------------------------|

| 2024-12-26 | Rev.A.0  | Initial released version |

### **Pin Configuration and Functions**

|                   | Pin    | <b>T</b> urne (1)   | Description                                                                                                                                                                                                                                                                |

|-------------------|--------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.               | Name   | Type <sup>(1)</sup> | Description                                                                                                                                                                                                                                                                |

| 1                 | SDI    | DI                  | Data input of the SPI interface                                                                                                                                                                                                                                            |

| 2                 | RST/PD | DI                  | Hardware RST/PD with low logic input active.<br>This pin can perform a reset or power-down function depending on the low input<br>duration.                                                                                                                                |

| 3                 | DAISY  | DI                  | Chain the data input during daisy-chain mode                                                                                                                                                                                                                               |

| 4                 | REFSEL | DI                  | Active low logic input to enable the internal reference. When this pin is low, the internal reference is enabled and REFIO acts as an output pin. When this pin is high, the internal reference is enabled and REFIO acts as an input pin to apply the external input REF. |

| 5                 | REFIO  | AIO                 | External reference input pin and internal reference output pin                                                                                                                                                                                                             |

| 6                 | REFGND | Р                   | Reference ground pin. Connect this pin to AGND.                                                                                                                                                                                                                            |

| 7                 | REFCAP | AO                  | Reference buffer output pin. Decouple this pin to AGND using capacitor. The voltage on this pin is typically 4.096 V.                                                                                                                                                      |

| 8,28,29,<br>31,32 | AGND   | Ρ                   | Analog ground pins.                                                                                                                                                                                                                                                        |

| 9, 30             | AVDD   | Р                   | Analog supply pins.                                                                                                                                                                                                                                                        |

|     | Pin     | - (1)               |                                                                             |

|-----|---------|---------------------|-----------------------------------------------------------------------------|

| No. | Name    | Type <sup>(1)</sup> | Description                                                                 |

| 10  | AUX_INP | AI                  | Auxiliary input channel: positive input.                                    |

| 11  | AUX_GND | AI                  | Auxiliary input channel: negative input.                                    |

| 12  | NC      | AI                  | Leave this pin floating or connected to AGND.                               |

| 13  | NC      | AI                  | Leave this pin floating or connected to AGND.                               |

| 14  | NC      | AI                  | Leave this pin floating or connected to AGND.                               |

| 15  | NC      | AI                  | Leave this pin floating or connected to AGND.                               |

| 16  | AIN_0P  | AI                  | Positive analog input for channel 0.                                        |

| 17  | AIN_0N  | AI                  | Negative analog input for channel 0.                                        |

| 18  | AIN_1P  | AI                  | Positive analog input for channel 1.                                        |

| 19  | AIN_1N  | AI                  | Negative analog input for channel 1.                                        |

| 20  | AIN_2N  | AI                  | Negative analog input for channel 2.                                        |

| 21  | AIN_2P  | AI                  | Positive analog input for channel 2.                                        |

| 22  | AIN_3N  | AI                  | Negative analog input for channel 3.                                        |

| 23  | AIN_3P  | AI                  | Positive analog input for channel 3.                                        |

| 24  | NC      | AI                  | Leave this pin floating or connected to AGND.                               |

| 25  | NC      | AI                  | Leave this pin floating or connected to AGND.                               |

| 26  | NC      | AI                  | Leave this pin floating or connected to AGND.                               |

| 27  | NC      | AI                  | Leave this pin floating or connected to AGND.                               |

| 34  | DVDD    | Р                   | Digital supply pins.                                                        |

| 35  | ALARM   | DO                  | ALARM function output. This pin can be float if alarm function is disabled. |

| 36  | SDO     | DO                  | This pin outputs serial conversion data.                                    |

| 37  | SCLK    | DI                  | This pin acts as the serial clock input for data transfers.                 |

| 38  | CS      | DI                  | Active low logic input; chip-select signal                                  |

(1) AI is analog input, GND is ground, P is power supply, REF is reference input/output, DI is digital input, DO is digital output, and CAP is decoupling capacitor pin.

## **Specifications**

### Absolute Maximum Ratings <sup>(1)</sup>

|                                            | Parameter                                    | Min  | Мах          | Unit |

|--------------------------------------------|----------------------------------------------|------|--------------|------|

|                                            | Analog Input Voltage (AINxP or AINxN) to GND | -30  | +30          | V    |

| Analog Voltage                             | AUX_IN to GND                                | -0.3 | AVDD + 0.3 V | V    |

|                                            | REFCAP or REFIO to REFGND                    | -0.3 | AVDD + 0.3 V | V    |

| Digital Voltage                            | Digital Input Voltage to GND                 | -0.3 | DVDD + 0.3 V | V    |

|                                            | Digital Output Voltage to GND                | -0.3 | DVDD + 0.3 V | V    |

| Our relative to the second                 | AVDD to GND                                  | -0.3 | 7            | V    |

| Supply Voltage                             | DVDD to GND                                  | -0.3 | AVDD + 0.3 V | V    |

| TJ Maximum Junction Temperature            |                                              |      | 150          | °C   |

| T <sub>A</sub> Operating Temperature Range |                                              | -40  | 125          | °C   |

| T <sub>STG</sub>                           | Storage Temperature Range                    | -65  | 150          | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

### **ESD**, Electrostatic Discharge Protection

| Symbol | Parameter                |                   | Condition                             | Minimum Level | Unit |

|--------|--------------------------|-------------------|---------------------------------------|---------------|------|

|        | BM Human Body Model ESD  | Analog input pins | ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±8            | kV   |

| HBM    |                          | All other pins    | ANSI/ESDA/JEDEC JS-001                | ±4            | kV   |

| CDM    | Charged Device Model ESD | -<br>-            | ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ±1            | kV   |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **Recommended Operating Conditions**

| Parameter |                        |      | Тур | Max  | Unit |

|-----------|------------------------|------|-----|------|------|

| AVDD      | Analog Supply Voltage  | 4.75 | 5   | 5.25 | V    |

| DVDD      | Digital Supply Voltage | 1.71 | 3.3 | AVDD | V    |

### **Thermal Information**

| Package Type | θ <sub>JA</sub> | θյς  | Unit |

|--------------|-----------------|------|------|

| TSSOP38      | 68.8            | 19.9 | °C/W |

### **Electrical Characteristics**

All test conditions: AVDD = 5 V,  $V_{REF}$  = 4.096 V (internal), DVDD = 3 V,  $f_{SAMPLE}$  = 500 kSPS,  $T_A$  = -40 °C to 125 °C, unless otherwise noted.

| Parameter                                                                              | Test Conditions                         | Min                          | Тур                   | Max                      | Unit |  |

|----------------------------------------------------------------------------------------|-----------------------------------------|------------------------------|-----------------------|--------------------------|------|--|

| Analog Inputs                                                                          |                                         | 1                            |                       |                          |      |  |

|                                                                                        | Input range = ±3 × V <sub>REF</sub>     | -3 × V <sub>REF</sub>        |                       | 3 × V <sub>REF</sub>     |      |  |

|                                                                                        | Input range = ±2.5 × V <sub>REF</sub>   | -2.5 × V <sub>REF</sub>      |                       | 2.5 × V <sub>REF</sub>   |      |  |

|                                                                                        | Input range = ±1.5 × V <sub>REF</sub>   | −1.5 × V <sub>REF</sub>      |                       | 1.5 × V <sub>REF</sub>   |      |  |

|                                                                                        | Input range = ±1.25 × V <sub>REF</sub>  | -1.25 × V <sub>REF</sub>     |                       | 1.25 × V <sub>REF</sub>  | F    |  |

|                                                                                        | Input range = ±0.75 × V <sub>REF</sub>  | -0.75 × V <sub>REF</sub>     |                       | 0.75 × V <sub>REF</sub>  |      |  |

| Input V <sub>IN</sub> Voltage Ranges <sup>(1)</sup><br>V <sub>IN</sub> = AINxP - AINxN | Input range = ±0.625 × V <sub>REF</sub> | -0.625 ×<br>V <sub>REF</sub> |                       | 0.625 × V <sub>REF</sub> | V    |  |

|                                                                                        | Input range = 3 × V <sub>REF</sub>      | 0                            |                       | 3 × V <sub>REF</sub>     |      |  |

|                                                                                        | Input range = 2.5 × V <sub>REF</sub>    | 0                            |                       | 2.5 × V <sub>REF</sub>   |      |  |

|                                                                                        | Input range = 1.5 × V <sub>REF</sub>    | 0                            |                       | 1.5 × V <sub>REF</sub>   |      |  |

|                                                                                        | Input range = 1.25 × V <sub>REF</sub>   | 0                            |                       | 1.25 × V <sub>REF</sub>  |      |  |

|                                                                                        | Input range = ±3 × V <sub>REF</sub>     | -3 × V <sub>REF</sub>        | -3 × V <sub>REF</sub> | 3 × V <sub>REF</sub>     |      |  |

|                                                                                        | Input range = ±2.5 × V <sub>REF</sub>   | -2.5 × V <sub>REF</sub>      |                       | 2.5 × V <sub>REF</sub>   |      |  |

|                                                                                        | Input range = ±1.5 × V <sub>REF</sub>   | −1.5 × V <sub>REF</sub>      |                       | 1.5 × V <sub>REF</sub>   |      |  |

|                                                                                        | Input range = ±1.25 × V <sub>REF</sub>  | -1.25 × V <sub>REF</sub>     |                       | 1.25 × V <sub>REF</sub>  |      |  |

| AIN_xP                                                                                 | Input range = ±0.75 × V <sub>REF</sub>  | -0.75 × V <sub>REF</sub>     |                       | 0.75 × V <sub>REF</sub>  |      |  |

| Operating Input Range,<br>Positive Input <sup>(1)</sup>                                | Input range = ±0.625 × V <sub>REF</sub> | -0.625 ×<br>V <sub>REF</sub> |                       | 0.625 × V <sub>REF</sub> | V    |  |

|                                                                                        | Input range = 3 × V <sub>REF</sub>      | 0                            |                       | 3 × V <sub>REF</sub>     |      |  |

|                                                                                        | Input range = 2.5 × V <sub>REF</sub>    | 0                            |                       | 2.5 × V <sub>REF</sub>   |      |  |

|                                                                                        | Input range = 1.5 × V <sub>REF</sub>    | 0                            |                       | 1.5 × V <sub>REF</sub>   |      |  |

|                                                                                        | Input range = 1.25 × V <sub>REF</sub>   | 0                            |                       | 1.25 × V <sub>REF</sub>  |      |  |

|                                                                                        | Input range = ±3 × V <sub>REF</sub>     | -3 × V <sub>REF</sub>        |                       | 3 × V <sub>REF</sub>     |      |  |

|                                                                                        | Input range = ±2.5 × V <sub>REF</sub>   | −2.5 × V <sub>REF</sub>      |                       | 2.5 × V <sub>REF</sub>   |      |  |

|                                                                                        | Input range = ±1.5 × V <sub>REF</sub>   | −1.5 × V <sub>REF</sub>      |                       | 1.5 × V <sub>REF</sub>   |      |  |

|                                                                                        | Input range = ±1.25 × V <sub>REF</sub>  | −1.25 × V <sub>REF</sub>     |                       | 1.25 × V <sub>REF</sub>  |      |  |

| AIN_xN                                                                                 | Input range = ±0.75 × V <sub>REF</sub>  | -0.75 × V <sub>REF</sub>     |                       | 0.75 × V <sub>REF</sub>  |      |  |

| Operating Input Range,<br>Negative Input <sup>(1)</sup>                                | Input range = ±0.625 × V <sub>REF</sub> | -0.625 ×<br>V <sub>REF</sub> |                       | 0.625 × V <sub>REF</sub> | V    |  |

|                                                                                        | Input range = 3 × V <sub>REF</sub>      | -0.1                         |                       | 0.1                      |      |  |

|                                                                                        | Input range = 2.5 × V <sub>REF</sub>    | -0.1                         |                       | 0.1                      |      |  |

|                                                                                        | Input range = 1.5 × V <sub>REF</sub>    | -0.1                         |                       | 0.1                      |      |  |

|                                                                                        | Input range = 1.25 × V <sub>REF</sub>   | -0.1                         |                       | 0.1                      |      |  |

| F                                                                                | Parameter                            | Test Conditions                                        | Min                          | Тур   | Max                      | Unit   |

|----------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------------------|------------------------------|-------|--------------------------|--------|

|                                                                                  |                                      | Input range = ±3 × V <sub>REF</sub>                    | -3 × V <sub>REF</sub>        |       | 3 × V <sub>REF</sub>     |        |

|                                                                                  |                                      | Input range = ±2.5 × V <sub>REF</sub>                  | -2.5 × V <sub>REF</sub>      |       | 2.5 × V <sub>REF</sub>   |        |

|                                                                                  |                                      | Input range = ±1.5 × V <sub>REF</sub>                  | −1.5 × V <sub>REF</sub>      |       | 1.5 × V <sub>REF</sub>   | ]      |

| Fully Differential Input Range <sup>(1)</sup><br>V <sub>IN</sub> = AINxP - AINxN |                                      | Input range = ±1.25 × V <sub>REF</sub>                 | -1.25 × V <sub>REF</sub>     |       | 1.25 × V <sub>REF</sub>  | V      |

|                                                                                  |                                      | Input range = ±0.75 × V <sub>REF</sub>                 | -0.75 × V <sub>REF</sub>     |       | 0.75 × V <sub>REF</sub>  |        |

|                                                                                  |                                      | Input range = ±0.625 × V <sub>REF</sub>                | -0.625 ×<br>V <sub>REF</sub> |       | 0.625 × V <sub>REF</sub> |        |

|                                                                                  |                                      | Input range = ±3 × V <sub>REF</sub>                    | -6.8                         |       | 6.5                      |        |

|                                                                                  |                                      | Input range = ±2.5 × V <sub>REF</sub>                  | -6.8                         |       | 6.5                      |        |

| Fully Different                                                                  | ial Input                            | Input range = ±1.5 × V <sub>REF</sub>                  | -3.4                         |       | 4.9                      |        |

| Common-Mod                                                                       | le Input Range <sup>(1)</sup>        | Input range = ±1.25 × V <sub>REF</sub>                 | -3.4                         |       | 4.9                      | V      |

|                                                                                  |                                      | Input range = ±0.75 × V <sub>REF</sub>                 | -1.7                         |       | 4.1                      |        |

|                                                                                  |                                      | Input range = ±0.625 × V <sub>REF</sub>                | -1.7                         |       | 4.1                      |        |

|                                                                                  | Input Impedance                      | All input ranges, T <sub>A</sub> = 25°C                | 0.85                         | 1     | 1.17                     | Mohm   |

| Z <sub>IN</sub>                                                                  | Input Impedance<br>Temperature Drift | All input ranges                                       |                              | 7     |                          | ppm/°C |

|                                                                                  | Input Leakage<br>Current             | Input range = ±2.5 × V <sub>REF</sub>                  |                              | 8.8   |                          |        |

|                                                                                  |                                      | Input range = ±1.25 × V <sub>REF</sub>                 |                              | 3.3   |                          | μA     |

| Analog Input<br>Current                                                          |                                      | Input range = ±0.625 × V <sub>REF</sub>                |                              | 1.1   |                          |        |

| Guilent                                                                          |                                      | Input range = 2.5 × V <sub>REF</sub>                   |                              | 9.2   |                          |        |

|                                                                                  |                                      | Input range = 1.25 × V <sub>REF</sub>                  |                              | 4.3   |                          |        |

| Input Overvo                                                                     | Itage Protection <sup>(1)</sup>      | 1                                                      | 1 1                          |       | 1                        |        |

| Analog Input<br>Clamp                                                            | Overvoltage<br>Protection Voltage    | All input ranges                                       | -30                          |       | 30                       | v      |

| Analog Input                                                                     | Filter                               | 1                                                      | 1 1                          |       | 1                        |        |

| −3 dB BW                                                                         | Analog Input LPF                     | Low bandwidth                                          |                              | 15    |                          | kHz    |

|                                                                                  | Bandwidth −3 dB                      | High bandwidth                                         |                              | 35    |                          |        |

| -0.1 dB BW                                                                       | Analog Input LPF                     | Low bandwidth                                          |                              | 2.5   |                          | kHz    |

| 0.1 00 000                                                                       | Bandwidth −0.1 dB                    | High bandwidth                                         |                              | 5.5   |                          |        |

| System Perfo                                                                     | ormance                              | 1                                                      | 1                            |       |                          |        |

| Resolution                                                                       | 1                                    |                                                        | 16                           |       |                          | Bits   |

| NMC                                                                              | No Missing Codes                     |                                                        | 16                           |       |                          | Bits   |

| DNL                                                                              | Differential<br>Nonlinearity         | All input ranges                                       | -0.99                        | ±0.5  | 1                        | LSB    |

| INL                                                                              | Integral Nonlinearity                | All input ranges                                       | -2                           | ±1    | 2                        | LSB    |

| E.                                                                               | Positive Full-scale                  | At T <sub>A</sub> = 25°C,<br>all normal input ranges   |                              | ±0.02 | ±0.05                    | %FSR   |

| E <sub>G</sub> Error                                                             | Error                                | At $T_A = 25^{\circ}C$ ,<br>all overrange input ranges |                              | ±0.02 | ±0.12                    | %FSR   |

| Parameter         |                                                                  | Test Conditions                                         | Min  | Тур    | Мах   | Unit   |  |

|-------------------|------------------------------------------------------------------|---------------------------------------------------------|------|--------|-------|--------|--|

|                   | Positive Full-scale<br>Error Matching <sup>(1)</sup>             | At $T_A = 25^{\circ}C$ ,<br>all normal input ranges     |      | ±0.02  | ±0.05 | %FSR   |  |

|                   | All Input Ranges<br>(channel-to-channel)                         | At T <sub>A</sub> = 25°C,<br>all overrange input ranges |      | ±0.02  | ±0.12 | %FSR   |  |

|                   | Positive Full-scale<br>Error Temperature<br>Drift <sup>(1)</sup> | All input ranges                                        | -5   | 1      | 5     | ppm/°C |  |

|                   |                                                                  | Input range = ±3 × V <sub>REF</sub>                     |      | ±0.375 | ±2.63 |        |  |

|                   |                                                                  | Input range = ±2.5 × V <sub>REF</sub>                   |      | ±0.32  | ±1.25 |        |  |

|                   |                                                                  | Input range = ±1.5 × V <sub>REF</sub>                   |      | ±0.56  | ±1.69 |        |  |

|                   |                                                                  | Input range = ±1.25 × V <sub>REF</sub>                  |      | ±0.47  | ±0.95 |        |  |

| _                 | Offset Error                                                     | Input range = ±0.75 × V <sub>REF</sub>                  |      | ±0.375 | ±1.41 |        |  |

| Eo                | At T <sub>A</sub> = 25°C,                                        | Input range = ±0.625 × V <sub>REF</sub>                 |      | ±0.32  | ±0.8  | mV     |  |

|                   |                                                                  | Input range = 3 × V <sub>REF</sub>                      |      | ±0.375 | ±4.59 |        |  |

|                   |                                                                  | Input range = 2.5 × V <sub>REF</sub>                    |      | ±0.32  | ±2.2  |        |  |

|                   |                                                                  | Input range = 1.5 × V <sub>REF</sub>                    |      | ±0.47  | ±4.69 |        |  |

|                   |                                                                  | Input range = 1.25 × V <sub>REF</sub>                   |      | ±0.39  | ±1.8  | 1      |  |

|                   | Offset Error Matching                                            | Input range = ±3 × V <sub>REF</sub>                     |      | ±0.375 | ±2.63 |        |  |

|                   | (1)<br>(channel to channel<br>At T <sub>A</sub> = 25°C)          | Input range = ±2.5 × V <sub>REF</sub>                   |      | ±0.32  | ±1.25 |        |  |

|                   |                                                                  | Input range = ±1.5 × V <sub>REF</sub>                   |      | ±0.56  | ±1.69 |        |  |

|                   |                                                                  | Input range = ±1.25 × V <sub>REF</sub>                  |      | ±0.47  | ±0.95 |        |  |

|                   |                                                                  | Input range = ±0.75 × V <sub>REF</sub>                  |      | ±0.375 | ±1.41 |        |  |

|                   |                                                                  | Input range = ±0.625 × V <sub>REF</sub>                 |      | ±0.32  | ±0.8  | mV     |  |

|                   |                                                                  | Input range = 3 × V <sub>REF</sub>                      |      | ±0.375 | ±4.59 |        |  |

|                   |                                                                  | Input range = 2.5 × V <sub>REF</sub>                    |      | ±0.32  | ±2.2  |        |  |

|                   |                                                                  | Input range = 1.5 × V <sub>REF</sub>                    |      | ±0.47  | ±4.69 |        |  |

|                   |                                                                  | Input range = 1.25 × V <sub>REF</sub>                   |      | ±0.39  | ±1.8  |        |  |

|                   | Offset Error<br>Temperature Drift <sup>(1)</sup>                 | All input ranges                                        | -4   | 1      | 4     | ppm/°C |  |

| Sampling          | Dynamics <sup>(1)</sup>                                          |                                                         |      |        |       |        |  |

| t <sub>CONV</sub> | Conversion Time                                                  |                                                         |      |        | 880   | ns     |  |

| t <sub>ACQ</sub>  | Acquisition Time                                                 |                                                         | 1120 |        |       | ns     |  |

| fs                | Maximum<br>Throughput Rate<br>without Latency                    |                                                         |      | 500    |       | kSPS   |  |

| Dynamic           | Characteristics                                                  |                                                         |      |        |       |        |  |

| SNR               | Low Bandwidth                                                    | Input range = ±3 × V <sub>REF</sub>                     | 87.2 | 90.5   |       |        |  |

|                   | –0.5 dBFS 1 kHz                                                  | Input range = ±2.5 × V <sub>REF</sub>                   | 86.9 | 89.9   |       | dB     |  |

|                   | Input                                                            | Input range = ±1.5 × V <sub>REF</sub>                   | 87   | 90     |       |        |  |

| Parameter |                                      | Test Conditions                         | Min  | Тур  | Мах | Unit |

|-----------|--------------------------------------|-----------------------------------------|------|------|-----|------|

|           |                                      | Input range = $\pm 1.25 \times V_{REF}$ | 86.5 | 89.4 |     |      |

|           |                                      | Input range = ±0.75 × V <sub>REF</sub>  | 86.2 | 88.9 |     |      |

|           |                                      | Input range = ±0.625 × V <sub>REF</sub> | 85.5 | 88.3 |     |      |

|           |                                      | Input range = $3 \times V_{REF}$        | 86.9 | 89.8 |     |      |

|           |                                      | Input range = 2.5 × V <sub>REF</sub>    | 86.3 | 89   |     |      |

|           |                                      | Input range = 1.5 × V <sub>REF</sub>    | 85.6 | 88.2 |     |      |

|           |                                      | Input range = 1.25 × V <sub>REF</sub>   | 84.8 | 87.1 |     |      |

|           | High Bandwidth                       | Input range = ±3 × V <sub>REF</sub>     |      | 90   |     |      |

|           | –0.5 dBFS 1 kHz                      | Input range = ±2.5 × V <sub>REF</sub>   |      | 90   |     |      |

|           | Input                                | Input range = ±1.5 × V <sub>REF</sub>   |      | 90   |     |      |

|           |                                      | Input range = ±1.25 × V <sub>REF</sub>  |      | 89   |     |      |

|           |                                      | Input range = ±0.75 × V <sub>REF</sub>  |      | 89   |     |      |

|           |                                      | Input range = ±0.625 × V <sub>REF</sub> |      | 88   |     | dB   |

|           |                                      | Input range = 3 × V <sub>REF</sub>      |      | 88   |     | _    |

|           |                                      | Input range = 2.5 × V <sub>REF</sub>    |      | 88   |     |      |

|           | Input range = 1.5 × V <sub>REF</sub> |                                         | 86   |      |     |      |

|           |                                      | Input range = 1.25 × V <sub>REF</sub>   |      | 85   |     |      |

| THD       | Low Bandwidth                        | Input range = ±3 × V <sub>REF</sub>     |      | -103 |     |      |

|           | –0.5 dBFS 1 kHz                      | Input range = ±2.5 × V <sub>REF</sub>   |      | -103 |     |      |

|           | Input                                | Input range = ±1.5 × V <sub>REF</sub>   |      | -103 |     | _    |

|           |                                      | Input range = ±1.25 × V <sub>REF</sub>  |      | -103 |     |      |

|           |                                      | Input range = ±0.75 × V <sub>REF</sub>  |      | -103 |     |      |

|           |                                      | Input range = ±0.625 × V <sub>REF</sub> |      | -103 |     | dB   |

|           |                                      | Input range = 3 × V <sub>REF</sub>      |      | -103 |     |      |

|           |                                      | Input range = 2.5 × V <sub>REF</sub>    |      | -103 |     |      |

|           |                                      | Input range = 1.5 × V <sub>REF</sub>    |      | -103 |     |      |

|           |                                      | Input range = 1.25 × V <sub>REF</sub>   |      | -103 |     |      |

|           | High Bandwidth                       | Input range = ±3 × V <sub>REF</sub>     |      | -100 |     |      |

|           | –0.5 dBFS 1 kHz                      | Input range = ±2.5 × V <sub>REF</sub>   |      | -100 |     |      |

|           | Input                                | Input range = ±1.5 × V <sub>REF</sub>   |      | -100 |     |      |

|           |                                      | Input range = ±1.25 × V <sub>REF</sub>  |      | -100 |     |      |

|           |                                      | Input range = ±0.75 × V <sub>REF</sub>  |      | -100 |     |      |

|           |                                      | Input range = ±0.625 × V <sub>REF</sub> |      | -100 |     | dB   |

|           |                                      | Input range = 3 × V <sub>REF</sub>      |      | -100 |     |      |

|           |                                      | Input range = 2.5 × V <sub>REF</sub>    |      | -100 |     |      |

|           |                                      | Input range = 1.5 × V <sub>REF</sub>    |      | -100 |     |      |

|           |                                      | Input range = 1.25 × V <sub>REF</sub>   |      | -100 |     | 1    |

| Parameter               |                                        | Test Conditions                                                       | Min   | Тур  | Max              | Unit |

|-------------------------|----------------------------------------|-----------------------------------------------------------------------|-------|------|------------------|------|

| SINAD                   | Low Bandwidth                          | Input range = ±3 × V <sub>REF</sub>                                   | 86.6  | 90   |                  |      |

|                         | –0.5 dBFS 1 kHz                        | Input range = ±2.5 × V <sub>REF</sub>                                 | 86.7  | 89.7 |                  |      |

|                         | Input                                  | Input range = ±1.5 × V <sub>REF</sub>                                 | 86.6  | 89.8 |                  |      |

|                         |                                        | Input range = ±1.25 × V <sub>REF</sub>                                | 86.3  | 89.2 |                  |      |

|                         |                                        | Input range = ±0.75 × V <sub>REF</sub>                                | 85.5  | 88.8 |                  |      |

|                         |                                        | Input range = ±0.625 × V <sub>REF</sub>                               | 84.6  | 88.2 |                  | - dB |

|                         |                                        | Input range = 3 × V <sub>REF</sub>                                    | 86.3  | 89.6 |                  |      |

|                         |                                        | Input range = 2.5 × V <sub>REF</sub>                                  | 85.7  | 88.8 |                  |      |

|                         |                                        | Input range = 1.5 × V <sub>REF</sub>                                  | 85.2  | 88.1 |                  |      |

|                         |                                        | Input range = 1.25 × V <sub>REF</sub>                                 | 84.4  | 87   |                  |      |

|                         | High Bandwidth                         | Input range = ±3 × V <sub>REF</sub>                                   |       | 89   |                  |      |

|                         | –0.5 dBFS 1 kHz                        | Input range = ±2.5 × V <sub>REF</sub>                                 |       | 89   |                  |      |

|                         | Input                                  | Input range = ±1.5 × V <sub>REF</sub>                                 |       | 89   |                  |      |

|                         |                                        | Input range = ±1.25 × V <sub>REF</sub>                                |       | 89   |                  | dB   |

|                         |                                        | Input range = ±0.75 × V <sub>REF</sub>                                |       | 88   |                  |      |

|                         |                                        | Input range = $\pm 0.625 \times V_{REF}$                              |       | 88   |                  |      |

|                         |                                        | Input range = 3 × V <sub>REF</sub>                                    |       | 89   |                  |      |

|                         |                                        | Input range = 2.5 × V <sub>REF</sub>                                  |       | 89   |                  |      |

|                         |                                        | Input range = 1.5 × V <sub>REF</sub>                                  |       | 87   |                  |      |

|                         |                                        | Input range = 1.25 × V <sub>REF</sub>                                 |       | 86   |                  |      |

| Crosstalk Isol          | ation                                  | Interfere channel input<br>overdriven to 2 x maximum<br>input voltage |       | 120  |                  | dB   |

| Crosstalk Mei           | mory                                   | Interfere channel input<br>overdriven to 2 x maximum<br>input voltage |       | 90   |                  | dB   |

| Auxiliary Cha           | annel                                  |                                                                       |       | 1    | 1                |      |

| Resolution              |                                        |                                                                       | 16    |      |                  | Bits |

| V <sub>AUX_IN</sub>     | AUX_IN Voltage<br>Range <sup>(1)</sup> | (AUX_IN – AUX_GND)                                                    | 0     |      | V <sub>REF</sub> | V    |

|                         | Operating Input                        | AUX_IN                                                                | 0     |      | V <sub>REF</sub> | V    |

|                         | Range <sup>(1)</sup>                   | AUX_GND                                                               |       | 0    |                  | V    |

| 0                       | In mut Com - sites                     | During sampling                                                       |       | 35   |                  | pF   |

| Cin                     | Input Capacitance                      | During conversion                                                     |       | 5    |                  | pF   |

| Analog input<br>current | Input Leakage<br>Current               |                                                                       |       | 100  |                  | nA   |

| Differential            |                                        | All input ranges                                                      | -0.99 | ±0.5 | 1                | LSB  |

| INL                     | Integral Nonlinearity                  | All input ranges                                                      | -2.2  | ±1   | 2.2              | LSB  |

| Parameter             |                                               | Test Conditions                                                         | Min   | Тур   | Max    | Unit   |

|-----------------------|-----------------------------------------------|-------------------------------------------------------------------------|-------|-------|--------|--------|

| E <sub>G(AUX)</sub>   | Gain Error                                    | At T <sub>A</sub> = 25°C                                                |       | ±0.01 | ±0.018 | %FSR   |

| E <sub>O(AUX)</sub>   | Offset Error                                  | At T <sub>A</sub> = 25°C                                                |       | ±0.5  | ±1.05  | mV     |

| SNR                   | Signal-to-noise Ratio                         | V <sub>AUX_IN</sub> = –0.5 dBFS at 1 kHz                                | 85.4  | 89    |        | dB     |

| THD                   | Total Harmonic<br>Distortion                  | V <sub>AUX_IN</sub> = -0.5 dBFS at 1 kHz                                |       | -104  |        | dB     |

| SINAD                 | Signal-to-noise<br>Distortion Ratio           | V <sub>AUX_IN</sub> = -0.5 dBFS at 1 kHz 85 88.8                        |       |       | dB     |        |

| SFDR                  | Spurious-free<br>Dynamic Range                | V <sub>AUX_IN</sub> = –0.5 dBFS at 1 kHz                                |       | 104   |        | dB     |

| Internal Refe         | rence Output                                  |                                                                         |       |       |        |        |

| Vrefio_int            | REFIO Voltage                                 | Voltage on REFIO pin<br>(configured as output)<br>T <sub>A</sub> = 25°C | 4.086 | 4.096 | 4.106  | v      |

|                       | Reference<br>Temperature Drift <sup>(1)</sup> |                                                                         |       | 5     | 10     | ppm/°C |

| Cout_refio            | Decoupling<br>Capacitor on REFIO              |                                                                         |       | 0.1   |        | μF     |

| VREFCAP               | Reference Voltage                             | Reference voltage to ADC<br>(on REFCAP pin)<br>T <sub>A</sub> = 25°C    | 4.086 | 4.096 | 4.106  | v      |

|                       | Reference Buffer<br>Output Impedance          |                                                                         |       | 0.5   |        | Ω      |

|                       | Reference Buffer<br>Temperature Drift         |                                                                         |       | 1     |        | ppm/°C |

| Cout_refcap           | Decoupling<br>Capacitor on REFIO              |                                                                         |       | 10    |        | μF     |

| t <sub>on</sub>       | Reference Turn-on<br>Time                     | $C_{OUT\_REFIO} = 0.1 \ \mu F$<br>$C_{OUT\_REFCAP} = 10 \ \mu F$        |       | 10    |        | ms     |

| External Ref          | erence Input                                  |                                                                         |       | T     | 1      |        |

| VREFIO_EXT            | External Reference                            | External reference voltage<br>on REFIO<br>(configured as input)         | 4.046 | 4.096 | 4.146  | v      |

| Power-Supp            | ly Requirements                               |                                                                         |       |       |        |        |

| AVDD <sup>(1)</sup>   | Analog Power-supply<br>Voltage                | Analog supply                                                           | 4.75  | 5     | 5.25   | V      |

|                       | Digital Power supply                          | Digital supply range                                                    | 1.65  | 3.3   | AVDD   | V      |

| DVDD <sup>(1)</sup>   | Digital Power-supply<br>Voltage               | Digital supply range for specified performance                          | 2.7   | 3.3   | 5.25   | V      |

| I <sub>AVDD_DYN</sub> | AVDD Dynamic                                  | AVDD = 5 V, f <sub>S</sub> = maximum<br>and internal reference          |       | 18    | 22     | mA     |

| Parameter                      |                                   | Test Conditions                                                  | Min        | Тур | Мах        | Unit |

|--------------------------------|-----------------------------------|------------------------------------------------------------------|------------|-----|------------|------|

| I <sub>AVDD_STC</sub>          | AVDD Static                       | Device not converting and internal reference                     |            | 15  | 20         | mA   |

| ISTDBY                         | Standby                           | At AVDD = 5 V, device in<br>STDBY mode and internal<br>reference |            | 6   | 8          | mA   |

| IPWR_DN                        | Power-down                        | At AVDD = 5 V, device in<br>PWR_DN                               |            | 12  |            | μA   |

| I <sub>DVDD_DYN</sub>          | Digital Supply<br>Current         | At DVDD = 3.3 V, output = 0000                                   |            | 0.5 |            | mA   |

| Digital Input                  | s (CMOS)                          |                                                                  |            |     |            |      |

| VIH                            | Digital Input Logic               | DVDD > 2.1 V                                                     | 0.7 x DVDD |     | DVDD + 0.3 | V    |

| VIL                            | Levels                            |                                                                  | -0.3       |     | 0.3 x DVDD | V    |

| VIH                            | Digital Input Logic               |                                                                  | 0.8 x DVDD |     | DVDD + 0.3 | V    |

| VIL                            | Levels                            | DVDD ≤ 2.1 V                                                     | -0.3       |     | 0.2 x DVDD | V    |

| Input Leakage                  | e Current                         |                                                                  |            | 100 |            | nA   |

| Input Capacit                  | ance                              |                                                                  |            | 5   |            | pF   |

| Digital Outpu                  | uts (CMOS)                        |                                                                  |            |     |            |      |

| V <sub>OH</sub>                | Digital Output Logic              | I <sub>0</sub> = 500-μA source                                   | 0.8 x DVDD |     | DVDD       | V    |

| V <sub>OL</sub>                | Levels                            | I <sub>0</sub> = 500-μA sink                                     | 0          |     | 0.2 x DVDD | V    |

| Floating State Leakage Current |                                   | Only for SDO                                                     |            | 1   |            | μA   |

| Internal Pin Capacitance       |                                   |                                                                  |            | 5   |            | pF   |

| Temperature                    | Range <sup>(1)</sup>              |                                                                  |            |     | ·          |      |

| T <sub>A</sub>                 | Operating Free-air<br>Temperature |                                                                  | -40        |     | 125        | °C   |

(1) These specifications are not production tested but are supported by characterization data at the initial product release.

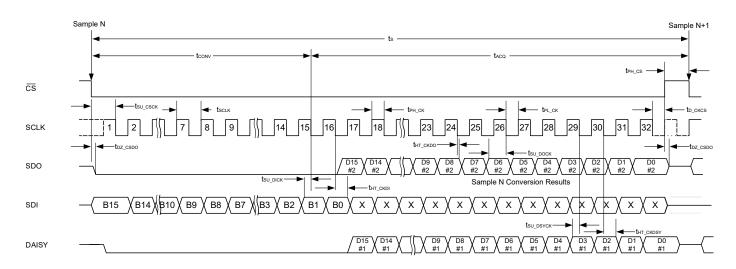

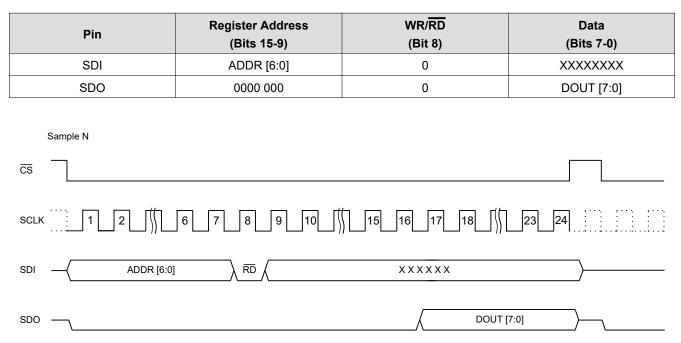

### Timing Requirements <sup>(1)</sup>

#### **Universal Serial Timing Specifications**

AVDD = 5 V, DVDD = 5 V,  $V_{REF}$  = 4.096 V internal reference,  $f_{SAMPLE}$  = 500 kSPS,  $T_A$  = -40°C to +125°C, interface timing tested using a load capacitance of 20 pF, unless otherwise noted.

|                       | Parameter                                                  | Min  | Тур | Max | Unit              |

|-----------------------|------------------------------------------------------------|------|-----|-----|-------------------|

| Timing Spe            | cifications                                                |      |     |     |                   |

| fs                    | Sampling frequency (f <sub>CLK</sub> = max)                |      |     | 500 | kSPS              |

| ts                    | ADC cycle time period (f <sub>CLK</sub> = max)             | 2    |     |     | μs                |

| f <sub>SCLK</sub>     | Serial clock frequency ( $f_s$ = max) DVDD ≥ 3V            |      |     | 17  | MHz               |

| t <sub>SCLK</sub>     | Serial clock time period ( $f_s$ = max) DVDD ≥ 3V          | 59   |     |     | ns                |

| t <sub>CONV</sub>     | Conversion time                                            |      |     | 880 | ns                |

| t <sub>DZ_CSDO</sub>  | Delay time: $\overline{CS}$ falling to data enable         |      |     | 10  | ns                |

| t <sub>D_CKCS</sub>   | Delay time: last SCLK falling to CS rising                 | 10   |     |     | ns                |

| t <sub>DZ_CSDO</sub>  | Delay time: $\overline{CS}$ rising to SDO going to 3-state | 10   |     |     | ns                |

| Timing Rec            | uirements                                                  |      |     | 1   | 1                 |

| t <sub>ACQ</sub>      | Acquisition time                                           | 1120 |     |     | ns                |

| t <sub>PH_CK</sub>    | Clock high time                                            | 0.4  |     | 0.6 | tsclk             |

| t <sub>PL_CK</sub>    | Clock low time                                             | 0.4  |     | 0.6 | t <sub>SCLK</sub> |

| t <sub>PH_CS</sub>    | CS high time                                               | 30   |     |     | ns                |

| tsu_cscк              | Setup time: CS falling to SCLK falling                     | 15   |     |     | ns                |

| t <sub>нт_скро</sub>  | Hold time: SCLK falling to (previous) data valid on SDO    | 5    |     |     | ns                |

| tsu_docк              | Setup time: SDO data valid to SCLK falling                 | 25   |     |     | ns                |

| tsu_DICK              | Setup time: SDI data valid to SCLK falling                 | 5    |     |     | ns                |

| t <sub>HT_CKDI</sub>  | Hold time: SCLK falling to (previous) data valid on SDI    | 5    |     |     | ns                |

| t <sub>SU_DSYCK</sub> | Setup time: DAISY data valid to SCLK falling               | 5    |     |     | ns                |

| tht_ckdsy             | Hold time: SCLK falling to (previous) data valid on DAISY  | 5    |     |     | ns                |

#### **Table 2. Serial Interface Timing Specifications**

(1) Parameters are provided by the design simulation.

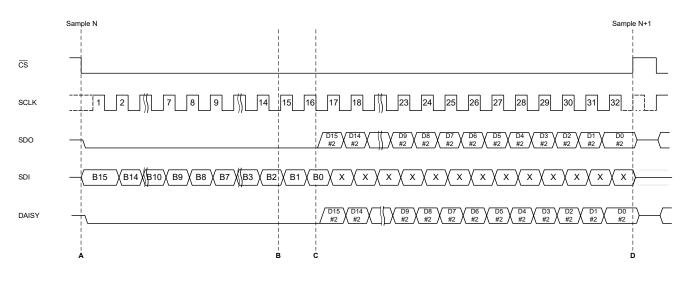

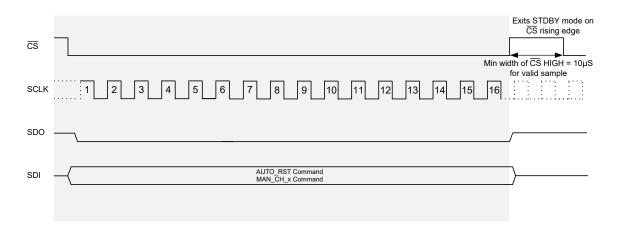

Figure 1. Universal Timing Diagram Across All Interfaces

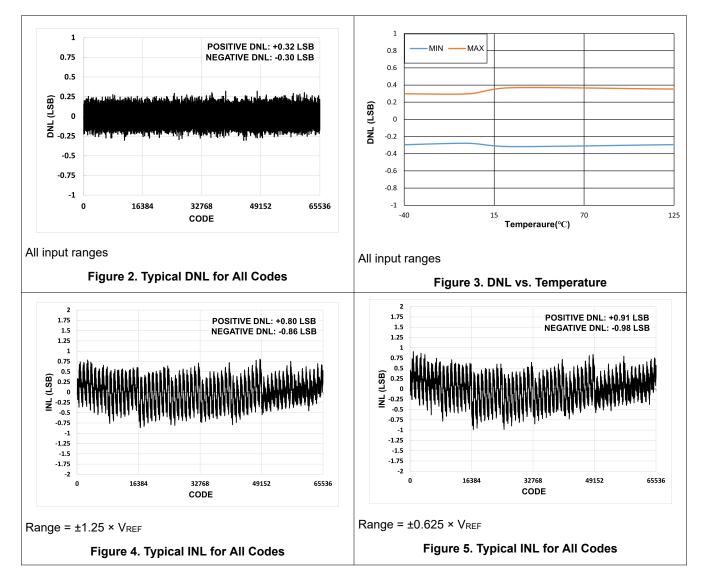

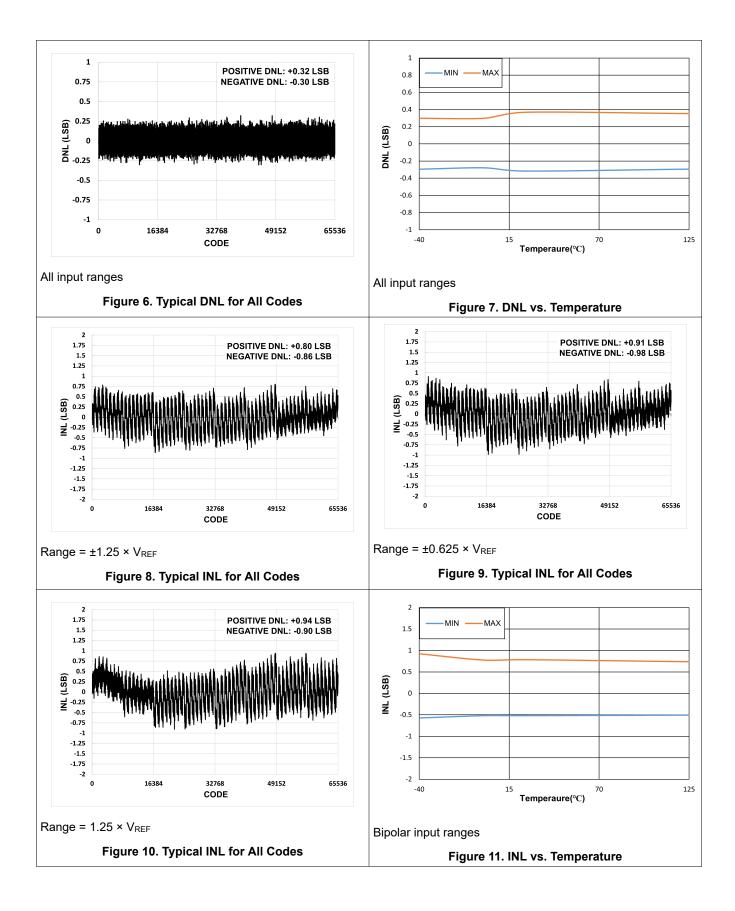

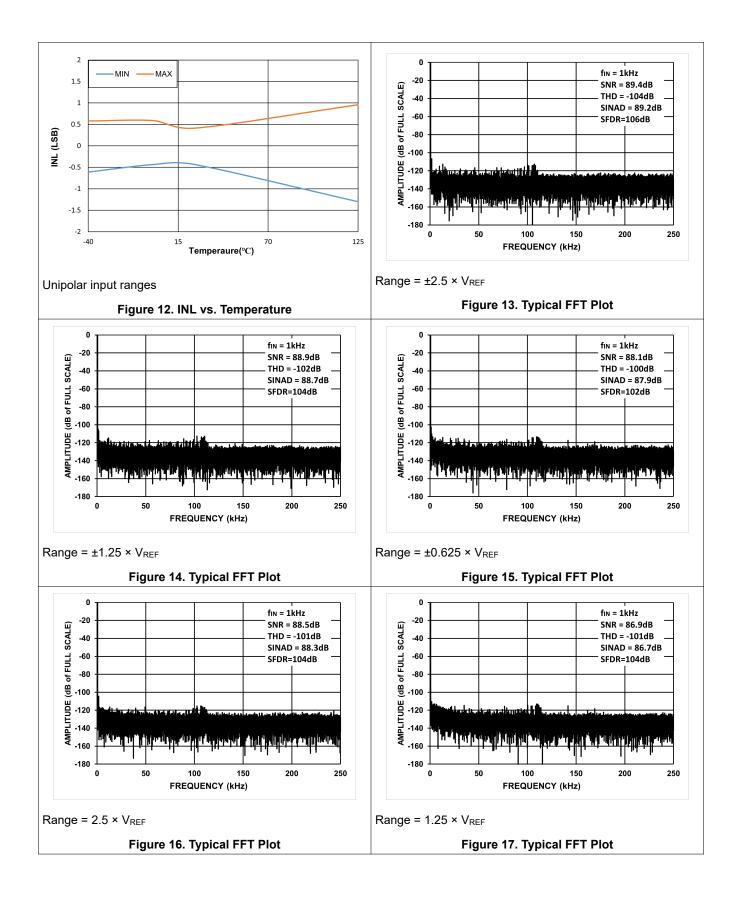

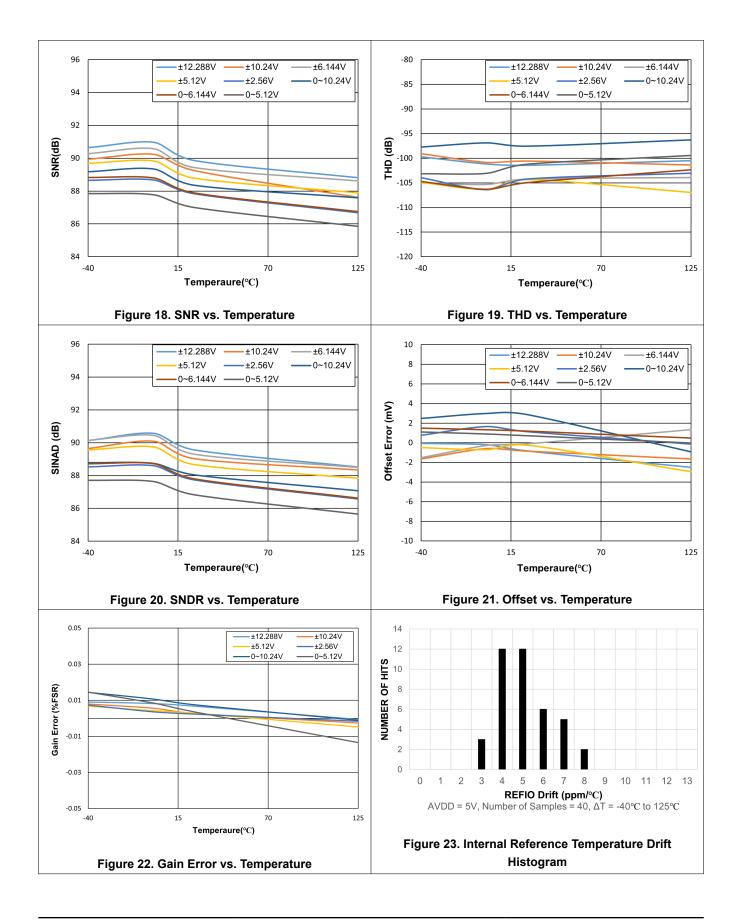

### **Typical Performance Characteristics**

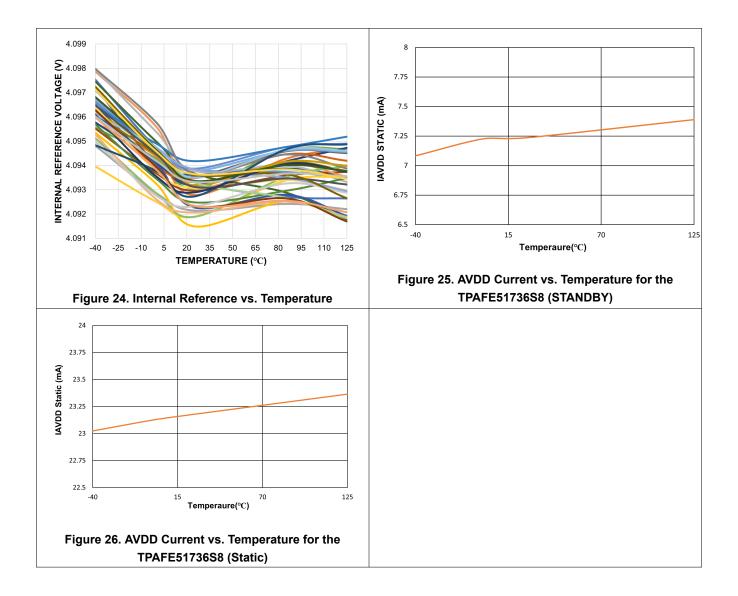

All test conditions:  $T_A = 25^{\circ}C$ , AVDD = 5 V, DVDD = 5 V, internal reference  $V_{REF} = 4.096$  V, and  $f_{SAMPLE} = 500$  kSPS, unless otherwise noted.

### **TPAFE51736S4**

## **Detailed Description**

### Overview

The TPAFE51736S4 is a 16-bit data acquisition system with 4 analog input channels. Each input channel includes input protection circuitry, a programmable gain amplifier (PGA), an analog low-pass filter, and an analog-to-digital converter (ADC) driver. These channels feed into a 4-channel analog multiplexer (MUX) with an ADC operating at a 500 KSPS throughput rate. The device incorporates a 4.096-V internal reference with a fast-settling buffer and a flexible channel sequencer. It also provides high-speed serial interfaces for communication with the daisy-chain function, making it suitable for a wide range of data acquisition applications.

The device operates with a single 5-V analog supply and can process true bipolar input signals. It provides a programmable analog signal range, including options for true bipolar single-ended  $\pm 12.288$  V,  $\pm 10.24$  V,  $\pm 6.144$  V,  $\pm 5.12$  V,  $\pm 3.072$  V,  $\pm 2.56$  V, unipolar single-ended 0 V - 12.288 V, 0 V - 10.24 V, 0 V - 6.144 V, 0 V - 5.12 V, and true bipolar fully-differential  $\pm 12.288$  V,  $\pm 10.24$  V,  $\pm 6.144$  V,  $\pm 5.12$  V input signals. The input clamp protection circuitry can protect the device from being damaged by voltages as high as  $\pm 30$  V. The device features a constant 1M $\Omega$  resistive input impedance.

### **Functional Block Diagram**

### **Feature Description**

#### Analog Inputs

The TPAFE51736 incorporates a 16-bit successive approximation register (SAR) analog-to-digital converter (ADC). The ADC is linked up to 8 analog input channels through a multiplexer. The device comprises a total of eight analog input pairs. The ADC is responsible for converting the voltage difference between the analog input pairs AINxP – AINxN. The simplified circuit schematic for each analog input channel is shown in the function block diagram, encompassing the input clamp protection circuit, PGA, low-pass filter, multiplexer, high-speed ADC driver, and a precision 16-bit SAR ADC.

#### Analog Input Ranges

The TPAFE51736 can handle true bipolar differential, bipolar single-ended, and unipolar single-ended input voltages. It is possible to configure an individual analog input range per channel from the range select registers.

The devices sample the voltage difference (AIN\_xP – AIN\_xN) between the selected analog input pairs. They allow a  $\pm 0.1$  V range on the AIN\_nGND pin for all analog input channels. This feature is beneficial in modular systems where the sensor or signal-conditioning block is located at a distance from the ADC on the board. It proves particularly useful when there might be a difference in the ground potential between the sensor or signal conditioner and the ADC ground. In such cases, it is recommended to run separate wires from the AIN\_xN pin of the device to the sensor or signal-conditioning ground.

In single-ended mode, the AINxN pins are typically connected to analog ground and allow a ±0.1 V range referred to ground.

In differential mode, the AINxP and AINxN typically sense the fully differential input signals within a certain input common mode range. Also, this feature is beneficial in modular systems where the sensor or signal-conditioning block is located at a distance from the ADC on the board. It proves particularly useful when there might be a difference in the ground potential between the sensor or signal conditioner and the ADC ground. In such cases, it is recommended to run separate wires from the AIN\_xN pin of the device to the sensor or signal-conditioning ground.

#### Analog Input Impedance

The TPAFE51736 features a fixed high analog input impedance of 1 M $\Omega$ , which is nearly constant at different sampling frequencies. It eliminates the need for an external driver amplifier, allowing direct connection to the source or sensor.

#### Analog Input Clamp Protection

The TPAFE51736 incorporates an internal clamp protection circuit on each of the analog input channels. This protection circuit allows each analog input voltage to swing up to  $\pm 30$  V. Beyond this threshold, the input clamp circuit activates while still operating from a single 5 V supply.

To ensure that the input current stays within safe limits ( $\pm$ 10 mA) for input voltages above the clamp threshold, it is advisable to use a series resistor with the analog inputs. This resistor can serve the dual purpose of limiting input current and providing an antialiasing low-pass filter (LPF) when combined with a capacitor. Matching the external source impedance on the AINxP and AINxN pins helps cancel any additional offset error. However, it's advisable to avoid prolonged activation of the clamp protection circuitry during normal or power-down conditions for optimal device performance.

#### Programmable Gain Amplifier (PGA)

The TPAFE51736 includes a PGA at each analog input channel, providing support for both unipolar/bipolar single-ended and bipolar differential inputs. The supported analog input ranges are listed below. Each channel's analog input range can be configured independently using the range select register fields located at addresses 0x5 to 0xC and 0xD for range expanding.

|                   | Amelan kanat Damas           |                | RANGE_CHn[3:0] |       |       |

|-------------------|------------------------------|----------------|----------------|-------|-------|

| Analog Input Mode | Analog Input Range           | CHn_OVER_RANGE | BIT 2          | BIT 1 | BIT 0 |

| Single-ended      | ±3 x V <sub>REF</sub>        | 1              | 0              | 0     | 0     |

| Single-ended      | ±2.5 x V <sub>REF</sub>      | 0              | 0              | 0     | 0     |

| Single-ended      | ±1.5 x V <sub>REF</sub>      | 1              | 0              | 0     | 1     |

| Single-ended      | ±1.25 x V <sub>REF</sub>     | 0              | 0              | 0     | 1     |

| Single-ended      | ±0.75 x V <sub>REF</sub>     | 1              | 0              | 1     | 0     |

| Single-ended      | ±0.625 x V <sub>REF</sub>    | 0              | 0              | 1     | 0     |

| Differential      | ±3 x V <sub>REF</sub>        | 1              | 0              | 1     | 1     |

| Differential      | ±2.5 x V <sub>REF</sub>      | 0              | 0              | 1     | 1     |

| Differential      | ±1.5 x V <sub>REF</sub>      | 1              | 1              | 0     | 0     |

| Differential      | ±1.25 x V <sub>REF</sub>     | 0              | 1              | 0     | 0     |

| Differential      | ±0.75 x V <sub>REF</sub>     | 1              | 1              | 1     | 1     |

| Differential      | ±0.625 x V <sub>REF</sub>    | 0              | 1              | 1     | 1     |

| Single-ended      | 0 to 3 x V <sub>REF</sub>    | 1              | 1              | 0     | 1     |

| Single-ended      | 0 to 2.5 x V <sub>REF</sub>  | 0              | 1              | 0     | 1     |

| Single-ended      | 0 to 1.5 x V <sub>REF</sub>  | 1              | 1              | 1     | 0     |

| Single-ended      | 0 to 1.25 x V <sub>REF</sub> | 0              | 1              | 1     | 0     |

#### Table 3. Analog Input Ranges

#### Low-Pass Filter (LPF)

Every analog input channel on the TPAFE51736 is equipped with an antialiasing low-pass filter (LPF) situated at the PGA output. The following table outlines the programmable LPF options associated with the analog input range in the device. The analog input bandwidth for all eight channels can be chosen using the LPF\_CONFIG[1:0] bits found in address 0xE.

#### Table 4. Low-Pass Filter Corner Frequency

| LPF            | Analog Input Range | Typical –3 dB Bandwidth |

|----------------|--------------------|-------------------------|

| Low-bandwidth  | All input ranges   | 15 kHz                  |

| High-bandwidth | All input ranges   | 35 kHz                  |

#### Multiplexer (MUX)

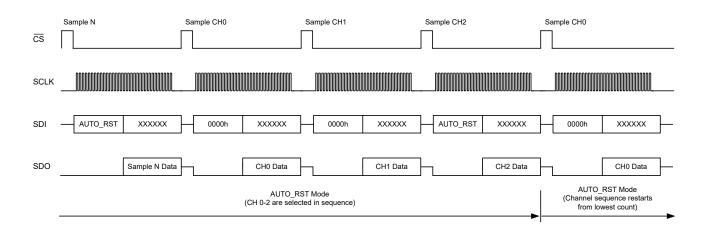

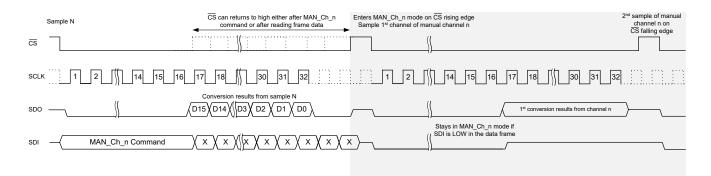

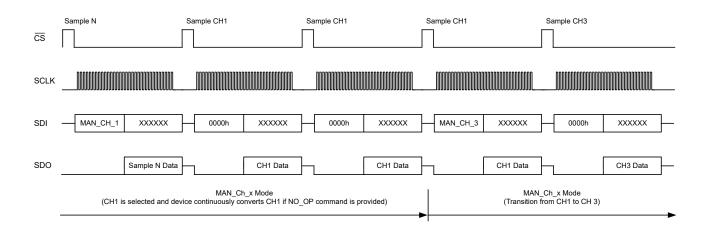

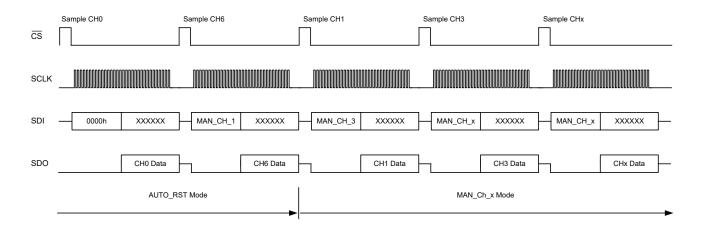

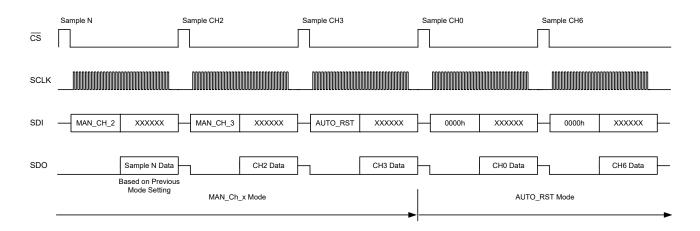

The TPAFE51736 includes an integrated multi-channel analog multiplexer. Each analog input channel is processed of the voltage difference between the positive analog input AIN\_xP and the negative ground input AIN\_xN through the analog front-end circuitry before entering the multiplexer. The ADC directly samples the output of the multiplexer. The multiplexer can scan these analog inputs in either manual or auto-scan mode, as detailed in the Channel Sequencing Modes section.In manual mode (MAN\_Ch\_n), the channel is selected for every sample through a register write. In auto-scan mode (AUTO\_RST), the channel number increments automatically on every  $\overline{CS}$  falling edge after the current channel is sampled. The analog inputs can be chosen for an auto-scan with register settings (refer to the Auto-Scan Sequencing Control Registers section). The devices automatically scan only the selected analog inputs in ascending order.

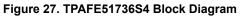

#### Reference

The TPAFE51736 can operate with either an internal voltage reference or an external voltage reference, utilizing the internal buffer. The configuration between internal and external reference is controlled by an external REFSEL pin. The devices incorporate a built-in buffer amplifier designed to drive the reference input of the internal ADC core, optimizing overall performance.

#### **Internal Reference**

The TPAFE51736 includes an on-chip 4.096 V reference which can be accessed through the REFIO pin. The SAR ADC utilizes this internally generated and buffered 4.096 V reference for its conversions. To select the internal reference, connect the REFSEL pin to AGND or tie it low. In this configuration, the REFIO pin serves as an output pin, providing the internal reference value. It is recommended to place a 0.1  $\mu$ F decoupling capacitor between the REFIO pin and REFGND, and a larger capacitor requires longer settling time. Place the capacitor as close to the REFIO pin as possible. The capacitors act as decoupling components and form a low-pass filter with the output impedance of the internal band-gap circuit, limiting the noise of the reference. Avoid using the REFIO pin to drive external loads, as REFIO has limited current output capability. If needed as a source, it can be followed by an operational amplifier buffer.

Figure 28. Device Connections for Using an Internal 4.096-V Reference

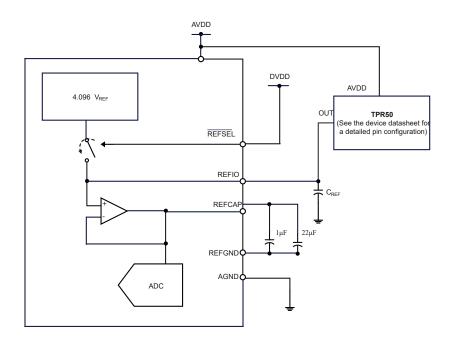

#### **External Reference**

Alternatively, the TPAFE51736 can accept an external reference voltage applied to the REFIO pin. When an external 4.096 V reference is provided, the device internally amplifies it to create the 4.096 V buffered reference used by the SAR ADC. To select external reference mode, either tie the REFSEL pin high or connect it to the DVDD supply. In this mode, an external 4.096-V reference should be applied at REFIO, which becomes an input pin. Users can use any external reference in this mode. The internal buffer is designed to handle dynamic loading on the REFCAP pin, which is internally connected to the ADC reference input. When using an external reference, it's important to appropriately filter the reference output to minimize its impact on system performance.

The output of the internal reference buffer is present at the REFCAP pin. To ensure proper operation, decoupling capacitors of 22  $\mu$ F and 1  $\mu$ F must be connected between REFCAP and REFGND. It's important not to use the internal buffer to drive any external loads due to the limited current output capability of this buffer.

#### Auxiliary Channel

The TPAFE51736 incorporates a single-ended auxiliary input channel (AUX\_IN and AUX\_GND). The AUX channel facilitates a direct interface with an internal, high-precision, 16-bit ADC through the multiplexer, excluding the front-end analog signal conditioning found in other analog input channels. The AUX channel supports a unipolar input range of 0 V to  $V_{REF}$ , as no front-end PGA on the auxiliary channel. The AUX\_IN pin can accept input signals ranging from 0 V to  $V_{REF}$ , while the AUX GND pin should be connected to GND.

During a conversion, the voltage between these pins is directly sampled on an internal sampling capacitor. The input current required to charge the sampling capacitor depends on factors such as the sampling rate, input frequency, and source impedance. For slow applications with a low-impedance source, the inputs of the AUX channel can be directly driven. However, as the throughput, input frequency, or source impedance increases, a driving amplifier is recommended at the input to achieve optimal AC performance from the AUX channel.

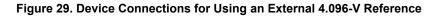

#### ADC Transfer Function

The TPAFE51736 outputs 16 bits of conversion data in straight binary format for all ranges and all modes (unipolar/bipolar). The full-scale range (FSR) for each input signal is determined by the difference between the positive full-scale (PFS) input voltage and the negative full-scale (NFS) input voltage. The size of the least significant bit (LSB) is calculated as FSR /  $2^{16}$  = FSR / 65536 for the 16-bit resolution of the ADC. In the case of a reference voltage (V<sub>REF</sub>) set to 4.096 V, the LSB values for various input ranges are as follows:

Figure 30. 16-Bit ADC Transfer Function (Straight-Binary Format)

| Input Range                         | NFS (V) | PFS (V) | FSR (V) | LSB (µV) |

|-------------------------------------|---------|---------|---------|----------|

| ±3 x V <sub>REF</sub>               | -12.288 | 12.288  | 24.576  | 375      |

| ±2.5 x V <sub>REF</sub>             | -10.24  | 10.24   | 20.48   | 312.5    |

| ±1.5 x V <sub>REF</sub>             | -6.144  | 6.144   | 12.288  | 187.5    |

| ±1.25 x V <sub>REF</sub>            | -5.12   | 5.12    | 10.24   | 156.25   |

| $\pm 0.75 \text{ x V}_{\text{REF}}$ | -3.072  | 3.072   | 6.144   | 93.75    |

| ±0.625 x V <sub>REF</sub>           | -2.56   | 2.56    | 5.12    | 78.125   |

| 0 to 3 x V <sub>REF</sub>           | 0       | 12.288  | 12.288  | 187.5    |

| 0 to 2.5 x $V_{\text{REF}}$         | 0       | 10.24   | 10.24   | 156.25   |

| 0 to 1.5 x V <sub>REF</sub>         | 0       | 6.144   | 6.144   | 93.75    |

| 0 to 1.25 x $V_{\text{REF}}$        | 0       | 5.12    | 5.12    | 78.125   |

Table 5. Transfer Characteristics

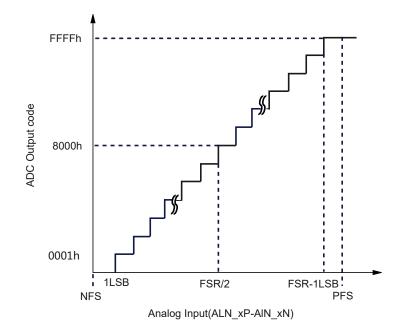

#### Alarm Feature

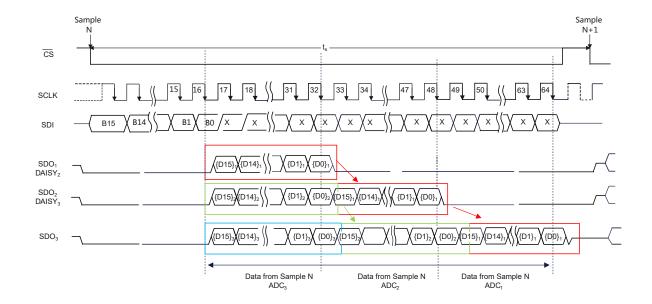

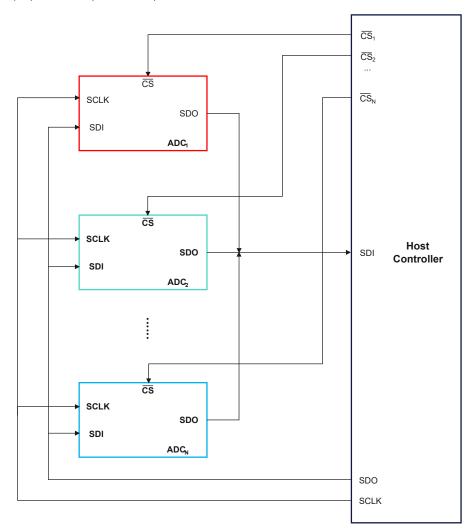

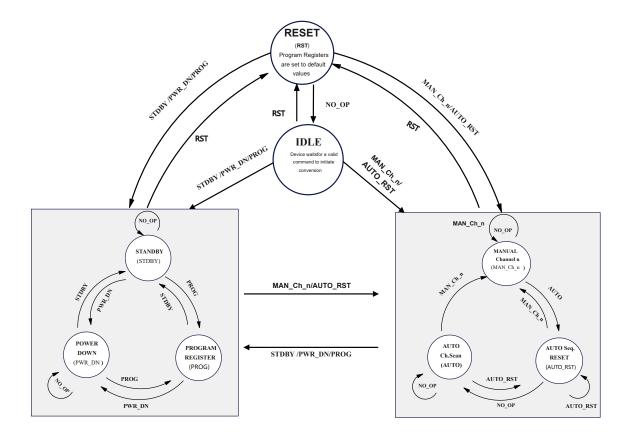

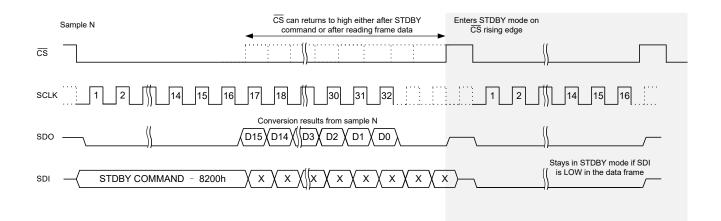

The TPAFE51736 features an active-high ALARM output. The ALARM signal is synchronous with a state change on the 16th falling edge of the SCLK signal. A high level on ALARM indicates that the alarm flag has been triggered on one or more channels of the device. This pin can be connected to interrupt the host input. Upon receiving an ALARM interrupt, the alarm flag registers are examined to identify which channels have an alarm condition. Each channel on the devices supports two independently programmable alarms – a low alarm and a high alarm – with separate hysteresis settings for each alarm threshold. If the alarm feature is disabled, the ALARM pin can be left floating.