#### **Features**

- 16-Bit, Single-Channel ADC with Integrated Analog Front-End

- · Sampling with 100 kSPS throughput Rate

- · Independently Programmable Channel Inputs

- True Bipolar Single-ended:  $\pm 12.288$  V,  $\pm 10.24$  V,  $\pm 6.144$  V,  $\pm 5.12$  V,  $\pm 3.072$  V,  $\pm 2.56$  V

- Unipolar Single-ended: 0 V 12.288 V, 0 V 10.24

V, 0 V 6.144 V, 0 V 5.12 V

- True Bipolar Fully-differential: ±12.288 V, ±10.24 V, ±6.144 V, ±5.12 V

- Configurable Analog Bandwidth: 15 kHz or 35 kHz

- Power Supply

- Single Analog Supply: 5 V

- Digital Supply: 1.71 V to 5 V

- · Highly Integrated Analog Front-End

- 1-MΩ Analog Input Impedance

- Programmable Gain Amplifier

- Analog Low-Pass Filter

- Internal Accurate Reference and Reference Buffer

- ±30 V Analog Input Overvoltage Clamp Protection with ±7-kV ESD

- · Flexible Digital and Interface

- Serial Interface Compatible with SPI

- Daisy-Chain Function

- Integrated Diagnostic Function

- Analog Input Open Detect with Manual or Auto Mode

- Optional Cyclic Redundancy Check (CRC) Error Checking

- ALARM

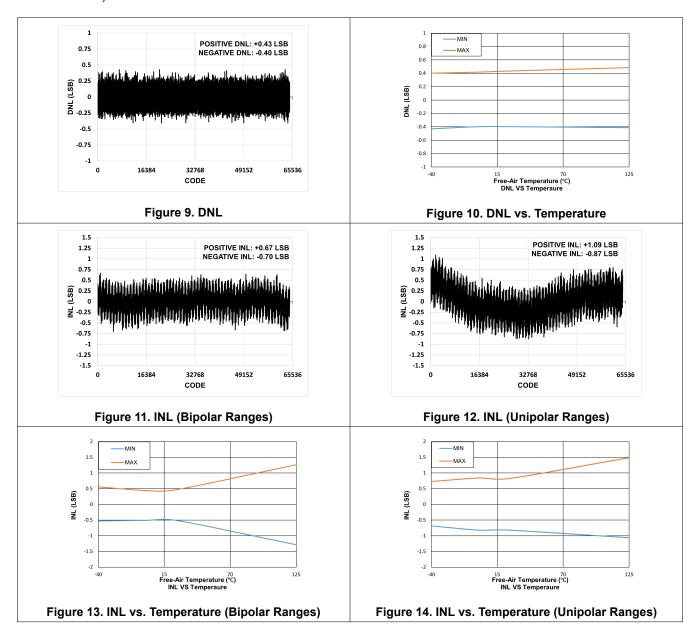

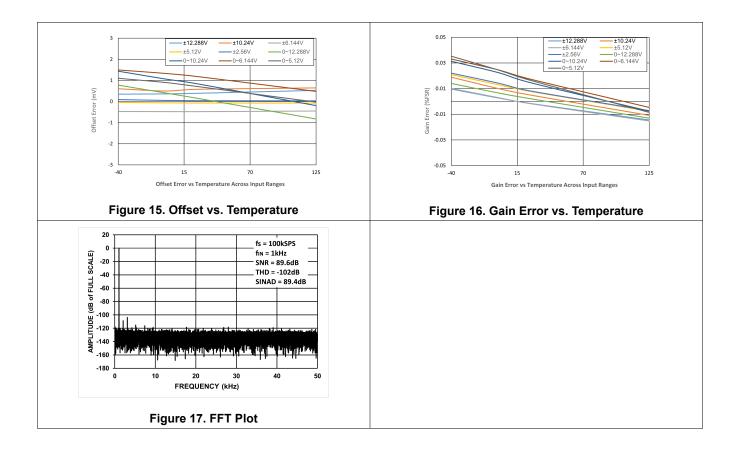

- Typical Performance

- DNL: ±0.5 LSB

- INL: ±1 LSB

- SNR: 90 dB

- SINAD: 90 dB

- THD: −103 dB

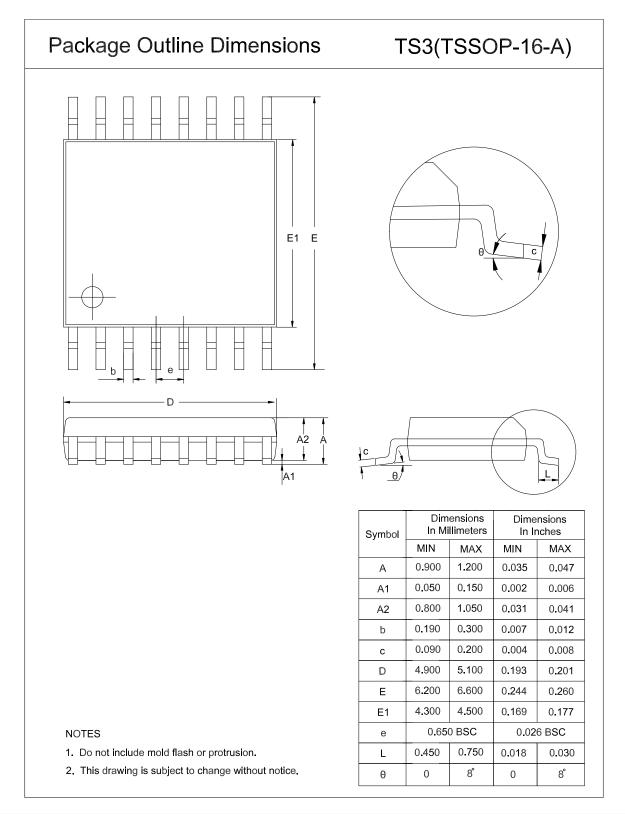

- Package: TSSOP16 Package

- Wide Operating Temperature Range: −40°C to +125°C

### **Applications**

- · Analog Input Modules

- Servo

- · Channel-to-Channel Isolated Data Acquisition

### **Description**

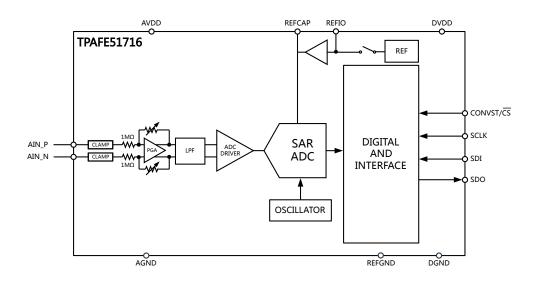

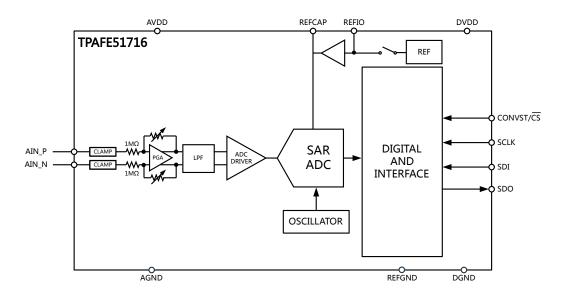

The TPAFE51716S is a single-channel, 16-bit, 100 kSPS sampling system based on a successive approximation register (SAR) analog-to-digital converter (ADC). The TPAFE51716S is highly integrated with analog front-end for each channel, including input overvoltage clamp, 1  $M\Omega$  input impedance, programmable gain amplifier (PGA), active low-pass filter, and ADC driver. Internal precision and low-drift reference with buffer makes the device feasible for a compact data acquisition solution. The digital interface supports communication with various host controllers with SPI-compatible serial and daisy-chaining of multiple devices.

The TPAFE51716S can process true bipolar single-ended  $\pm 12.288$  V,  $\pm 10.24$  V,  $\pm 6.144$  V,  $\pm 5.12$  V,  $\pm 3.072$  V,  $\pm 2.56$  V, unipolar single-ended 0 V - 12.288 V, 0 V - 10.24 V, 0 V - 6.144 V, 0 V - 5.12 V, and true bipolar fully-differential  $\pm 12.288$  V,  $\pm 10.24$  V,  $\pm 6.144$  V,  $\pm 5.12$  Vinput signals, with a single 5 V analog power supply. The 1 M $\Omega$  high input impedance simplified analog input design, and the device can be connected directly to sensors. The analog input overvoltage could protect the device up to  $\pm 30$  V. The device offers a simple SPI-compatible serial interface and also supports daisy-chaining of multiple devices.

The device integrates various diagnostic functions to improve system robustness, like analog input open detection, alarm, and CRC error checking on read and write data and registers.

The TPAFE51716S is available in the TSSOP 5x4.4-16 package and operates from  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ .

## **Functional Block Diagram**

www.3peak.com 2 / 58 BA20240404A0

## **Table of Contents**

| Features                                | 1  |

|-----------------------------------------|----|

| Applications                            | 1  |

| Description                             | 1  |

| Functional Block Diagram                | 2  |

| Product Family Table                    | 5  |

| Revision History                        | 5  |

| Pin Configuration and Functions         | 6  |

| Specifications                          |    |

| Absolute Maximum Ratings <sup>(1)</sup> | 8  |

| ESD, Electrostatic Discharge Protection | 8  |

| Recommended Operating Conditions        | 8  |

| Thermal Information                     | 8  |

| Electrical Characteristics              | 9  |

| Timing Requirements <sup>(1)</sup>      | 15 |

| Typical Performance Characteristics     | 21 |

| Detailed Description                    | 23 |

| Overview                                | 23 |

| Functional Block Diagram                | 23 |

| Feature Description                     | 24 |

| Device Functional Modes                 | 28 |

| Register Maps                           | 40 |

| Device Configuration and Register Maps  | 40 |

| DEVICE_ID_REG Register                  |    |

| RST_PWRCTL_REG Register                 | 42 |

| SDI_CTL_REG Register                    | 43 |

| SDO_CTL_REG Register                    | 44 |

| DATAOUT_CTL_REG Register                | 45 |

| RANGE_SEL_REG Register                  | 47 |

| ALARM_REG Register                      | 49 |

| ALARM_H_TH_REG Register                 | 51 |

| ALARM_L_TH_REG Register                 | 51 |

| OPEN_DETECT Register                    | 52 |

| OPEN_DETECT_ADC_CODE Register           | 53 |

| BW_CTRL Register                        | 53 |

| CRC_CFG Register                        | 54 |

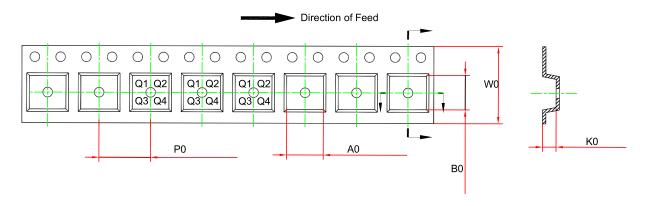

| Tape and Reel Information               | 55 |

| Package Outline Dimensions      | 56 |

|---------------------------------|----|

| TSSOP16                         | 56 |

| Order Information               | 57 |

| IMPORTANT NOTICE AND DISCLAIMER | 58 |

# **Product Family Table**

| Order Number     | Channels | Resolution | Resolution Throughput |         |

|------------------|----------|------------|-----------------------|---------|

| TPAFE51716S-TS3R | 1        | 16 Bits    | 100 kSPS              | TSSOP16 |

## **Revision History**

| Date       | Revision | Notes            |

|------------|----------|------------------|

| 2025-01-17 | Rev.A.0  | Initial release. |

www.3peak.com 5 / 58 BA20240404A0

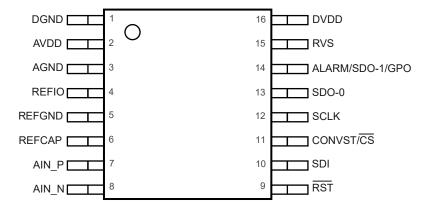

## **Pin Configuration and Functions**

TPAFE51716S TSSOP16 Package Top View

Table 1. Pin Functions: TPAFE51716S

| Pin Type (1) |                     | T (1)    | Donatis tion                                                                                                                                                                                                                                                                                                                                                  |

|--------------|---------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.          | Name                | Type ("/ | Description                                                                                                                                                                                                                                                                                                                                                   |

| 3            | AGND                | Р        | Analog ground pins.                                                                                                                                                                                                                                                                                                                                           |

| 8            | AIN_N               | Al       | Negative analog input.                                                                                                                                                                                                                                                                                                                                        |

| 7            | AIN_P               | Al       | Positive analog input                                                                                                                                                                                                                                                                                                                                         |

| 14           | ALARM/<br>SDO-1/GPO | DO       | Multifunction output pin. Active high alarm.  Data output 1 for serial communication. General-purpose output pin.                                                                                                                                                                                                                                             |

| 2            | AVDD                | Р        | Analog supply pins.                                                                                                                                                                                                                                                                                                                                           |

| 11           | CONVST/CS           | DI       | Dual-functionality pin.  Active high logic: conversion start input pin; a CONVST rising edge brings the device from the acquisition phase to the conversion phase.  Active low logic: chip-select input pin; the device takes control of the data bus when $\overline{\text{CS}}$ is low; the SDO-x pins go to tri-state when $\overline{\text{CS}}$ is high. |

| 1            | DGND                | Р        | Digital ground pins.                                                                                                                                                                                                                                                                                                                                          |

| 16           | DVDD                | Р        | Digital supply pins.                                                                                                                                                                                                                                                                                                                                          |

| 6            | REFCAP              | AO       | Reference buffer output pin. Decouple this pin to AGND using a capacitor. The voltage on this pin is typically 4.096 V.                                                                                                                                                                                                                                       |

| 5            | REFGND              | Р        | Reference ground pin. Connect this pin to AGND.                                                                                                                                                                                                                                                                                                               |

| 4            | REFIO               | AIO      | External reference input pin and internal reference output pin                                                                                                                                                                                                                                                                                                |

| 9            | RST                 | DI       | Hardware RST with low logic input active.                                                                                                                                                                                                                                                                                                                     |

| 15           | RVS                 | DO       | Multifunction output pin for serial interface. With $\overline{\text{CS}}$ held high, RVS reflects the status of the internal ADCST signal With $\overline{\text{CS}}$ low, the status of RVS depends on the output protocol selection.                                                                                                                       |

| 12           | SCLK                | DI       | This pin acts as the serial clock input for data transfers.                                                                                                                                                                                                                                                                                                   |

www.3peak.com 6 / 58 BA20240404A0

|     | Pin   | <b>T</b> (1) | Description                     |  |

|-----|-------|--------------|---------------------------------|--|

| No. | Name  | Type (1)     | Description                     |  |

| 10  | SDI   | DI           | Data input of the SPI interface |  |

| 13  | SDO-0 | DO           | This pin outputs serial data 0. |  |

<sup>(1)</sup> Al is analog input, GND is ground, P is power supply, REF is reference input/output, DI is digital input, DO is digital output, and CAP is decoupling capacitor pin.

www.3peak.com 7 / 58 BA20240404A0

### **Specifications**

### Absolute Maximum Ratings (1)

| Parameter        |                                              | Min  | Max          | Unit |

|------------------|----------------------------------------------|------|--------------|------|

|                  | Analog Input Voltage (AINxP or AINxN) to GND | -30  | +30          | V    |

| Analog Voltage   | AUX_IN to GND                                | -0.3 | AVDD + 0.3 V | V    |

|                  | REFCAP or REFIO to REFGND                    | -0.3 | AVDD + 0.3 V | V    |

| Digital Valtage  | Digital Input Voltage to GND                 | -0.3 | DVDD + 0.3 V | V    |

| Digital Voltage  | Digital Output Voltage to GND                | -0.3 | DVDD + 0.3 V | V    |

|                  | AVDD to GND                                  | -0.3 | 7            | V    |

| Supply Voltage   | DVDD to GND                                  | -0.3 | AVDD + 0.3 V | V    |

| TJ               | Maximum Junction Temperature                 |      | 150          | °C   |

| T <sub>A</sub>   | Operating Temperature Range                  | -40  | 125          | °C   |

| T <sub>STG</sub> | Storage Temperature Range                    | -65  | 150          | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

### **ESD, Electrostatic Discharge Protection**

| Symbol | Parameter Parameter      |                   | Condition                   | Minimum Level | Unit |

|--------|--------------------------|-------------------|-----------------------------|---------------|------|

| LIDM   | Lluman Dady Madal ECD    | Analog input pins | 41101/5054/15550 10 004 (1) | ±7            | kV   |

| HBM    | Human Body Model ESD     | All other pins    | ANSI/ESDA/JEDEC JS-001 (1)  | ±2            | kV   |

| CDM    | Charged Device Model ESD |                   | ANSI/ESDA/JEDEC JS-002 (2)  | ±1.5          | kV   |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### **Recommended Operating Conditions**

| Parameter |                        | Min  | Тур | Max  | Unit |

|-----------|------------------------|------|-----|------|------|

| AVDD      | Analog Supply Voltage  | 4.75 | 5   | 5.25 | V    |

| DVDD      | Digital Supply Voltage | 1.71 | 3.3 | AVDD | V    |

#### **Thermal Information**

| Package Type | θ <sub>JA</sub> | θ <sub>JC(TOP)</sub> | θЈВ   | Unit |

|--------------|-----------------|----------------------|-------|------|

| TSSOP16      | 104.93          | 23.04                | 73.46 | °C/W |

www.3peak.com 8 / 58 BA20240404A0

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **Electrical Characteristics**

All test conditions: AVDD = 5 V,  $V_{REF}$  = 4.096 V (internal), DVDD = 3.3 V,  $f_{SAMPLE}$  = 100 kSPS,

$T_A$  = -40 °C to 125 °C, unless otherwise noted.

| Parameter                             | Test Conditions                                      | Min                       | Тур | Max                      | Unit |

|---------------------------------------|------------------------------------------------------|---------------------------|-----|--------------------------|------|

| Analog Inputs                         |                                                      |                           |     |                          |      |

|                                       | Input range = ±3 × V <sub>REF</sub>                  | −3 × V <sub>REF</sub>     |     | 3 × V <sub>REF</sub>     |      |

|                                       | Input range = ±2.5 × V <sub>REF</sub>                | −2.5 × V <sub>REF</sub>   |     | 2.5 × V <sub>REF</sub>   |      |

|                                       | Input range = ±1.5 × V <sub>REF</sub>                | −1.5 × V <sub>REF</sub>   |     | 1.5 × V <sub>REF</sub>   |      |

|                                       | Input range = ±1.25 × V <sub>REF</sub>               | -1.25 × V <sub>REF</sub>  |     | 1.25 × V <sub>REF</sub>  |      |

| Input V <sub>IN</sub> Voltage Ranges  | Input range = ±0.75 × V <sub>REF</sub>               | −0.75 × V <sub>REF</sub>  |     | 0.75 × V <sub>REF</sub>  | .,   |

| V <sub>IN</sub> = AIN_P - AIN_N       | Input range = ±0.625 × V <sub>REF</sub>              | -0.625 × V <sub>REF</sub> |     | 0.625 × V <sub>REF</sub> | V    |

|                                       | Input range = 3 × V <sub>REF</sub>                   | 0                         |     | 3 × V <sub>REF</sub>     |      |

|                                       | Input range = 2.5 × V <sub>REF</sub>                 | 0                         |     | 2.5 × V <sub>REF</sub>   |      |

|                                       | Input range = 1.5 × V <sub>REF</sub>                 | 0                         |     | 1.5 × V <sub>REF</sub>   |      |

|                                       | Input range = 1.25 × V <sub>REF</sub>                | 0                         |     | 1.25 × V <sub>REF</sub>  |      |

|                                       | Input range = ±3 × V <sub>REF</sub>                  | −3 × V <sub>REF</sub>     |     | 3 × V <sub>REF</sub>     |      |

| AIN_P                                 | Input range = ±2.5 × V <sub>REF</sub>                | −2.5 × V <sub>REF</sub>   |     | 2.5 × V <sub>REF</sub>   | V    |

|                                       | Input range = ±1.5 × V <sub>REF</sub>                | −1.5 × V <sub>REF</sub>   |     | 1.5 × V <sub>REF</sub>   |      |

|                                       | Input range = ±1.25 × V <sub>REF</sub>               | -1.25 × V <sub>REF</sub>  |     | 1.25 × V <sub>REF</sub>  |      |

|                                       | Input range = ±0.75 × V <sub>REF</sub>               | −0.75 × V <sub>REF</sub>  |     | 0.75 × V <sub>REF</sub>  |      |

| Operating Input Range, Positive Input | Input range = ±0.625 × V <sub>REF</sub>              | -0.625 × V <sub>REF</sub> |     | 0.625 × V <sub>REF</sub> |      |

| 1 Ositive input                       | Input range = 3 × V <sub>REF</sub>                   | 0                         |     | 3 × V <sub>REF</sub>     |      |

|                                       | Input range = 2.5 × V <sub>REF</sub>                 | 0                         |     | 2.5 × V <sub>REF</sub>   |      |

|                                       | Input range = 1.5 × V <sub>REF</sub>                 | 0                         |     | 1.5 × V <sub>REF</sub>   |      |

|                                       | Input range = 1.25 × V <sub>REF</sub>                | 0                         |     | 1.25 × V <sub>REF</sub>  |      |

|                                       | Input range = ±3 × V <sub>REF</sub>                  | −3 × V <sub>REF</sub>     |     | 3 × V <sub>REF</sub>     |      |

|                                       | Input range = ±2.5 × V <sub>REF</sub>                | −2.5 × V <sub>REF</sub>   |     | 2.5 × V <sub>REF</sub>   |      |

|                                       | Input range = ±1.5 × V <sub>REF</sub>                | −1.5 × V <sub>REF</sub>   |     | 1.5 × V <sub>REF</sub>   |      |

|                                       | Input range = ±1.25 × V <sub>REF</sub>               | -1.25 × V <sub>REF</sub>  |     | 1.25 × V <sub>REF</sub>  |      |

| AIN_N                                 | Input range = ±0.75 × V <sub>REF</sub>               | -0.75 × V <sub>REF</sub>  |     | 0.75 × V <sub>REF</sub>  |      |

| Operating Input Range, Negative Input | Input range = ±0.625 × V <sub>REF</sub>              | -0.625 × V <sub>REF</sub> |     | 0.625 × V <sub>REF</sub> | V    |

| Wegative input                        | Input range = 3 × V <sub>REF</sub> <sup>(1)</sup>    | -0.1                      |     | 0.1                      |      |

|                                       | Input range = 2.5 × V <sub>REF</sub> <sup>(1)</sup>  | -0.1                      |     | 0.1                      |      |

|                                       | Input range = 1.5 × V <sub>REF</sub> <sup>(1)</sup>  | -0.1                      |     | 0.1                      |      |

|                                       | Input range = 1.25 × V <sub>REF</sub> <sup>(1)</sup> | -0.1                      |     | 0.1                      |      |

| Fully Differential Input Range (1)    | Input range = ±3 × V <sub>REF</sub>                  | −3 × V <sub>REF</sub>     |     | 3 × V <sub>REF</sub>     |      |

| V <sub>IN</sub> = AIN_P - AIN_N       | Input range = ±2.5 × V <sub>REF</sub>                | −2.5 × V <sub>REF</sub>   |     | 2.5 × V <sub>REF</sub>   | V    |

www.3peak.com 9 / 58 BA20240404A0

| F                        | Parameter                         | Test Conditions                         | Min                       | Тур  | Max                      | Unit   |

|--------------------------|-----------------------------------|-----------------------------------------|---------------------------|------|--------------------------|--------|

|                          |                                   | Input range = ±1.5 × V <sub>REF</sub>   | −1.5 × V <sub>REF</sub>   |      | 1.5 × V <sub>REF</sub>   |        |

|                          |                                   | Input range = ±1.25 × V <sub>REF</sub>  | −1.25 × V <sub>REF</sub>  |      | 1.25 × V <sub>REF</sub>  |        |

|                          |                                   | Input range = ±0.75 × V <sub>REF</sub>  | −0.75 × V <sub>REF</sub>  |      | 0.75 × V <sub>REF</sub>  |        |

|                          |                                   | Input range = ±0.625 × V <sub>REF</sub> | -0.625 × V <sub>REF</sub> |      | 0.625 × V <sub>REF</sub> |        |

|                          |                                   | Input range = ±3 × V <sub>REF</sub>     | -6.8                      |      | 6.5                      |        |

| Fully Differential Input |                                   | Input range = ±2.5 × V <sub>REF</sub>   | -6.8                      |      | 6.5                      |        |

|                          |                                   | Input range = ±1.5 × V <sub>REF</sub>   | -3.4                      |      | 4.9                      |        |

| Common-Mod               | le Input Range <sup>(1)</sup>     | Input range = ±1.25 × V <sub>REF</sub>  | -3.4                      |      | 4.9                      | V      |

|                          |                                   | Input range = ±0.75 × V <sub>REF</sub>  | -1.7                      |      | 4.1                      |        |

|                          |                                   | Input range = ±0.625 × V <sub>REF</sub> | -1.7                      |      | 4.1                      |        |

|                          | Input Impedance                   | All input ranges, T <sub>A</sub> = 25°C | 0.86                      | 1    | 1.17                     | Mohm   |

| Z <sub>IN</sub>          | Input Impedance Temperature Drift | All input ranges                        |                           | 7    |                          | ppm/°C |

|                          |                                   | Input range = ±2.5 × V <sub>REF</sub>   |                           | 8.8  |                          |        |

|                          | Input Leakage<br>Current          | Input range = ±1.25 × V <sub>REF</sub>  |                           | 3.3  |                          |        |

| Analog Input<br>Current  |                                   | Input range = ±0.625 × V <sub>REF</sub> |                           | 1.1  |                          | μA     |

| Current                  |                                   | Input range = 2.5 × V <sub>REF</sub>    |                           | 9.2  |                          |        |

|                          |                                   | Input range = 1.25 × V <sub>REF</sub>   |                           | 4.3  |                          |        |

| Input Overvo             | Itage Protection <sup>(1)</sup>   |                                         |                           |      |                          |        |

| Analog Input<br>Clamp    | Overvoltage Protection Voltage    | All input ranges                        | -30                       |      | 30                       | V      |

| Analog Input             | Filter                            |                                         |                           |      |                          |        |

| 3 4D D/W                 | Analog Input LPF                  | Low bandwidth                           |                           | 15   |                          | kU=    |

| −3 dB BW                 | Bandwidth −3 dB                   | High bandwidth                          |                           | 35   |                          | kHz    |

| -0.1 dB BW               | Analog Input LPF                  | Low bandwidth                           |                           | 2.5  |                          | kHz    |

| -0.1 UB BW               | Bandwidth −0.1 dB                 | High bandwidth                          |                           | 5.5  |                          | KIIZ   |

| System Perfo             | ormance                           |                                         |                           |      |                          |        |

| Resolution               |                                   |                                         | 16                        |      |                          | Bits   |

| NMC                      | No Missing Codes                  |                                         | 16                        |      |                          | Bits   |

| DNL                      | Differential<br>Nonlinearity      | All input ranges                        | -0.99                     | ±0.5 | 1                        | LSB    |

| INL                      | Integral Nonlinearity             | All input ranges                        | -2                        | ±1   | 2                        | LSB    |

| E <sub>G</sub>           |                                   | Input range = ±3 × V <sub>REF</sub>     | -0.02                     |      | 0.02                     |        |

|                          |                                   | Input range = ±2.5 × V <sub>REF</sub>   | -0.02                     |      | 0.02                     |        |

|                          | Gain Error                        | Input range = ±1.5 × V <sub>REF</sub>   | -0.18                     |      | 0.18                     | 0/ 505 |

|                          | At T <sub>A</sub> = 25°C          | Input range = ±1.25 × V <sub>REF</sub>  | -0.02                     |      | 0.02                     | %FSR   |

|                          |                                   | Input range = ±0.75 × V <sub>REF</sub>  | -0.18                     |      | 0.18                     |        |

|                          |                                   | Input range = ±0.625 × V <sub>REF</sub> | -0.02                     |      | 0.02                     |        |

|                   | Parameter                                      | Test Conditions                         | Min    | Тур    | Max   | Unit   |  |

|-------------------|------------------------------------------------|-----------------------------------------|--------|--------|-------|--------|--|

|                   |                                                | Input range = 3 × V <sub>REF</sub>      | -0.2   |        | 0.16  |        |  |

|                   |                                                | Input range = 2.5 × V <sub>REF</sub>    | -0.045 |        | 0.045 |        |  |

|                   |                                                | Input range = 1.5 × V <sub>REF</sub>    | -0.2   |        | 0.16  |        |  |

|                   |                                                | Input range = 1.25 × V <sub>REF</sub>   | -0.06  |        | 0.06  |        |  |

|                   | Gain Error<br>Temperature Drift <sup>(1)</sup> | All input ranges                        | -5     | 1      | 5     | ppm/°C |  |

|                   |                                                | Input range = ±3 × V <sub>REF</sub>     | -2.9   | ±0.375 | 2.9   |        |  |

|                   |                                                | Input range = ±2.5 × V <sub>REF</sub>   | -1.25  | ±0.32  | 1.25  |        |  |

|                   |                                                | Input range = ±1.5 × V <sub>REF</sub>   | -2.1   | ±0.56  | 2.1   |        |  |

|                   |                                                | Input range = ±1.25 × V <sub>REF</sub>  | -1.1   | ±0.47  | 1.1   |        |  |

| _                 | Offset Error                                   | Input range = ±0.75 × V <sub>REF</sub>  | -1.5   | ±0.375 | 1.5   |        |  |

| Eo                | At $T_A = 25^{\circ}C$ ,                       | Input range = ±0.625 × V <sub>REF</sub> | -0.8   | ±0.32  | 0.8   | mV     |  |

|                   |                                                | Input range = 3 × V <sub>REF</sub>      | -6.4   | ±0.375 | 5.3   |        |  |

|                   |                                                | Input range = 2.5 × V <sub>REF</sub>    | -0.5   | ±0.32  | 0.5   |        |  |

|                   |                                                | Input range = 1.5 × V <sub>REF</sub>    | -6.2   | ±0.47  | 5     |        |  |

|                   |                                                | Input range = 1.25 × V <sub>REF</sub>   | -1.2   | ±0.39  | 1.2   |        |  |

|                   | Offset Error<br>Temperature Drift (1)          | All input ranges                        | -4     | 1      | 4     | ppm/°C |  |

| Sampling          | ) Dynamics                                     |                                         |        |        |       | ,      |  |

| $t_{\text{CONV}}$ | Conversion Time                                |                                         |        |        | 5     | μs     |  |

| t <sub>ACQ</sub>  | Acquisition Time                               |                                         | 5      |        |       | μs     |  |

| fs                | Maximum Throughput Rate without Latency        |                                         |        | 100    |       | kSPS   |  |

| Dynamic           | Characteristics                                |                                         |        |        |       |        |  |

| SNR               | Low Bandwidth                                  | Input range = ±3 × V <sub>REF</sub>     | 88.5   | 90.5   |       |        |  |

|                   | -0.5 dBFS 1 kHz                                | Input range = ±2.5 × V <sub>REF</sub>   | 88.2   | 89.9   |       |        |  |

|                   | Input                                          | Input range = ±1.5 × V <sub>REF</sub>   | 87.8   | 90     |       |        |  |

|                   |                                                | Input range = ±1.25 × V <sub>REF</sub>  | 87.4   | 89.4   |       |        |  |

|                   |                                                | Input range = ±0.75 × V <sub>REF</sub>  | 86.6   | 88.9   |       |        |  |

|                   |                                                | Input range = ±0.625 × V <sub>REF</sub> | 85.8   | 88.3   |       | dB     |  |

|                   |                                                | Input range = 3 × V <sub>REF</sub>      | 87.4   | 89.8   |       |        |  |

|                   |                                                | Input range = 2.5 × V <sub>REF</sub>    | 86.9   | 89     |       |        |  |

|                   |                                                | Input range = 1.5 × V <sub>REF</sub>    | 85.7   | 88.2   |       |        |  |

|                   |                                                | Input range = 1.25 × V <sub>REF</sub>   | 85.0   | 87.1   |       |        |  |

|                   | High Bandwidth                                 | Input range = ±3 × V <sub>REF</sub>     |        | 90     |       |        |  |

|                   | -0.5 dBFS 1 kHz                                | Input range = ±2.5 × V <sub>REF</sub>   |        | 90     |       | dB     |  |

|                   | Input                                          | Input range = ±1.5 × V <sub>REF</sub>   |        | 90     |       |        |  |

|       | Parameter       | Test Conditions                         | Min                   | Тур  | Max | Unit |

|-------|-----------------|-----------------------------------------|-----------------------|------|-----|------|

|       |                 | Input range = ±1.25 × V <sub>REF</sub>  |                       | 89   |     |      |

|       |                 | Input range = ±0.75 × V <sub>REF</sub>  |                       | 89   |     |      |

|       |                 | Input range = ±0.625 × V <sub>REF</sub> |                       | 88   |     |      |

|       |                 | Input range = 3 × V <sub>REF</sub>      |                       | 88   |     |      |

|       |                 | Input range = 2.5 × V <sub>REF</sub>    |                       | 88   |     |      |

|       |                 | Input range = 1.5 × V <sub>REF</sub>    |                       | 86   |     |      |

|       |                 | Input range = 1.25 × V <sub>REF</sub>   |                       | 85   |     |      |

| THD   | Low Bandwidth   | Input range = ±3 × V <sub>REF</sub>     |                       | -103 |     |      |

|       | -0.5 dBFS 1 kHz | Input range = ±2.5 × V <sub>REF</sub>   |                       | -103 |     |      |

|       | Input           | Input range = ±1.5 × V <sub>REF</sub>   |                       | -103 |     |      |

|       |                 | Input range = ±1.25 × V <sub>REF</sub>  |                       | -103 |     |      |

|       |                 | Input range = ±0.75 × V <sub>REF</sub>  |                       | -103 |     | T    |

|       |                 | Input range = ±0.625 × V <sub>REF</sub> |                       | -103 |     | dB   |

|       |                 | Input range = 3 × V <sub>REF</sub>      |                       | -103 |     |      |

|       |                 | Input range = 2.5 × V <sub>REF</sub>    |                       | -103 |     | 1    |

|       |                 | Input range = 1.5 × V <sub>REF</sub>    | V <sub>REF</sub> -103 |      |     |      |

|       |                 | Input range = 1.25 × V <sub>REF</sub>   |                       | -103 |     |      |

|       | High Bandwidth  | Input range = ±3 × V <sub>REF</sub>     |                       | -100 |     |      |

|       | -0.5 dBFS 1 kHz | Input range = ±2.5 × V <sub>REF</sub>   |                       | -100 |     |      |

|       | Input           | Input range = ±1.5 × V <sub>REF</sub>   |                       | -100 |     |      |

|       |                 | Input range = ±1.25 × V <sub>REF</sub>  |                       | -100 |     |      |

|       |                 | Input range = ±0.75 × V <sub>REF</sub>  |                       | -100 |     |      |

|       |                 | Input range = ±0.625 × V <sub>REF</sub> |                       | -100 |     | dB   |

|       |                 | Input range = 3 × V <sub>REF</sub>      |                       | -100 |     |      |

|       |                 | Input range = 2.5 × V <sub>REF</sub>    |                       | -100 |     |      |

|       |                 | Input range = 1.5 × V <sub>REF</sub>    |                       | -100 |     |      |

|       |                 | Input range = 1.25 × V <sub>REF</sub>   |                       | -100 |     |      |

| SINAD | Low Bandwidth   | Input range = ±3 × V <sub>REF</sub>     | 86.3                  | 90   |     |      |

|       | -0.5 dBFS 1 kHz | Input range = ±2.5 × V <sub>REF</sub>   | 85.9                  | 89.7 |     |      |

|       | Input           | Input range = ±1.5 × V <sub>REF</sub>   | 86.1                  | 89.8 |     |      |

|       |                 | Input range = ±1.25 × V <sub>REF</sub>  | 85.5                  | 89.2 |     |      |

|       |                 | Input range = ±0.75 × V <sub>REF</sub>  | 84.6                  | 88.8 |     | -15  |

|       |                 | Input range = ±0.625 × V <sub>REF</sub> | 83.9                  | 88.2 |     | ⊢ dB |

|       |                 | Input range = 3 × V <sub>REF</sub>      | 85.5                  | 89.6 |     |      |

|       |                 | Input range = 2.5 × V <sub>REF</sub>    | 85.2                  | 88.8 |     |      |

|       |                 | Input range = 1.5 × V <sub>REF</sub>    | 84.0                  | 88.1 |     |      |

|       |                 | Input range = 1.25 × V <sub>REF</sub>   | 82.7                  | 87   |     |      |

| ı                       | Parameter                                     | Test Conditions                                                         | Min   | Тур   | Max   | Unit   |

|-------------------------|-----------------------------------------------|-------------------------------------------------------------------------|-------|-------|-------|--------|

|                         | High Bandwidth                                | Input range = ±3 × V <sub>REF</sub>                                     |       | 89    |       |        |

|                         | -0.5 dBFS 1 kHz                               | Input range = ±2.5 × V <sub>REF</sub>                                   |       | 89    |       |        |

|                         | Input                                         | Input range = ±1.5 × V <sub>REF</sub>                                   |       | 89    |       |        |

|                         |                                               | Input range = ±1.25 × V <sub>REF</sub>                                  |       | 89    |       |        |

|                         |                                               | Input range = ±0.75 × V <sub>REF</sub>                                  |       | 88    |       | -ID    |

|                         |                                               | Input range = ±0.625 × V <sub>REF</sub>                                 |       | 88    |       | dB     |

|                         |                                               | Input range = 3 × V <sub>REF</sub>                                      |       | 89    |       |        |

|                         |                                               | Input range = 2.5 × V <sub>REF</sub>                                    |       | 89    |       |        |

|                         |                                               | Input range = 1.5 × V <sub>REF</sub>                                    |       | 87    |       |        |

|                         |                                               | Input range = 1.25 × V <sub>REF</sub>                                   |       | 86    |       |        |

| Internal Refe           | rence Output                                  |                                                                         |       |       |       |        |

| V <sub>REFIO_INT</sub>  | REFIO Voltage                                 | Voltage on REFIO pin<br>(configured as output)<br>T <sub>A</sub> = 25°C | 4.088 | 4.096 | 4.104 | V      |

|                         | Reference<br>Temperature Drift <sup>(1)</sup> |                                                                         |       | 5     | 10    | ppm/°C |

| C <sub>OUT_REFIO</sub>  | Decoupling Capacitor on REFIO                 |                                                                         |       | 0.1   |       | μF     |

| VREFCAP                 | Reference Voltage                             | Reference voltage to ADC (on REFCAP pin) T <sub>A</sub> = 25°C          | 4.091 | 4.096 | 4.101 | V      |

|                         | Reference Buffer<br>Output Impedance          |                                                                         |       | 0.5   |       | Ω      |

|                         | Reference Buffer<br>Temperature Drift         |                                                                         |       | 1     |       | ppm/°C |

| C <sub>OUT_REFCAP</sub> | Decoupling Capacitor on REFIO                 |                                                                         |       | 10    |       | μF     |

| ton                     | Reference Turn-on Time                        | C <sub>OUT_REFIO</sub> = 0.1µF<br>C <sub>OUT_REFCAP</sub> = 10µF        |       | 10    |       | ms     |

| External Refe           | erence Input                                  |                                                                         |       |       |       |        |

| Vrefio_ext              | External Reference                            | External reference voltage on REFIO (configured as input)               | 4.046 | 4.096 | 4.146 | V      |

| Power-suppl             | y Requirements                                |                                                                         |       |       |       |        |

| AVDD                    | Analog Power-supply<br>Voltage                | Analog supply                                                           | 4.75  | 5     | 5.25  | V      |

|                         | Digital Power supply                          | Digital supply range                                                    | 1.65  | 3.3   | AVDD  | V      |

| DVDD                    | Digital Power-supply<br>Voltage               | Digital supply range for specified performance                          | 2.7   | 3.3   | 5.25  | V      |

|                                | Parameter                         | Test Conditions                                             | Min        | Тур | Max        | Unit |

|--------------------------------|-----------------------------------|-------------------------------------------------------------|------------|-----|------------|------|

| I <sub>AVDD_DYN</sub>          | AVDD Dynamic                      | AVDD = 5 V, f <sub>S</sub> = maximum and internal reference |            | 9   | 9.5        | mA   |

| I <sub>AVDD_STC</sub>          | AVDD Static                       | Device not converting and internal reference                |            | 8.5 | 9.3        | mA   |

| ISTDBY                         | Standby                           | At AVDD = 5 V, device in STDBY mode and internal reference  |            | 7   |            | mA   |

| I <sub>PWR_DN</sub>            | Power-down                        | At AVDD = 5 V, device in PWR_DN                             |            | 2.8 | 200        | μA   |

| I <sub>DVDD_DYN</sub>          | Digital Supply<br>Current         | At DVDD = 3.3 V, output = 0000                              |            | 0.1 |            | mA   |

| Digital Input                  | s (CMOS)                          |                                                             |            |     |            |      |

| V <sub>IH</sub>                | Digital Input Logic               | DVDD > 0.4 V                                                | 0.7 x DVDD |     | DVDD + 0.3 | V    |

| V <sub>IL</sub>                | Levels                            | DVDD > 2.1 V                                                | -0.3       |     | 0.3 x DVDD | V    |

| V <sub>IH</sub>                | Digital Input Logic               | DVDD < 0.4.V                                                | 0.8 x DVDD |     | DVDD + 0.3 | V    |

| VIL                            | Levels                            | DVDD ≤ 2.1 V                                                | -0.3       |     | 0.2 x DVDD | V    |

| Input Leakag                   | e Current                         |                                                             |            | 100 |            | nA   |

| Input Capacit                  | tance                             |                                                             |            | 5   |            | pF   |

| Digital Outpo                  | uts (CMOS)                        |                                                             |            |     |            |      |

| V <sub>OH</sub>                | Digital Output Logic              | I <sub>O</sub> = 500-μA source                              | 0.8 x DVDD |     | DVDD       | V    |

| VoL                            | Levels                            | I <sub>0</sub> = 500-μA sink                                | 0          |     | 0.2 x DVDD | V    |

| Floating State Leakage Current |                                   | Only for SDO                                                |            | 1   |            | μA   |

| Internal Pin C                 | Capacitance                       |                                                             |            | 5   |            | pF   |

| Temperature                    | Range                             |                                                             |            |     |            |      |

| TA                             | Operating Free-air<br>Temperature |                                                             | -40        |     | 125        | °C   |

<sup>(1)</sup> These specifications are not production tested but are supported by characterization data at the initial product release.

www.3peak.com 14 / 58 BA20240404A0

### Timing Requirements (1)

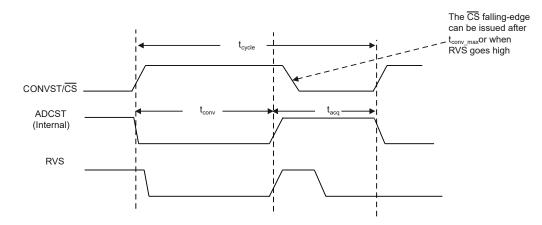

#### **Conversion Cycle Timing Specifications**

AVDD = 5 V, DVDD = 5 V, VREF = 4.096 V internal reference, fsample = 100 kSPS, Ta = 25°C, unless otherwise noted.

|                    | Parameter             |                      |  | Max | Unit |

|--------------------|-----------------------|----------------------|--|-----|------|

| Timing S           | pecifications         |                      |  |     |      |

| f <sub>cycle</sub> | Sampling frequency    |                      |  | 100 | kSPS |

| t <sub>cycle</sub> | ADC cycle time period | 1/f <sub>cycle</sub> |  |     | μs   |

| f <sub>acq</sub>   | Acquisition time      | 5                    |  |     | μs   |

| t <sub>CONV</sub>  | Conversion time       |                      |  | 5   | μs   |

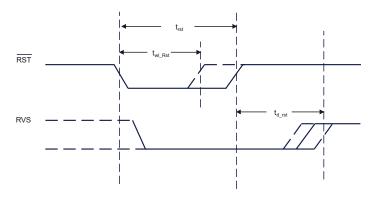

#### **Asynchronous Reset Timing Specifications**

AVDD = 5 V, DVDD = 5 V,  $V_{REF}$  = 4.096 V internal reference,  $f_{SAMPLE}$  = 100 kSPS,  $T_A$  = -40°C to +125°C, unless otherwise noted.

|                        | Parameter                                                        |     |    | Max | Unit |

|------------------------|------------------------------------------------------------------|-----|----|-----|------|

| Timing Spe             | cifications                                                      |     |    |     |      |

| t <sub>wl_RST</sub>    | Pulse duration: RST low                                          | 100 |    |     | ns   |

| t <sub>D_RST_POR</sub> | Delay time for POR reset: RST rising to RVS rising               |     | 20 |     | ms   |

| t <sub>D_RST_APP</sub> | Delay time for application reset: RST rising to CONVST/CS rising |     |    | 1   | μs   |

| t <sub>NAP_WKUP</sub>  | Wake-up time: NAP mode                                           |     |    | 20  | μs   |

| tpwrup                 | Power-up time: PD mode                                           |     | 20 |     | ms   |

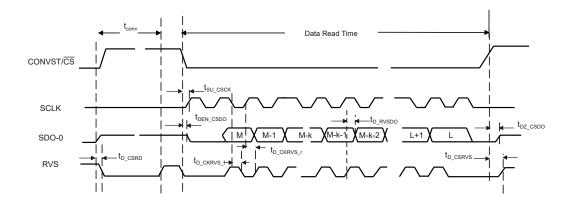

#### **SPI-Compatible Serial Interface Timing Specifications**

AVDD = 5 V, DVDD = 5 V,  $V_{REF}$  = 4.096 V internal reference,  $f_{SAMPLE}$  = 100 kSPS,  $T_A$  = -40°C to +125°C, unless otherwise noted.

|                       | Parameter                                                    | Min                  | Тур | Max   | Unit             |

|-----------------------|--------------------------------------------------------------|----------------------|-----|-------|------------------|

| Timing Spe            | ecifications                                                 |                      |     |       |                  |

| fclk                  | Serial clock frequency                                       |                      |     | 66.67 | MHz              |

| t <sub>CLK</sub>      | Serial clock time period                                     | 1/f <sub>cycle</sub> |     |       |                  |

| t <sub>PH_CK</sub>    | SCLK high time                                               | 0.45                 |     | 0.55  | t <sub>CLK</sub> |

| t <sub>PL_CK</sub>    | SCLK low time                                                | 0.45                 |     | 0.55  | tclk             |

| t <sub>SU_CSCK</sub>  | Setup time: CONVST/CS falling to first SCLK capture edge     | 7.5                  |     |       | ns               |

| t <sub>SU_CKDI</sub>  | Setup time: SDI data valid to SCLK capture edge              | 7.5                  |     |       | ns               |

| tht_ckdi              | Hold time: SCLK capture edge to (previous) data valid on SDI | 7.5                  |     |       | ns               |

| t <sub>HT_CKCS</sub>  | Delay time: last SCLK capture edge to CONVST/CS rising       | 7.5                  |     |       | ns               |

| t <sub>DEN_CSDO</sub> | Delay time: CONVST/CS falling edge to data enable            |                      |     | 9.5   | ns               |

| t <sub>DZ_CSDO</sub>  | Delay time: CONVST/CS rising to SDO-x going to 3-state       |                      |     | 10    | ns               |

www.3peak.com 15 / 58 BA20240404A0

|                      | Parameter                                                  |  | Тур | Max | Unit |

|----------------------|------------------------------------------------------------|--|-----|-----|------|

| t <sub>D_CKDO</sub>  | Delay time: SCLK launch edge to (next) data valid on SDO-x |  |     | 12  | ns   |

| t <sub>D_CSRVS</sub> | Delay time: CONVST/CS rising edge to RVS falling           |  |     | 14  | ns   |

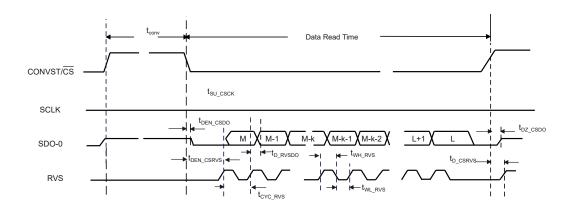

#### Timing Requirements: Source-Synchronous Serial Interface (External Clock)

AVDD = 5 V, DVDD = 5 V,  $V_{REF}$  = 4.096 V internal reference,  $f_{SAMPLE}$  = 100 kSPS,  $T_A$  = -40°C to +125°C, unless otherwise noted.

|                        | Parameter                                                                 | Min                  | Тур | Max   | Unit             |  |

|------------------------|---------------------------------------------------------------------------|----------------------|-----|-------|------------------|--|

| Timing Specifications  |                                                                           |                      |     |       |                  |  |

| f <sub>CLK</sub>       | Serial clock frequency                                                    |                      |     | 66.67 | MHz              |  |

| t <sub>CLK</sub>       | Serial clock time period                                                  | 1/f <sub>cycle</sub> |     |       |                  |  |

| t <sub>PH_CK</sub>     | SCLK high time                                                            | 0.45                 |     | 0.55  | t <sub>CLK</sub> |  |

| t <sub>PL_CK</sub>     | SCLK low time                                                             | 0.45                 |     | 0.55  | t <sub>CLK</sub> |  |

| t <sub>DEN_CSDO</sub>  | Delay time: CONVST/CS falling edge to data enable                         |                      |     | 9.5   | ns               |  |

| t <sub>DZ_CSDO</sub>   | Delay time: CONVST/CS rising to SDO-x going to 3-state                    |                      |     | 10    | ns               |  |

| t <sub>D_CKRVS_r</sub> | Delay time: SCLK rising edge to RVS rising                                |                      |     | 14    | ns               |  |

| t <sub>D_CKRVS_f</sub> | Delay time: SCLK falling edge to RVS falling                              |                      |     | 14    | ns               |  |

| t <sub>D_RVSDO</sub>   | Delay time: RVS rising to (next) data valid on SDO-x                      |                      |     | 2.5   | ns               |  |

| t <sub>D_CSRVS</sub>   | Delay time: CONVST/CS rising edge to RVS displaying internal device state |                      |     | 15    | ns               |  |

#### Timing Requirements: Source-Synchronous Serial Interface (Internal Clock)

AVDD = 5 V, DVDD = 5 V,  $V_{REF}$  = 4.096 V internal reference,  $f_{SAMPLE}$  = 100 kSPS,  $T_A$  = -40°C to +125°C, unless otherwise noted.

|                        | Parameter                                                                 |     |  | Max | Unit                |

|------------------------|---------------------------------------------------------------------------|-----|--|-----|---------------------|

| Timing Spe             | cifications                                                               |     |  |     |                     |

| t <sub>DEN_CSDO</sub>  | Delay time: CONVST/CS falling edge to data enable                         |     |  | 9.5 | ns                  |

| t <sub>DZ_CSDO</sub>   | Delay time: CONVST/CS rising to SDO-x going to 3-state                    |     |  | 10  | ns                  |

| t <sub>DEN_CSRVS</sub> | Delay time: CONVST/CS falling edge to first rising edge on RVS            |     |  | 50  | ns                  |

| t <sub>D_RVSDO</sub>   | Delay time: RVS rising to (next) data valid on SDO-x                      |     |  | 2.5 | ns                  |

| t <sub>INTCLK</sub>    | Time period: internal clock                                               | 15  |  |     |                     |

| t <sub>CYC_RVS</sub>   | Time period: RVS signal                                                   | 15  |  | 15  | ns                  |

| twh_Rvs                | RVS high time                                                             | 0.4 |  | 0.6 | tINTCLK             |

| t <sub>WL_RVS</sub>    | RVS low time                                                              | 0.4 |  | 0.6 | t <sub>INTCLK</sub> |

| t <sub>D_CSRVS</sub>   | Delay time: CONVST/CS rising edge to RVS displaying internal device state |     |  | 15  | ns                  |

(1) Parameters are preliminary and provided by design simulation.

www.3peak.com 16 / 58 BA20240404A0

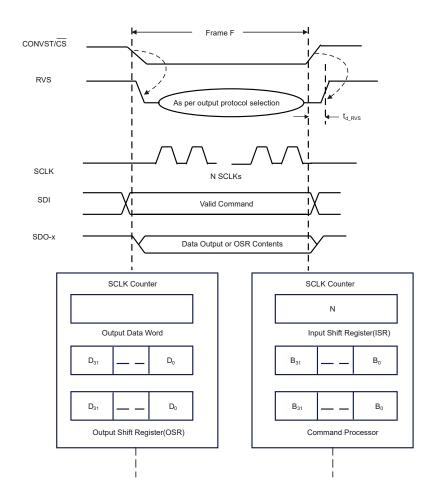

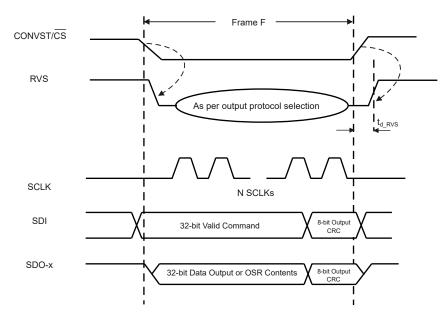

Figure 1. Conversion Cycle Timing Diagram

Figure 2. Asynchronous Reset Timing Diagram

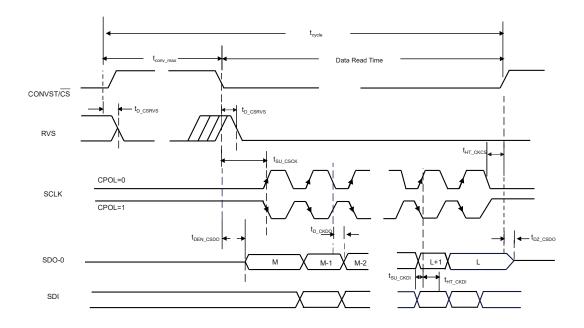

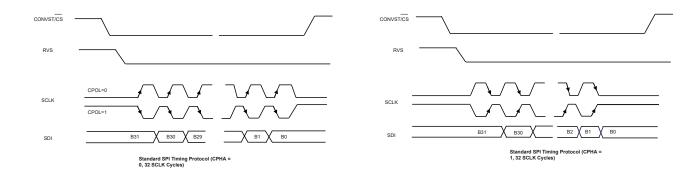

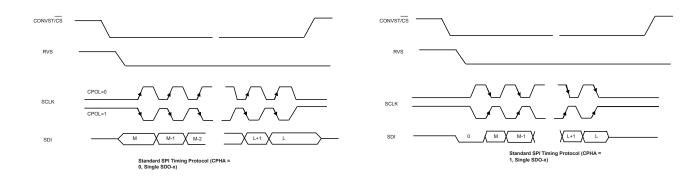

Figure 3. Standard SPI Interface Timing Diagram for CPHA = 0

www.3peak.com 17 / 58 BA20240404A0

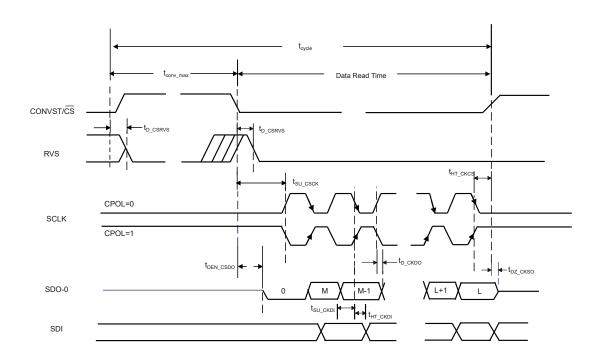

Figure 4. Standard SPI Interface Timing Diagram for CPHA = 1

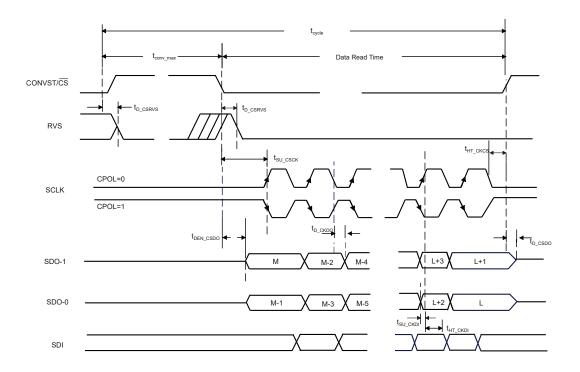

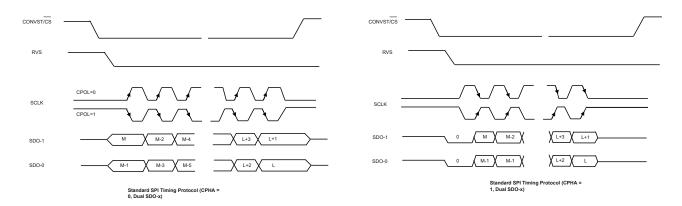

Figure 5. MultiSPI Interface Timing Diagram for Dual SDO-x and CPHA = 0

www.3peak.com 18 / 58 BA20240404A0

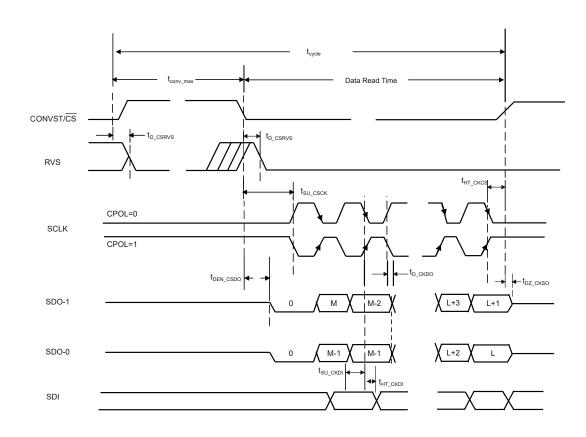

Figure 6. MultiSPI Interface Timing Diagram for Dual SDO-x and CPHA = 1

Figure 7. MultiSPI Source-Synchronous External Clock Serial Interface Timing Diagram

www.3peak.com 19 / 58 BA20240404A0

Figure 8. MultiSPI Source-Synchronous Internal Clock Serial Interface Timing Diagram

www.3peak.com 20 / 58 BA20240404A0

### **Typical Performance Characteristics**

All test conditions: at  $T_A$  = 25°C, AVDD = 5 V, DVDD = 5 V, VREF = 4.096 V (internal), and maximum throughput (unless otherwise noted).

www.3peak.com 21 / 58 BA20240404A0

### **Detailed Description**

#### Overview

The TPAFE51716S is a 16-bit data acquisition system with single analog input channels. Each input channel includes input protection circuitry, a programmable gain amplifier (PGA), an analog low-pass filter, and an analog-to-digital converter (ADC) driver with ADC operating on 100 KSPS throughput rate. The device incorporates a 4.096V internal reference with a fast-settling buffer. It also provides high-speed serial interfaces for communication with a daisy-chain function, making it suitable for a wide range of data acquisition applications.

The device operates with a single 5-V analog supply and can process true bipolar input signals. It provides a programmable analog signal range, including options for true bipolar single-ended  $\pm 12.288$  V,  $\pm 10.24$  V,  $\pm 6.144$  V,  $\pm 5.12$  V,  $\pm 3.072$  V,  $\pm 2.56$  V, unipolar single-ended 0 V - 12.288 V, 0 V - 10.24 V, 0 V - 6.144 V, 0 V - 5.12 V, and true bipolar fully-differential  $\pm 12.288$  V,  $\pm 10.24$  V,  $\pm 6.144$  V,  $\pm 5.12$  Vinput signals. The input clamp protection circuitry can protect the device from being damaged by voltages as high as  $\pm 30$  V. The device features a constant 1-M $\Omega$  resistive input impedance.

#### **Functional Block Diagram**

Figure 18. TPAFE51716S Block Diagram

www.3peak.com 23 / 58 BA20240404A0

#### **Feature Description**

#### **Analog Inputs**

The TPAFE51716 incorporates a 16-bit successive approximation register (SAR) analog-to-digital converter (ADC). The device comprises one analog input pairs. The ADC is responsible for converting the voltage difference between the analog input pair AIN\_P – AIN\_N. The simplified circuit schematic for each analog input channel is shown in a function block diagram, encompassing the input clamp protection circuit, PGA, low-pass filter, high-speed ADC driver, and a precision 16-bit SAR ADC.

#### **Analog Input Ranges**

The TPAFE51716 can handle true bipolar differential, bipolar single-ended, and unipolar single-ended input voltages. It is possible to configure an individual analog input range per channel, from the range select registers.

The devices sample the voltage difference  $(AIN_P - AIN_N)$  between the selected analog input pairs. This feature is beneficial in modular systems where the sensor or signal-conditioning block is located at a distance from the ADC on the board. It proves particularly useful when there might be a difference in the ground potential between the sensor or signal conditioner and the ADC ground. In such cases, it is recommended to run separate wires from the AIN\_N pin of the device to the sensor or signal-conditioning ground.

In single-ended mode, the AIN\_N pins are typically connected to analog ground and allow a ±0.1 V range referred to ground.

In differential mode, the AIN\_P and AIN\_N typically sense the fully differential input signals within a certain input common mode range. Also, this feature is beneficial in modular systems where the sensor or signal-conditioning block is located at a distance from the ADC on the board. It proves particularly useful when there might be a difference in the ground potential between the sensor or signal conditioner and the ADC ground. In such cases, it is recommended to run separate wires from the AIN N pin of the device to the sensor or signal-conditioning ground.

#### **Analog Input Impedance**

The TPAFE51716 features a fixed high analog input impedance of 1 M $\Omega$ , which is nearly constant at different sampling frequencies. It eliminates the need for an external driver amplifier, allowing direct connection to the source or sensor.

#### **Analog Input Clamp Protection**

The TPAFE51716 incorporates an internal clamp protection circuit on each of the analog input channels. This protection circuit allows each analog input voltage to swing up to ±30 V. Beyond this threshold, the input clamp circuit activates while still operating from a single 5 V supply.

To ensure that the input current stays within safe limits (±10 mA) for input voltages above the clamp threshold, it is advisable to use a series resistor with the analog inputs. This resistor can serve the dual purpose of limiting input current and providing an antialiasing low-pass filter (LPF) when combined with a capacitor. Matching the external source impedance on the AIN\_P and AIN\_N pins helps cancel any additional offset error. However, it's advisable to avoid prolonged activation of the clamp protection circuitry during normal or power-down conditions for optimal device performance.

#### **Programmable Gain Amplifier (PGA)**

The TPAFE51716 includes a PGA at each analog input channel, providing support for both unipolar/bipolar single-ended and bipolar differential inputs. The supported analog input ranges are listed below. The input range is set by the RANGE\_SEL[3:0] bits in the configuration register.

www.3peak.com 24 / 58 BA20240404A0

Table 2. Analog Input Ranges

| A I               | A                            |       | RANGE_ | RANGE_SEL[3:0] |       |  |  |  |

|-------------------|------------------------------|-------|--------|----------------|-------|--|--|--|

| Analog Input Mode | Analog Input Range           | BIT 3 | BIT 2  | BIT 1          | BIT 0 |  |  |  |

| Single-ended      | ±3 x V <sub>REF</sub>        | 0     | 0      | 0              | 0     |  |  |  |

| Single-ended      | ±2.5 x V <sub>REF</sub>      | 0     | 0      | 0              | 1     |  |  |  |

| Single-ended      | ±1.5 x V <sub>REF</sub>      | 0     | 0      | 1              | 0     |  |  |  |

| Single-ended      | ±1.25 x V <sub>REF</sub>     | 0     | 0      | 1              | 1     |  |  |  |

| Single-ended      | ±0.625 x V <sub>REF</sub>    | 0     | 1      | 0              | 0     |  |  |  |

| Single-ended      | ±0.75 x V <sub>REF</sub>     | 0     | 1      | 0              | 1     |  |  |  |

| Differential      | ±3 x V <sub>REF</sub>        | 0     | 1      | 1              | 0     |  |  |  |

| Differential      | ±2.5 x V <sub>REF</sub>      | 0     | 1      | 1              | 1     |  |  |  |

| Single-ended      | 0 to 3 x V <sub>REF</sub>    | 1     | 0      | 0              | 0     |  |  |  |

| Single-ended      | 0 to 2.5 x V <sub>REF</sub>  | 1     | 0      | 0              | 1     |  |  |  |

| Single-ended      | 0 to 1.5 x V <sub>REF</sub>  | 1     | 0      | 1              | 0     |  |  |  |

| Single-ended      | 0 to 1.25 x V <sub>REF</sub> | 1     | 0      | 1              | 1     |  |  |  |

| Differential      | ±1.5 x V <sub>REF</sub>      | 1     | 1      | 0              | 0     |  |  |  |

| Differential      | ±1.25 x V <sub>REF</sub>     | 1     | 1      | 0              | 1     |  |  |  |

| Differential      | ±0.75 x V <sub>REF</sub>     | 1     | 1      | 1              | 0     |  |  |  |

| Differential      | ±0.625 x V <sub>REF</sub>    | 1     | 1      | 1              | 1     |  |  |  |

The analog input channel on the TPAFE51716 is equipped with an antialiasing low-pass filter (LPF) situated at the PGA output. The following table outlines the programmable LPF options associated with the analog input range in the device. The analog input bandwidth for all eight channels can be chosen using the LPF\_CONFIG[1:0] bits found in address 0x34.

Table 3. Low-Pass Filter Corner Frequency

| LPF            | Analog Input Range | Typical −3 dB Bandwidth |

|----------------|--------------------|-------------------------|

| Low-bandwidth  | All input ranges   | 15 kHz                  |

| High-bandwidth | All input ranges   | 35 kHz                  |

#### Reference

The TPAFE51716 can operate with either an internal voltage reference or an external voltage reference, utilizing the internal buffer. The configuration between internal and external reference is controlled by programming the INTREF\_DIS bit of the RANGE\_SEL\_REG register. The devices incorporate a built-in buffer amplifier designed to drive the reference input of the internal ADC core, optimizing overall performance.

#### **Internal Reference**

The TPAFE51716 includes an on-chip  $4.096\ V$  reference, which can be accessed through the REFIO pin. The SAR ADC utilizes this internally generated and buffered  $4.096\ V$  reference for its conversions. To select the internal reference, program the INTREF\_DIS bit of the RANGE\_SEL\_REG register. The internal reference is enabled (INTREF\_DIS = 0) by default after reset or powering up. The INTREF\_DIS bit must be set to 1 to disable the internal reference source if an external reference source is used. In this configuration, the REFIO pin serves as an output pin, providing the internal reference value. It is recommended to place a  $10\ \mu\text{F}$  and a  $0.1\ \mu\text{F}$  decoupling capacitor between the REFIO pin and REFGND. Place the capacitor

www.3peak.com 25 / 58 BA20240404A0

as close to the REFIO pin as possible. The capacitors act as decoupling components and form a low-pass filter with the output impedance of the internal band-gap circuit, limiting the noise of the reference. Avoid using the REFIO pin to drive external loads, as REFIO has limited current output capability. If needed as a source, it can be followed by an operational amplifier buffer.

#### **External Reference**

Alternatively, the TPAFE51716 can accept an external reference voltage applied to the REFIO pin. When an external 4.096 V reference is provided, the device internally amplifies it to create the 4.096 V buffered reference used by the SAR ADC. To select external reference mode, , the INTREF\_DIS bit of the RANGE\_SEL\_REG register must be set to 1. In this mode, an external 4.096-V reference should be applied at REFIO, which becomes an input pin. The user can use any external reference in this mode. The internal buffer is designed to handle dynamic loading on the REFCAP pin, which is internally connected to the ADC reference input. When using an external reference, it's important to appropriately filter the reference output to minimize its impact on system performance.

The output of the internal reference buffer is present at the REFCAP pin. To ensure proper operation, decoupling capacitors of 22  $\mu$ F and 0.1  $\mu$ F must be connected between REFCAP and REFGND. It's important not to use the internal buffer to drive any external loads due to the limited current output capability of this buffer.

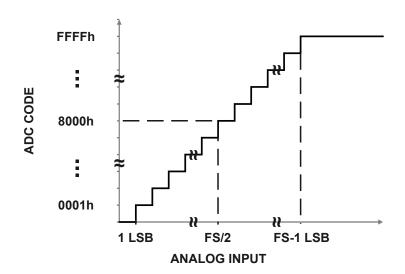

#### **ADC Transfer Function**

The TPAFE51716 outputs 16 bits of conversion data in straight binary format for all ranges and all modes (unipolar/bipolar). The full-scale range (FSR) for each input signal is determined by the difference between the positive full-scale (PFS) input voltage and the negative full-scale (NFS) input voltage. The size of the least significant bit (LSB) is calculated as FSR /  $2^16$  = FSR / 65536 for the 16-bit resolution of the ADC. In the case of a reference voltage (V<sub>REF</sub>) set to 4.096 V, the LSB values for various input ranges are as follows:

Figure 19. Device Transfer Function (Straight-Binary Format)

**Table 4. Transfer Characteristics**

| Input Range             | NFS (V) | PFS (V) FSR (V) |        | LSB (μV) |  |

|-------------------------|---------|-----------------|--------|----------|--|

| ±3 x V <sub>REF</sub>   | -12.288 | 12.288          | 24.576 | 375      |  |

| ±2.5 x V <sub>REF</sub> | -10.24  | 10.24           | 20.48  | 312.5    |  |

| ±1.5 x V <sub>REF</sub> | -6.144  | 6.144           | 12.288 | 187.5    |  |

www.3peak.com 26 / 58 BA20240404A0

| Input Range                  | NFS (V) | PFS (V) | FSR (V) | LSB (μV) |

|------------------------------|---------|---------|---------|----------|

| ±1.25 x V <sub>REF</sub>     | -5.12   | 5.12    | 10.24   | 156.25   |

| ±0.75 x V <sub>REF</sub>     | -3.072  | 3.072   | 6.144   | 93.75    |

| ±0.625 x V <sub>REF</sub>    | -2.56   | 2.56    | 5.12    | 78.125   |

| 0 to 3 x V <sub>REF</sub>    | 0       | 12.288  | 12.288  | 187.5    |

| 0 to 2.5 x V <sub>REF</sub>  | 0       | 10.24   | 10.24   | 156.25   |

| 0 to 1.5 x V <sub>REF</sub>  | 0       | 6.144   | 6.144   | 93.75    |

| 0 to 1.25 x V <sub>REF</sub> | 0       | 5.12    | 5.12    | 78.125   |

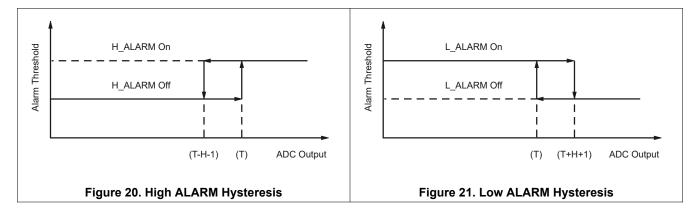

#### **Alarm Feature**

The device includes an active-high alarm output on the ALARM/SDO-1/GPO pin when configured for alarm functionality. To enable the ALARM output on this multifunction pin, set the SDO1\_CONFIG[1:0] bits in the SDO\_CTL\_REG register to 01b.

The device supports two alarm functions: an input alarm and an AVDD alarm.

- The input alarm monitors the ADC input voltage and compares it to user-programmable high and low thresholds. An active-high alarm output is triggered if the value of the input signal exceeds these thresholds.

- The AVDD alarm monitors the ADC's analog supply voltage and compares it to programmed low and high thresholds. An active-high alarm output is triggered if AVDD crosses either threshold in any direction.

When the alarm functionality is turned on, both the input and AVDD alarm functions are enabled by default. These alarm functions can be selectively disabled by programming the IN\_AL\_DIS and VDD\_AL\_DIS bits(respectively) of the RST PWRCTL REG register

Each alarm, whether input or AVDD, has two associated flags: the active alarm flag and the tripped alarm flag, both readable in the ALARM\_REG register. When an alarm is triggered, both flags are set. The active alarm flag clears at the end of the current ADC conversion unless the alarm condition persists, while the tripped flag remains set until ALARM\_REG is read.

The ALARM output flags update internally at the end of each conversion and can be read during any data frame initiated by pulling the CONVST/CS signal low.

The ALARM output flags can be accessed through the ALARM output pin, by reading the internal ALARM registers, or by appending the ALARM flags to the data output.

- A high level on the ALARM pin signals an over- or undervoltage condition on AVDD or an analog input channel. This pin can be used to interrupt the host input.

- The internal ALARM flag bits in the ALARM\_REG register update at the end of each conversion. After an ALARM

interrupt is received on the output pin, reading the internal alarm flag registers provides details on the conditions that

triggered the alarm.

- The alarm output flags can be optionally included in the data output bit stream, allowing the user to monitor alarm conditions alongside conversion data.

#### **Input Alarm**

The device includes both high and low alarms for the analog input. These alarms have independently programmable threshold values, which can be adjusted through the ALARM\_H\_TH\_REG and ALARM\_L\_TH\_REG registers. A common hysteresis setting is applied to both alarms to prevent rapid toggling due to minor signal fluctuations.

The device triggers an input high alarm when the digital output exceeds the [high alarm threshold (T)]. The alarm is cleared when the digital output falls below or equals the high alarm lower limit [high alarm (T) - H - 1].

Similarly, the input low alarm is activated when the digital output drops below the low alarm threshold [low alarm threshold (T)]. The alarm is reset when the digital output rises above or equals the low alarm higher limit [low alarm (T) + H + 1].

www.3peak.com 27 / 58 BA20240404A0

#### **AVDD Alarm**

The device includes high and low alarms for monitoring the analog voltage supply, AVDD. These alarms are triggered by fixed trip points, designed to alert when the AVDD supply voltage exceeds or falls below specified thresholds. The high alarm is triggered if AVDD exceeds a typical value of 5.3 V or 5.5 V. The low alarm is asserted if AVDD drops below 4.7 V. This feature is particularly useful for identifying issues such as glitches or brown-out conditions on the analog AVDD supply, which could lead to unexpected device behavior.

#### **Device Functional Modes**

#### **Device Modes**

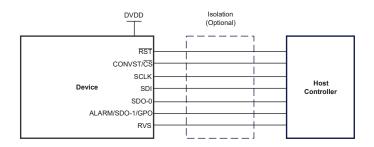

The device features a multiSPI digital interface that facilitates communication and data transfer between the device and the host controller. This interface supports multiple data transfer protocols, enabling the host to exchange both data and commands with the device. The host can transfer data into the device using one of the standard SPI modes. The device can be configured to output data in various ways, allowing flexibility in terms of throughput and latency requirements. The control of data output can either be managed by the host or the device, and the timing of data exchange can be either system synchronous or source synchronous.

The digital interface module of the device consists of several main components, which include shift registers (both input and output), configuration registers, and a protocol unit. These components work together to handle data transfer between the device and the host. In any given data frame, data are transferred both into and out of the device. As a result, the host perceives the device as a 32-bit input-output shift register, providing a continuous exchange of data. This structure ensures that the communication between the device and the host is efficient and flexible, allowing for seamless operation.

#### **Host-to-Device Connection Topologies**

The multiSPI interface allows for various configurations of data exchange between the host and the device. By configuring the appropriate device registers, the host can choose the optimal communication method to suit the specific system requirements, such as throughput, latency, and the number of connected devices. The flexibility of the multiSPI interface enables the user to adapt the data transfer protocol to different topologies, making it easier to integrate the device into various system architectures.

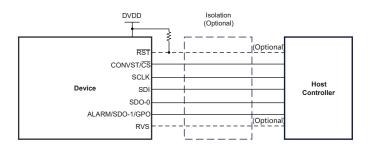

#### Single Device: All multiSPI Options

The figure below shows the pin connection between a host controller and a stand-alone device to exercise all options provided by the multiSPI interface.

www.3peak.com 28 / 58 BA20240404A0

Figure 22. All MultiSPI Protocols Pin Configuration

#### Single Device: Standard SPI Interface

The figure below shows the minimum pin interface for applications using a standard SPI protocol.

The CONVST/CS, SCLK, SDI, and SDO-0 pins constitute a standard SPI port of the host controller. The RST pin can be tied to DVDD. The RVS pin can be monitored for timing benefits. The ALARM/SDO-1/GPO pin may not have any external connection.

Figure 23. Standard SPI Protocol Pin Configuration

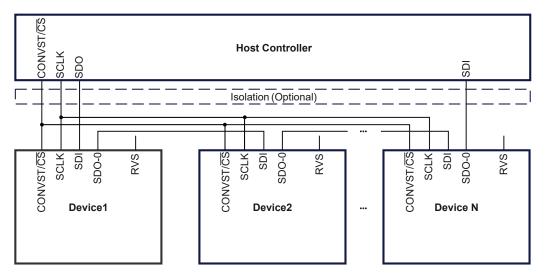

#### **Multiple Devices: Daisy-Chain Topology**

A typical connection diagram showing multiple devices in a daisy-chain topology is shown below.

Figure 24. Standard SPI Protocol Pin Configuration

www.3peak.com 29 / 58 BA20240404A0

In this configuration, multiple devices are chained together, allowing the host controller to communicate with each device sequentially. The CONVST/ $\overline{CS}$  and SCLK signals are shared across all devices, with the SDI input of the first device connected to the host's SDO-x output. The output from each device is then passed to the next device in the chain, with the final device's output connecting back to the host's SDI pin. This arrangement enables the host to send and receive data from multiple devices over a single SPI interface.

To set up multiple devices in a daisy-chain configuration, the host controller must ensure that each device is programmed with the same configuration register values. This ensures that the devices work together using a shared SDO-0 output. The data transfer between devices should occur with the external clock, and the devices should follow one of the legacy, SPI-compatible protocols for data reading and writing.