#### **Features**

- 32 Monotonic 12-Bit DACs

- Selectable Ranges: -10 to 0 V, -5 to 0 V, 0 to 5 V, and 0 to 10 V

- High Current Drive Capability: up to ±20 mA

- Auto-Range Detector

- Selectable Clamp Voltage

- 12-Bit SAR ADC

- 5 High Precision Inputs with 0-V to 5-V Range

- Programmable Out-of-Range Alarms

- Five General Purpose I/O Ports (GPIOs)

- Internal 2.5-V Reference

- · Internal Temperature Sensor

- –40°C to 125°C Operation

- Low-Power SPI-Compatible Serial Interface

- 4-Wire Mode or 3-Wire Mode, 1.8-V to 5.5-V

Operation

- Operating Temperature: −40°C to 125°C

- Available in TQFP7X7-48 package

#### **Applications**

- · Wireless Infrastructure

- Cellular Base Stations

- Microwave Backhaul

- · Optical Networks

- General Purpose Monitor and Control

- Data Acquisition Systems

#### **Description**

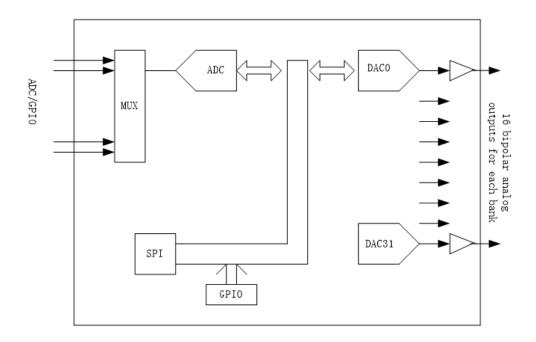

The TPAFE0532 is a highly integrated, low power consumption, analog monitor and control solution. It includes a 5-channel, 12-bit ADC, 32-channel 12-bit DACs with programmable output ranges, an internal reference, 5 GPIOs, and a local temperature sensor. The high integration significantly reduces component counts and simplifies the system design with small pace, low power, and high reliability.

The low power, very high integration, and wide operation temperature range of this device make it suitable for an all-in-one, low-cost, and bias-control circuit for power amplifiers found in multi-channel RF communication systems. The flexible DAC output ranges allow the device to be used as a biasing solution for a large variety of transistor technologies, such as LDMOS, GaN, or GaAs.

#### **Typical Application Circuit**

#### **Table of Contents**

| Features                                                   | 1  |

|------------------------------------------------------------|----|

| Applications                                               | 1  |

| Description                                                | 1  |

| Typical Application Circuit                                | 1  |

| Revision History                                           | 3  |

| Pin Configuration and Functions                            | 4  |

| Specifications                                             | 6  |

| Absolute Maximum Ratings                                   | 6  |

| ESD, Electrostatic Discharge Protection                    | 6  |

| Recommended Operating Conditions                           | 6  |

| Thermal Information                                        | 7  |

| Electrical Characteristics-DAC Specification               | 8  |

| Electrical Characteristics-ADC & TEMP Sensor Specification | 11 |

| Electrical Characteristics-General Specifications          | 12 |

| Timing Requirements                                        | 13 |

| Detailed Description                                       | 14 |

| Feature Description                                        | 14 |

| Application and Implementation                             | 44 |

| Application Note                                           | 44 |

| Layout                                                     | 45 |

| Layout Example                                             | 45 |

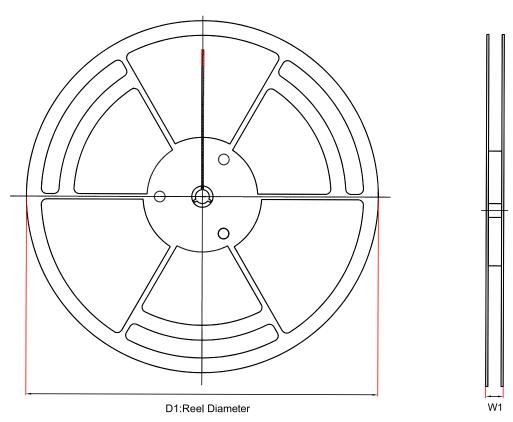

| Tape and Reel Information                                  | 46 |

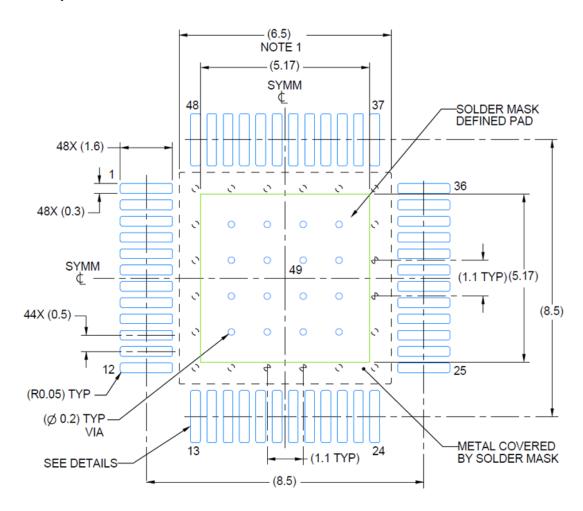

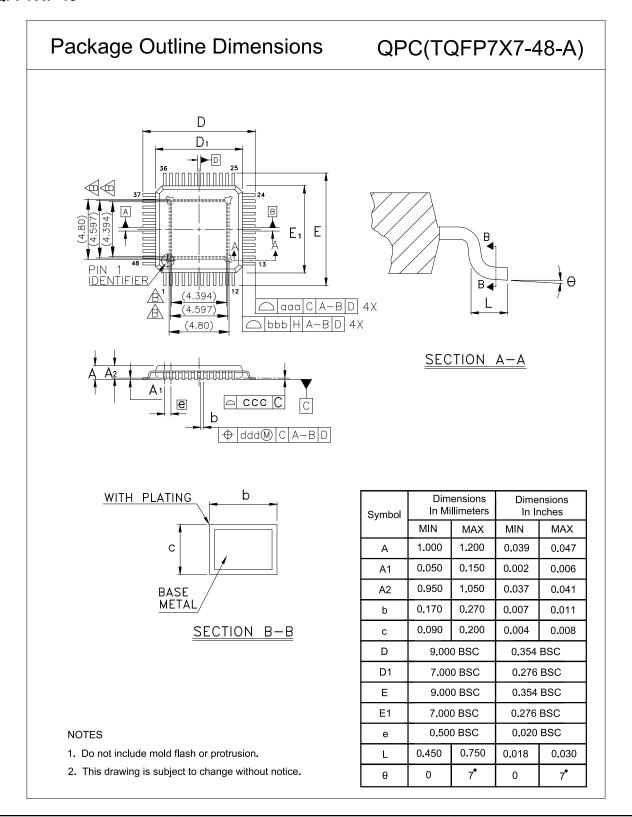

| Package Outline Dimensions                                 | 47 |

| TQFP7X7-48                                                 | 47 |

| Order Information                                          | 48 |

| IMPORTANT NOTICE AND DISCLAIMER                            | 49 |

# **Revision History**

| Date       | Revision | Notes                                                                                               |

|------------|----------|-----------------------------------------------------------------------------------------------------|

| 2019-12-10 | Rev.A.6  | Added the application note. Corrected the register names of the DACBxx in the register description. |

| 2020-05-28 | Rev.A.7  | Corrected the GPIO number in page 1.                                                                |

| 2021-02-18 | Rev.A.8  | Added Tape and Reel Order Information, and the 2 <sup>nd</sup> package POD.                         |

| 2022-05-30 | Rev.A.9  | Updated the example board layout.                                                                   |

| 2023-05-21 | Rev.A.10 | Updated Tape and Reel Information.                                                                  |

| 2024-08-13 | Rev.A.11 | Updated to a new datasheet format.  Added a note for Recommended Operating Conditions.              |

| 2024-12-12 | Rev.A.12 | Updated the POD of TQFP7x7-48. Added the MSL in the Order Information.                              |

www.3peak.com 3 / 50 BA20241205A12

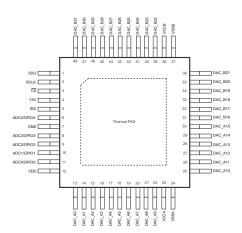

# **Pin Configuration and Functions**

TPAFE0532 TQFP7X7-48 Top View

**Table 1. Pin Functions**

| Pin No.        | Name                                | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|-------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | SDO                                 | 0   | The SPI data output. The data is clocked out of the input shift register on each falling edge of SCLK.                                                                                                                                                                                                                                                                                                                     |

| 2              | SCLK                                | I   | The SPI clock.                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3              | /CS                                 | I   | The active low serial data enable.                                                                                                                                                                                                                                                                                                                                                                                         |

| 4              | VIO                                 | PWR | The IO supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5              | SDI                                 | I   | The SPI data input.                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6<br>8~11      | ADC4/<br>GPIO4 to<br>ADC0/<br>GPIO0 | I/O | The analog ADC inputs. These pins can be set to operate as GPIOs. The GPIO functions are as below:  GPIO4: /DAV, the active low ADC data available indicator.  GPIO3: /ADCTRIG, the active low external ADC conversion trigger.  GPIO2: /ALARMOUT, the open drain global alarm output.  GPIO1: /CLEARB, the active low DAC group B clear control signal.  GPIO0: /CLEARA, the active low DAC group A clear control signal. |

| 7              | GND                                 | GND | The ground supply.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 12             | VDD                                 | PWR | The analog supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                 |

| 13~22<br>25~30 | DAC_A0 to<br>DAC_A15                | 0   | The DAC group A. These 16 DAC outputs share the same range and clamp levels.                                                                                                                                                                                                                                                                                                                                               |

| 23             | VCCA                                | PWR | The positive analog power supply for DAC group A.                                                                                                                                                                                                                                                                                                                                                                          |

| 24             | VSSA                                | PWR | The negative analog power supply for DAC group A.                                                                                                                                                                                                                                                                                                                                                                          |

| 31~36<br>39~48 | DAC_B16<br>to<br>DAC_B31            | 0   | The DAC group B. These 16 DAC outputs share the same range and clamp levels.                                                                                                                                                                                                                                                                                                                                               |

| 37             | VSSB                                | PWR | The negative analog power supply for DAC group A.                                                                                                                                                                                                                                                                                                                                                                          |

www.3peak.com 4 / 50 BA20241205A12

| Pin No. | Name    | I/O | Description                                                              |

|---------|---------|-----|--------------------------------------------------------------------------|

| 38      | VCCB    | PWR | The positive analog power supply for DAC group A.                        |

|         | Thermal |     | The thermal pad should be connected to PCB ground plane for good thermal |

|         | PAD     |     | performance.                                                             |

www.3peak.com 5 / 50 BA20241205A12

#### **Specifications**

#### **Absolute Maximum Ratings**

|                  | Parameter                            | Min                    | Max                    | Unit |

|------------------|--------------------------------------|------------------------|------------------------|------|

|                  | V <sub>DD</sub> to GND               | -0.3                   | 6                      | V    |

|                  | V <sub>IO</sub> to GND               | -0.3                   | 6                      | V    |

| Supply           | V <sub>CC (A, B)</sub> to GND        | -0.3                   | 12                     | V    |

| Voltage          | V <sub>SS (A, B)</sub> to GND        | -12                    | 0.3                    | V    |

|                  | V <sub>CCA</sub> to V <sub>SSA</sub> | -0.3                   | 12                     | V    |

|                  | V <sub>CCB</sub> to V <sub>SSB</sub> | -0.3                   | 12                     | V    |

|                  | DAC_A [0-15] Outputs to GND          | V <sub>SSA</sub> - 0.3 | V <sub>CCA</sub> + 0.3 | V    |

| Pin              | DAC_B [16-31] Ouputs to GND          | V <sub>SSB</sub> - 0.3 | V <sub>CCB</sub> + 0.3 | V    |

| Voltage          | FlexIO Pins to GND                   | -0.3                   | V <sub>DD</sub> + 0.3  | V    |

|                  | SPI Pins to GND                      | -0.3                   | V <sub>IO</sub> + 0.3  | V    |

|                  | ADC Analog Input Current             | -10                    | 10                     | mA   |

| TJ               | Maximum Junction Temperature         | -40                    | 150                    | °C   |

| T <sub>A</sub>   | Operating Temperature Range          | -40                    | 125                    | °C   |

| T <sub>STG</sub> | Storage Temperature Range            | -65                    | 150                    | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

#### **ESD, Electrostatic Discharge Protection**

| Symbol | Parameter                | Condition                  | Minimum Level | Unit |

|--------|--------------------------|----------------------------|---------------|------|

| НВМ    | Human Body Model ESD     | ANSI/ESDA/JEDEC JS-001 (1) | ±2000         | V    |

| CDM    | Charged Device Model ESD | ANSI/ESDA/JEDEC JS-002 (2) | ±1000         | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### **Recommended Operating Conditions**

|                | Parameter              | Min  | Тур | Max  | Unit |

|----------------|------------------------|------|-----|------|------|

| Supply Voltage | $V_{DD}$               | 4.5  |     | 5.5  | V    |

|                | V <sub>IO</sub>        | 1.65 |     | 5.5  | V    |

|                | V <sub>CC</sub> (A, B) | 4.5  |     | 11   | V    |

|                | Vss (A. B)             | -11  |     | -4.5 | V    |

www.3peak.com 6 / 50 BA20241205A12

<sup>(2)</sup> The input and output voltage ratings may be exceeded if the input and output diode current ratings are observed.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

|                             | Parameter                           | Min | Тур | Max | Unit |

|-----------------------------|-------------------------------------|-----|-----|-----|------|

|                             | V <sub>CCA</sub> - V <sub>SSA</sub> | 4.5 |     | 11  | V    |

|                             | V <sub>CCB</sub> - V <sub>SSB</sub> | 4.5 |     | 11  | V    |

| Specifies Temperature Range |                                     | -40 |     | 125 | °C   |

| Operating Temperature Range |                                     | -40 |     | 125 | °C   |

<sup>(1)</sup> For positive output,  $V_{ss[a]}$  or  $V_{ss[b]}$  should be connected to 0 V. For negative output,  $V_{cc[a]}$  or  $V_{cc[b]}$  should be connected to 0 V.

#### **Thermal Information**

| Package Type  | θ <sub>JA</sub> | θЈВ | θυς                      | Unit |

|---------------|-----------------|-----|--------------------------|------|

| TQFP7×7-EP48L | 22.1            | 6.6 | 12.7 (top), 0.7 (bottom) | °C/W |

www.3peak.com 7 / 50 BA20241205A12

#### **Electrical Characteristics-DAC Specification**

All test conditions:  $V_{DD}$  = 4.5 to 5.5 V,  $V_{IO}$  = 1.65 V to 3.6 V;  $V_{CC}$  = 4.5 V to 11 V,  $V_{SS}$  = GND for positive range;  $V_{CC}$  = GND,  $V_{SS}$  = -11 to -4.5 V for negative output range; over specified temperature range, unless otherwise noted.

| Parameter                          | Conditions                                                           | Min | Тур   | Max      | Unit   |

|------------------------------------|----------------------------------------------------------------------|-----|-------|----------|--------|

| DAC DC Specifications              |                                                                      |     |       | <u> </u> | I.     |

| Resolution                         |                                                                      | 12  |       |          |        |

|                                    |                                                                      | -10 |       | 0        | V      |

|                                    | Power up or Reset Through Auto-                                      | -5  |       | 0        | V      |

| Full-Scale Output Voltage Range    | Range Detection                                                      | 0   |       | 5        | V      |

|                                    |                                                                      | 0   |       | 10       | V      |

| INL                                |                                                                      |     |       | ±3       | LSB    |

| DNL                                |                                                                      |     |       | ±1       | LSB    |

| Positive Output Range              |                                                                      |     |       |          |        |

| TUE                                | End point fit between codes 16 to 4031.  DAC outputs unloaded.       |     | ±0.1  | ±0.5     | %FSR   |

| Total Error Temperature Drift      | After one point calibration at 25°C. Vout: 2.5 V (10 V or 5 V range) |     | ±0.03 |          | %FSR   |

| Offset Error                       | Full temp? End point fit towards value at code 000h                  |     | ±2    | ±15      | mV     |

| Offset Error Temperature Drift     |                                                                      |     | ±2    |          | ppm/°C |

| Gain Error                         | Full temp                                                            |     | ±0.01 | ±0.45    | %FSR   |

| Gain Error Temperature Drift       |                                                                      |     | ±20   |          | ppm/°C |

| Zero-Scale Error                   | Code = 000h<br>Full temp                                             |     | 2     | 15       | mV     |

| Zero-Scale Error Temperature Drift |                                                                      |     | ±2    |          | ppm/°C |

| Full-Scale Error                   | Code = FFFh                                                          |     | ±0.01 | ±0.45    | %FSR   |

| Full-Scale Error Temperature Drift |                                                                      |     | ±20   |          | ppm/°C |

| Negative Output Ranges             |                                                                      |     |       |          |        |

| TUE                                |                                                                      |     | ±0.1  | ±0.5     | %FSR   |

| Total Error Temperature Drift      |                                                                      |     | ±0.03 |          | %FSR   |

| Offset Error                       | End point fit towards value at code FFFh                             |     | ±2    | ±15      | mV     |

| Offset Error Temperature Drift     |                                                                      |     | ±2    |          | ppm/°C |

| Gain Error                         |                                                                      |     | ±0.01 | ±0.45    | %FSR   |

| Gain Error Temperature Drift       |                                                                      |     | ±20   |          | ppm/°C |

| Zero-Scale Error                   | Code = FFFh                                                          |     | -2    | 25       | mV     |

| Zero-Scale Error Temperature Drift |                                                                      |     | ±2    |          | ppm/°C |

| Full-Scale Error                   | Code = 000h                                                          |     | ±0.01 | ±0.45    | %FSR   |

www.3peak.com 8 / 50 BA20241205A12

| Parameter                          | Conditions                                                                                                | Min | Тур  | Max | Unit   |

|------------------------------------|-----------------------------------------------------------------------------------------------------------|-----|------|-----|--------|

| Full-Scale Error Temperature Drift |                                                                                                           |     | ±20  |     | ppm/°C |

| DAC Output Buffer Specifications   |                                                                                                           |     |      |     |        |

| Load Current                       | Source with 1-V headroom from V <sub>CC</sub> With 25-mV variation                                        |     | 20   |     | mA     |

| Load Garrent                       | Sink with 1-V headroom from V <sub>SS</sub> with 25-mV variation                                          |     | 20   |     | mA     |

| Short Circuit Current              | Low current mode                                                                                          |     | ±10  |     | mA     |

| Short Gireat Garrent               | Normal mode (default)                                                                                     |     | ±45  |     | mA     |

| Capacitive Load Stability          | R <sub>L</sub> = ∞                                                                                        |     | 200  |     | pF     |

| DC Output Impedance                | DAC code at mid-scale                                                                                     |     | 1    |     | Ω      |

| Output Voltage Setting Time        | Zero-scale to quarter full-scale step to within 2.5 mV $R_L = 2 \text{ k}\Omega$ , $C_I = 200 \text{ pF}$ |     | 7    |     | μs     |

|                                    | 1/4 to 3/4 scale settling to $\pm 0.5$ LSB. R <sub>L</sub> = 2 k $\Omega$ , C <sub>I</sub> = 200 pF       |     | 11   |     | μs     |

| Slew Rate                          | Transition: 1/4 to 3/4 scale, 10% to 90%                                                                  |     | 0.5  |     | V/µs   |

| Output Noise                       | 0.1 Hz to 10 Hz, DAC code at mid-scale                                                                    |     | 250  |     | μVpp   |

| Output Noise Density               | 1 kHz, DAC code at mid-scale                                                                              |     | 1000 |     | nV/√Hz |

| AC PSRR                            | DAC code at mid-scale. Frequency = 60 Hz, amplitude = 200 mVpp superimposed on V <sub>DD</sub>            |     | 60   |     | dB     |

|                                    | DAC code at mid-scale.  Frequency = 60 Hz, amplitude = 200  mVpp superimposed on V <sub>CC</sub>          |     | 85   |     | dB     |

|                                    | DAC code at mid-scale.  Frequency = 60 Hz, amplitude = 200  mVpp superimposed on Vss                      |     | 85   |     | dB     |

| DC PSRR                            | DAC code at mid-scale.<br>±5% variation on all supplies.                                                  |     | 0.15 |     | mV/V   |

| Code Change Glitch Impulse         | 1-LSB change around major carrier                                                                         |     | 6    |     | nV-s   |

| Glitch Impulse Amplitude           | 1-LSB change around major carrier                                                                         |     | 4    |     | mV     |

| Power-on Overshoot                 | $V_{SS}$ = GND, $V_{CC}$ = 0 to +11 V,<br>2-ms ramp<br>R_series = 5 ohm, C = 1 $\mu$ F                    |     | 50   |     | mV     |

|                                    | V <sub>SS</sub> = GND, V <sub>CC</sub> = 0 to −11 V,<br>2-ms ramp<br>R_series = 5 ohm, C = 1 μF           |     | 50   |     | mV     |

| Turn-on Overshoot                  | 0~1/2 FS<br>R_series = 5 ohm, C = 1 μF                                                                    |     |      |     | mV     |

| Channel to Channel DC Crosstalk    | Measured channel at midscale.                                                                             |     | 1    |     | mV     |

www.3peak.com 9 / 50 BA20241205A12

| Parameter                   | Conditions                                                               | Min | Тур | Max | Unit |

|-----------------------------|--------------------------------------------------------------------------|-----|-----|-----|------|

|                             | Full scale output change on all other                                    |     |     |     |      |

|                             | channels.                                                                |     |     |     |      |

| Clamp Output Specifications |                                                                          |     |     |     |      |

| Load Current                | DAC output buffers inactive. Sink with 2-V headroom from V <sub>SS</sub> | 8   |     |     | mA   |

www.3peak.com 10 / 50 BA20241205A12

#### **Electrical Characteristics-ADC & TEMP Sensor Specification**

All test conditions:  $V_{DD} = 4.5$  to 5.5 V,  $V_{IO} = 1.65$  V to 3.6 V;  $V_{CC} = 4.5$  V to 11 V,  $V_{SS} = GND$  for positive range;  $V_{CC} = GND$ ,  $V_{SS} = -11$  to -4.5 V for negative output range; over specified temperature range, unless otherwise noted.

| Parameter                      | Conditions                 | Min | Тур    | Max                  | Unit   |

|--------------------------------|----------------------------|-----|--------|----------------------|--------|

| ADC DC Specifications          |                            |     |        |                      |        |

| Resolution                     |                            | 12  |        |                      |        |

| Full Cools lawy & Downs        |                            | 0   |        | 2 × V <sub>REF</sub> | V      |

| Full-Scale Input Range         |                            | 0   |        | V <sub>REF</sub>     | V      |

| INL                            |                            |     |        | ±2                   | LSB    |

| DNL                            |                            |     |        | ±1                   | LSB    |

| Offset Error                   | After calibration          |     |        | ±5                   | LSB    |

| Offset Error Match             |                            |     | ±0.4   |                      | LSB    |

| Offset Error Temperature Drift |                            |     | 4      |                      | ppm/°C |

| Gain Error                     |                            |     | ±0.01  | ±0.5                 | %FSR   |

| Gain Error Match               |                            |     | ±0.4   |                      | LSB    |

| Gain Error Temperature Drift   |                            |     | 4      |                      | ppm/°C |

| Input Capacitance              |                            |     | 20     |                      | pF     |

| Input Bias Current             | Unselected ADC input       |     |        | ±10                  | μA     |

| Conversion Time                |                            |     | 1.875  |                      | μS     |

| Acquisition Time               | 500-kSPS conversion rate   |     |        |                      | μS     |

| Conversion Rate                |                            |     | 430    |                      | kSPS   |

| Throughput Rate                | SCLK = 20 MHz              |     |        | 250                  | kSPS   |

| Throughput Nate                | SPI Update data rate       |     |        | 230                  | KOFO   |

| Temperature Sensor Range       |                            |     |        |                      |        |

| Operating Range                |                            | -40 |        | 150                  | °C     |

| Accuracy                       | T <sub>J</sub> = -40~125°C |     | ±2.5   |                      | °C     |

| Resolution                     | LSB size                   |     | 0.0625 |                      | °C     |

| Update Time                    | T <sub>J</sub> = -40~125°C |     | 31.25  |                      | ms     |

www.3peak.com 11 / 50 BA20241205A12

#### **Electrical Characteristics-General Specifications**

All test conditions:  $V_{DD}$  = 4.5 to 5.5 V,  $V_{IO}$  = 1.65 V to 5.5 V;  $V_{CC}$  = 4.5 V to 11 V,  $V_{SS}$  = GND for positive range;  $V_{CC}$  = GND,  $V_{SS}$  = -11 to -4.5 V for negative output range; over specified temperature range, unless otherwise noted.

| Parameter                       | Conditions                                           | Min                   | Тур   | Max                   | Unit |

|---------------------------------|------------------------------------------------------|-----------------------|-------|-----------------------|------|

| GPIO Specifications             |                                                      |                       |       |                       |      |

| VIH LOWVIO                      |                                                      | 0.7 × V <sub>IO</sub> |       |                       | V    |

| V <sub>IL LowVIO</sub>          |                                                      |                       |       | 0.3 × V <sub>IO</sub> | V    |

| Serial Interface Specifications | s                                                    |                       |       |                       |      |

| VIH LowVIO                      |                                                      | 0.7 × V <sub>IO</sub> |       |                       | V    |

| V <sub>IL LowVIO</sub>          |                                                      |                       |       | 0.3 × V <sub>IO</sub> | V    |

| Input Current                   |                                                      |                       | 2     |                       | μA   |

| Input Pin Capacitance           |                                                      |                       | 2     |                       | pF   |

| V <sub>OH</sub>                 | I <sub>source</sub> = 0.2 mA                         | V <sub>IO</sub> - 0.2 |       |                       | V    |

| VoL                             | I <sub>sink</sub> = 0.2 mA                           |                       |       | 0.2                   | V    |

| Output Pin Capacitance          |                                                      |                       | 2     |                       | pF   |

| Pull up Resistor nCS            |                                                      |                       | 1     |                       | ΜΩ   |

| Pull up Resistor SCLK           |                                                      |                       | 1     |                       | МΩ   |

| Auto-Range Threshold Detec      | tor                                                  |                       |       |                       |      |

| V <sub>SSTH</sub>               | Negative voltage range                               |                       | -3.75 |                       |      |

| V <sub>ССТН</sub>               | Positive voltage range                               |                       | 3     |                       |      |

| Power Requirement               |                                                      |                       |       |                       |      |

| I <sub>VDD</sub>                |                                                      |                       | 20    |                       | mA   |

| I <sub>VCC</sub> [A,B]          | All DAC at midscale code.  ADC in fastest auto mode. |                       | 10    |                       | mA   |

| Ivss [A,B]                      | Temperature sensor enabled.                          |                       | 10    |                       | mA   |

| Ivio                            |                                                      |                       | 5     |                       | μΑ   |

| I <sub>VDD</sub>                |                                                      |                       | 3     |                       | mA   |

| Ivcc [A,B]                      | Davier davis made                                    |                       | 0.5   |                       | mA   |

| I <sub>VSS</sub> [A,B]          | Power-down mode                                      |                       | 0.5   |                       | mA   |

| Ivio                            |                                                      |                       | 5     |                       | μΑ   |

www.3peak.com 12 / 50 BA20241205A12

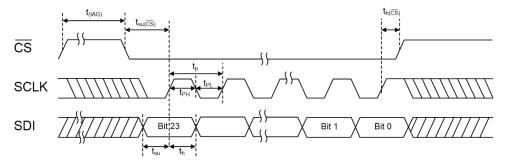

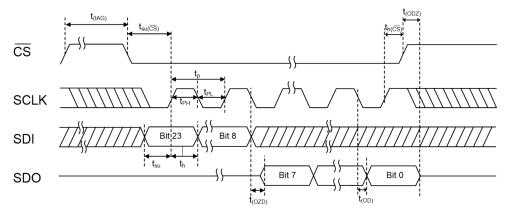

#### **Timing Requirements**

All test conditions:  $V_{DD}$  = 4.5 to 5.5 V,  $V_{IO}$  = 1.8 V to 3.6 V;  $V_{CC}$  = 4.5 V to 11 V,  $V_{SS}$  = GND for positive range;  $V_{CC}$  = GND,  $V_{SS}$  = -11 to -4.5 V for negative output range; over specified temperature range, unless otherwise noted.

| Parameter                                     | Conditions | Min  | Тур | Max | Unit |

|-----------------------------------------------|------------|------|-----|-----|------|

| Serial Interface                              |            |      |     |     |      |

| f (SCLK)                                      |            |      |     | 20  | MHz  |

| t <sub>PH</sub> SCLK Pulse Width High         |            | 24.5 |     |     | nS   |

| t <sub>PL</sub> SCLK Pulse Width Low          |            | 24.5 |     |     | nS   |

| t <sub>su</sub> SDI Setup <sup>(1)</sup>      |            | 20   |     |     | nS   |

| t <sub>h</sub> SDI Hold <sup>(1)</sup>        |            | 20   |     |     | nS   |

| t <sub>(ODZ)</sub> SDO Driven to Tri-State    |            | 0    |     | 25  | nS   |

| t <sub>(OZD)</sub> SDO Tri-State to Driven    |            | 1.5  |     | 30  | nS   |

| t <sub>(OD)</sub> SDO Output Delay            |            | 0    |     | 25  | nS   |

| t <sub>su (cs)</sub> /CS Setup <sup>(1)</sup> |            | 20   |     |     | nS   |

| t <sub>h (/cs)</sub> /CS Hold <sup>(1)</sup>  |            | 20   |     |     | nS   |

| t <sub>(IAG)</sub> /CS High Time              |            | 20   |     |     | nS   |

Figure 1. Serial Interface Write Timing Diagram

Figure 2. Serial Interface Read Timing Diagram

www.3peak.com 13 / 50 BA20241205A12

# **Detailed Description**

#### **Feature Description**

Register Map

| Address1    | Type | Default | Register Name                |

|-------------|------|---------|------------------------------|

| 0×00        | R/W  | 30      | Interface Configuration 0    |

| 0×01        | R/W  | 0       | Interface Configuration 1    |

| 0×02        | R/W  | 3       | Device Configuration         |

| 0×03        | R    | 8       | Chip Type                    |

| 0×04        | R    | 32      | Chip ID (Low Byte)           |

| 0×05        | R    | 5       | Chip ID (High Byte)          |

| 0×06        | R    | 3       | Chip Version                 |

| 0×07-0×0B   | _    | _       | Reserved                     |

| 0×0C        | R    | 32      | Manufacturer ID (Low Byte)   |

| 0×0D        | R    | 1       | Manufacturer ID (High Byte)  |

| 0×0E        | _    | _       | Reserved                     |

| 0×0F        | R/W  | 0       | Register Update              |

| 0×21E       | R    | 0       | Temperature Data (Low Byte)  |

| 0×21F       | R    | 40      | Temperature Data (High Byte) |

| 0×220       | R    | 0       | ADC0-Data (Low Byte)         |

| 0×221       | R    | 0       | ADC0-Data (High Byte)        |

| 0×222       | R    | 0       | ADC1-Data (Low Byte)         |

| 0×223       | R    | 0       | ADC1-Data (High Byte)        |

| 0×224       | R    | 0       | ADC2-Data (Low Byte)         |

| 0×225       | R    | 0       | ADC2-Data (High Byte)        |

| 0×226       | R    | 0       | ADC3-Data (Low Byte)         |

| 0×227       | R    | 0       | ADC3-Data (High Byte)        |

| 0×228       | R    | 0       | ADC4-Data (Low Byte)         |

| 0×229       | R    | 0       | ADC4-Data (High Byte)        |

| 0×22A       | R    | 0       | ADC5-Data (Low Byte)         |

| 0×22B       | R    | 0       | ADC5-Data (High Byte)        |

| 0×22C-0×22D | _    | _       | Reserve                      |

| 0×22E-0×22F | _    | _       | Reserve                      |

| 0×230       | R/W  | 0       | DACA0-Data (Low Byte)        |

| 0×231       | R/W  | 0       | DACA0-Data (High Byte)       |

| 0×232       | R/W  | 0       | DACA1-Data (Low Byte)        |

| 0×233       | R/W  | 0       | DACA1-Data (High Byte)       |

| 0×234       | R/W  | 0       | DACA2-Data (Low Byte)        |

www.3peak.com 14 / 50 BA20241205A12

| 0×235 | R/W | 0 | DACA2-Data (High Byte)  |

|-------|-----|---|-------------------------|

| 0×236 | R/W | 0 | DACA3-Data (Low Byte)   |

| 0×237 | R/W | 0 | DACA3-Data (High Byte)  |

| 0×238 | R/W | 0 | DACA4-Data (Low Byte)   |

| 0×239 | R/W | 0 | DACA4-Data (High Byte)  |

| 0×23A | R/W | 0 | DACA5-Data (Low Byte)   |

| 0×23B | R/W | 0 | DACA5-Data (High Byte)  |

| 0×23C | R/W | 0 | DACA6-Data (Low Byte)   |

| 0×23D | R/W | 0 | DACA6-Data (High Byte)  |

| 0×23E | R/W | 0 | DACA7-Data (Low Byte)   |

| 0×23F | R/W | 0 | DACA7-Data (High Byte)  |

| 0×240 | R/W | 0 | DACA8-Data (Low Byte)   |

| 0×241 | R/W | 0 | DACA8-Data (High Byte)  |

| 0×242 | R/W | 0 | DACA9-Data (Low Byte)   |

| 0×243 | R/W | 0 | DACA9-Data (High Byte)  |

| 0×244 | R/W | 0 | DACA10-Data (Low Byte)  |

| 0×245 | R/W | 0 | DACA10-Data (High Byte) |

| 0×246 | R/W | 0 | DACA11-Data (Low Byte)  |

| 0×247 | R/W | 0 | DACA11-Data (High Byte) |

| 0×248 | R/W | 0 | DACA12-Data (Low Byte)  |

| 0×249 | R/W | 0 | DACA12-Data (High Byte) |

| 0×24A | R/W | 0 | DACA13-Data (Low Byte)  |

| 0×24B | R/W | 0 | DACA13-Data (High Byte) |

| 0×24C | R/W | 0 | DACA14-Data (Low Byte)  |

| 0×24D | R/W | 0 | DACA14-Data (High Byte) |

| 0×24E | R/W | 0 | DACA15-Data (Low Byte)  |

| 0×24F | R/W | 0 | DACA15-Data (High Byte) |

| 0×250 | R/W | 0 | DACB16-Data (Low Byte)  |

| 0×251 | R/W | 0 | DACB16-Data (High Byte) |

| 0×252 | R/W | 0 | DACB17-Data (Low Byte)  |

| 0×253 | R/W | 0 | DACB17-Data (High Byte) |

| 0×254 | R/W | 0 | DACB18-Data (Low Byte)  |

| 0×255 | R/W | 0 | DACB18-Data (High Byte) |

| 0×256 | R/W | 0 | DACB19-Data (Low Byte)  |

| 0×257 | R/W | 0 | DACB19-Data (High Byte) |

| 0×258 | R/W | 0 | DACB20-Data (Low Byte)  |

| 0×259 | R/W | 0 | DACB20-Data (High Byte) |

| 0×25A | R/W | 0 | DACB21-Data (Low Byte)  |

www.3peak.com 15 / 50 BA20241205A12

| 0×25B | R/W | 0  | DACB21-Data (High Byte)   |

|-------|-----|----|---------------------------|

| 0×25C | R/W | 0  | DACB22-Data (Low Byte)    |

| 0×25D | R/W | 0  | DACB22-Data (High Byte)   |

| 0×25E | R/W | 0  | DACB23-Data (Low Byte)    |

| 0×25F | R/W | 0  | DACB23-Data (High Byte)   |

| 0×260 | R/W | 0  | DACB24-Data (Low Byte)    |

| 0×261 | R/W | 0  | DACB24-Data (High Byte)   |

| 0×262 | R/W | 0  | DACB25-Data (Low Byte)    |

| 0×263 | R/W | 0  | DACB25-Data (High Byte)   |

| 0×264 | R/W | 0  | DACB26-Data (Low Byte)    |

| 0×265 | R/W | 0  | DACB26-Data (High Byte)   |

| 0×266 | R/W | 0  | DACB27-Data (Low Byte)    |

| 0×267 | R/W | 0  | DACB27-Data (High Byte)   |

| 0×268 | R/W | 0  | DACB28-Data (Low Byte)    |

| 0×269 | R/W | 0  | DACB28-Data (High Byte)   |

| 0×26A | R/W | 0  | DACB29-Data (Low Byte)    |

| 0×26B | R/W | 0  | DACB29-Data (High Byte)   |

| 0×26C | R/W | 0  | DACB30-Data (Low Byte)    |

| 0×26D | R/W | 0  | DACB30-Data (High Byte)   |

| 0×26E | R/W | 0  | DACB31-Data (Low Byte)    |

| 0×26F | R/W | 0  | DACB31-Data (High Byte)   |

| 0×310 | R/W | 0  | ADC Configuration         |

| 0×311 | R/W | 60 | False Alarm Configuration |

| 0×312 | R/W | 0  | GPIO Configuration        |

| 0×313 | R/W | 3F | ADC MUX Configuration     |

| 0×314 | R/W | 0  | Hardware Reset            |

| 0×315 | R/W | 0  | DAC Range                 |

| 0×316 | R/W | 0  | DAC Clear Enable 0        |

| 0×317 | R/W | 0  | DAC Clear Enable 1        |

| 0×318 | R/W | 0  | DAC Clear Enable 2        |

| 0×319 | R/W | 0  | DAC Clear Enable 3        |

| 0×31A | R/W | 0  | DAC Clear Source 0        |

| 0×31B | R/W | 0  | DAC Clear Source 1        |

| 0×31C | R/W | 0  | ALARMOUT Source 0         |

| 0×31D | R/W | 0  | ALARMOUT Source1          |

| 0×370 | R   | 0  | Alarm Status 0            |

| 0×371 | R   | 0  | Alarm Status 1            |

| 0×372 | R   | 8  | General Status            |

www.3peak.com 16 / 50 BA20241205A12

| 0×373       | R   | 0  | DACA7~DACA0 Output Short           |

|-------------|-----|----|------------------------------------|

| 0×374       | R   | 0  | DACA15~DACA8 Output Short          |

| 0×375       | R   | 0  | DACB23~DACB16 Output Short         |

| 0×376       | R   | 0  | DACB31~DACB24 Output Short         |

| 0×377-0×379 | _   | _  | Reserved                           |

| 0×37A       | R/W | 3F | GPIO                               |

| 0×37B       | R/W | 0  | Auxillary                          |

| 0×37C-0×37D | _   | 0  | Reserved                           |

| 0×37E       | W   |    | DAC broadcast Data (Low Byte)      |

| 0×37F       | W   | _  | DAC broadcast Data (High Byte)     |

| 0×380       | R/W | FF | LT-Upper-Thresh (Low Byte)         |

| 0×381       | R/W | 0  | LT-Lower-Thresh (Low Byte)         |

| 0×382       | R/W | FF | LT-Therm-Thres (Thermal Thut Down) |

| 0×383       | _   | _  | Reserved                           |

| 0×384       | R/W | FF | ADC0-Upper-Thresh (Low Byte)       |

| 0×385       | R/W | 0F | ADC0-Upper-Thresh (High Byte)      |

| 0×386       | R/W | 0  | ADC0-Lower-Thresh (Low Byte)       |

| 0×387       | R/W | 0  | ADC0-Lower-Thresh (High Byte)      |

| 0×388       | R/W | FF | ADC1-Upper-Thresh (Low Byte)       |

| 0×389       | R/W | 0F | ADC1-Upper-Thresh (High Byte)      |

| 0×38A       | R/W | 0  | ADC1-Lower-Thresh (Low Byte)       |

| 0×38B       | R/W | 0  | ADC1-Lower-Thresh (High Byte)      |

| 0×38C       | R/W | FF | ADC2-Upper-Thresh (Low Byte)       |

| 0×38D       | R/W | 0F | ADC2-Upper-Thresh (High Byte)      |

| 0×38E       | R/W | 0  | ADC2-Lower-Thresh (Low Byte)       |

| 0×38F       | R/W | 0  | ADC2-Lower-Thresh (High Byte)      |

| 0×390       | R/W | FF | ADC3-Upper-Thresh (Low Byte)       |

| 0×391       | R/W | 0F | ADC3-Upper-Thresh (High Byte)      |

| 0×392       | R/W | 0  | ADC3-Lower-Thresh (Low Byte)       |

| 0×393       | R/W | 0  | ADC3-Lower-Thresh (High Byte)      |

| 0×394       | R/W | FF | ADC4-Upper-Thresh (Low Byte)       |

| 0×395       | R/W | 0F | ADC4-Upper-Thresh (High Byte)      |

| 0×396       | R/W | 0  | ADC4-Lower-Thresh (Low Byte)       |

| 0×397       | R/W | 0  | ADC4-Lower-Thresh (High Byte)      |

| 0×398       | R/W | FF | ADC5-Upper-Thresh (Low Byte)       |

| 0×399       | R/W | 0F | ADC5-Upper-Thresh (High Byte)      |

| 0×39A       | R/W | 0  | ADC5-Lower-Thresh (Low Byte)       |

| 0×39B       | R/W | 0  | ADC5-Lower-Thresh (High Byte)      |

www.3peak.com 17 / 50 BA20241205A12

| 0×39C-0×39F   | _   | _  | Reserved        |

|---------------|-----|----|-----------------|

| 0×3A0         | R/W | Α  | LT-Hysteresis   |

| 0×3A1         | R/W | 8  | ADC0-Hysteresis |

| 0×3A2         | R/W | 8  | ADC1-Hysteresis |

| 0×3A3         | R/W | 8  | ADC2-Hysteresis |

| 0×3A4         | R/W | 8  | ADC3-Hysteresis |

| 0×3A5         | R/W | 8  | ADC4-Hysteresis |

| 0×3A6         | R/W | 8  | ADC5-Hysteresis |

| 0×3A7 - 0×AD  | _   | _  | Reserved        |

| 0×3AE         | R/W | 0  | DAC Clear 0     |

| 0×3AF         | R/W | 0  | DAC Clear 1     |

| 0×3B0         | R/W | 0  | DAC Clear 2     |

| 0×3B1         | R/W | 0  | DAC Clear 3     |

| 0×3B2         | R/W | 0  | Power-Down 0    |

| 0×3B3         | R/W | 0  | Power-Down 1    |

| 0×3B4         | R/W | 0  | Power-Down 2    |

| 0×3B5         | R/W | 0  | Power-Down3     |

| 0×3B6         | R/W | 0  | Power-Down4     |

| 0×3B7 - 0×xBF | _   | _  | Reserved        |

| 0×3C0         | R/W | 77 | ADC Trigger     |

www.3peak.com 18 / 50 BA20241205A12

#### **Register Identification**

Interface configuration: Address 0×00-0×02

Register name: interface configuration 0-address 0×00

| Register Name      | Address                 | Bit       | Name        | Function                                                                           |                          |

|--------------------|-------------------------|-----------|-------------|------------------------------------------------------------------------------------|--------------------------|

|                    |                         |           |             | Soft reset (self clear)                                                            |                          |

|                    |                         | 7         | SOFT RESET  | 0: no action                                                                       |                          |

|                    | Interface Config 0 0×30 | ,         | GOI I_KLOLI | 1: reset-resets everything except address 0×00, 0×01                               |                          |

|                    |                         |           | 6           | Reserved                                                                           | Reserved for factory use |

|                    |                         | 0×30<br>5 | ADDR-ASCEND | Address ascend                                                                     |                          |

| Interface Config 0 |                         |           |             | 0: descend-decrements address while streaming (address wrap from 0×7fff to 0×0000) |                          |

|                    |                         |           |             | 1: ascend-increments address while streaming (address wrap from 0×0000 to 0×7fff)  |                          |

|                    |                         | 4         | Reserved    | Reserved for factory use                                                           |                          |

|                    |                         | 3:00      | Reserved    | Reserved for factory use                                                           |                          |

(1) This register is not reset by SOFT\_RESET.

(2) This register does not require update (address 0×0F).

Register name: interface configuration 1-address 0×01

| Register Name      | Address | Bit      | Name                        | Function                              |   |  |   |   |          |           |

|--------------------|---------|----------|-----------------------------|---------------------------------------|---|--|---|---|----------|-----------|

|                    |         |          |                             | Single instruction enable             |   |  |   |   |          |           |

|                    |         | 7        | SINGLE-INSTR                | 0: streaming mode (default)           |   |  |   |   |          |           |

|                    |         |          |                             | 1: single instruction                 |   |  |   |   |          |           |

|                    | 6       | Reserved | Reserved for factory use    |                                       |   |  |   |   |          |           |

|                    |         |          | Read Back                   |                                       |   |  |   |   |          |           |

|                    |         | 5        | 5 READBACK 0: DAC read back | 0: DAC read back from active register |   |  |   |   |          |           |

| Interface Config 1 | 0×01    | 3        | 3                           | 3                                     | 3 |  | ] | 3 | READBACK | (default) |

|                    |         |          |                             | 1: DAC read back from buffer register |   |  |   |   |          |           |

|                    |         | 4        | Reserved                    | Reserved for factory use              |   |  |   |   |          |           |

|                    |         | 3        | Reserved                    | Reserved for factory use              |   |  |   |   |          |           |

|                    |         | 2        | Reserved                    | Reserved for factory use              |   |  |   |   |          |           |

|                    |         | 1        | Reserved                    | Reserved for factory use              |   |  |   |   |          |           |

|                    |         | 0        | Reserved                    | Reserved for factory use              |   |  |   |   |          |           |

(1) This register is not reset by SOFT\_RESET.

(2) This register does not require update (address 0×0F).

www.3peak.com 19 / 50 BA20241205A12

Register name: device configuration-address 0×02

| Register Name | Address | Bit  | Name       | Function                                                                                                                                                                 |

|---------------|---------|------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |         | 7:02 | Reserved   | Reserved for factory use                                                                                                                                                 |

| Device Config | 0×02    | 1:00 | POWER-MODE | Mode: 00: normal opertion-full power and full performance 11: sleep-lowest power, non-operational except SPI One time overwrite of the power-enable register (0×B2-0×B6) |

Device identification: Address 0×03-0×0D Register name: chip type-address 0×03

| Register Name | Address | Bit  | Name      | Function                                                       |

|---------------|---------|------|-----------|----------------------------------------------------------------|

|               |         | 7:04 | Reserved  | Reserved for factory use                                       |

| Chip Type     | 0×03    | 3:00 | CHIP-TYPE | Identifies the device as a precison analog monitor and control |

Register name: chip ID low byte-address 0×04

| Register Name    | Address | Bit  | Name       | Function          |

|------------------|---------|------|------------|-------------------|

| Chip ID Low Byte | 0×04    | 7:00 | CHIPID-LOW | Chip ID. Low byte |

Register name: chip ID high byte-address 0×05

| Register Name     | Address | Bit  | Name        | Function           |

|-------------------|---------|------|-------------|--------------------|

| Chip ID High Byte | 0×05    | 7:00 | CHIPID-HIGH | Chip ID. High byte |

Register name: version ID-address 0×06

| Register Name | Address | Bit  | Name      | Function   |

|---------------|---------|------|-----------|------------|

| Version ID    | 0×06    | 7:00 | VERSIONID | Version ID |

Register name: manufacture ID low byte-address 0×0C

| Register Name      | Address | Bit  | Name         | Function                 |

|--------------------|---------|------|--------------|--------------------------|

| Manufacture ID Low | 0×0C    | 7:00 | VENDORID-LOW | Manufacture ID. Low byte |

| Byte               |         |      |              | •                        |

Register name: manufacture ID high byte-address 0×0D

| Register Name               | Address | Bit  | Name          | Function                  |

|-----------------------------|---------|------|---------------|---------------------------|

| Manufacture ID High<br>Byte | 0×0D    | 7:00 | VENDORID-HIGH | Manufacture ID. High byte |

www.3peak.com 20 / 50 BA20241205A12

Register update (buffered register): Address 0×0F

Register name: register update-address 0×0F (self clearing)

| Register Name   | Address | Bit  | Name        | Function                                                                           |

|-----------------|---------|------|-------------|------------------------------------------------------------------------------------|

|                 |         | 7:06 | Reserved    | Reserved for factory use                                                           |

| Register Update |         | 5    | TEMP-UPDATE | When set transfers the latest temperature conversion data to the LT data register. |

|                 | 0×0F    | 4    | ADC-UPDATE  | When set transfers the latest ADC conversion data to the ADC data registers.       |

|                 |         |      |             | This function is needed when operating the ADC in autocycle mode.                  |

|                 |         | 3:01 | Reserved    | Reserved for factory use                                                           |

|                 |         |      |             | Update (self clearing)                                                             |

|                 |         |      |             | 0: disabled                                                                        |

|                 |         | 0    | DAC-UPDATE  | 1: enabled-transfers data from buffers to active registers (DAC register only)     |

|                 |         |      |             | Reserved for factory use                                                           |

www.3peak.com 21 / 50 BA20241205A12

General device configuration: Address 0×310-0×317

Register name: ADC configuration-address 0×10 (R/W)

| Register Name | Address | Bit   | Name                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                          | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                 |

|---------------|---------|-------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

|               |         |       |                                                   | ADC conversion mode Bit. This bit selects the ADC conversion mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                 |

|               |         |       |                                                   | in the seques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ADC channentially on time                                                                                                                                | el registers and the control of the | outs specified<br>are converted<br>se set of<br>ADC is idle and |

|               | 7       | CMODE | in the assequence converte returns process 0×0F r | ADC channer of the contially and resistance of the first as. The ADC must be use the conversion of the | els registers epeatedly. We have the Archannel and current but to initiate to                                                                            | are converted when one set of ADC multiplexer d repeats the it in register the transfer of ne ADC Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                 |